Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

221 - 240 / 732

接合電極構造およびその製造方法ならびにターゲット材

【課題】 パターン加工性が良好でかつその材料コストや製造コストの低廉化が可能な銅合金を用いて電極を形成することを可能とし、かつその電極と半導体層との良好なオーミックコンタクト特性を確保することを可能とする接合電極構造、およびその製造方法ならびにそれに用いられるターゲット材を提供する。

【解決手段】 本発明の実施の形態に係る接合電極構造10は、アモルファスシリコン(a−Si)からなる半導体層1上に、銅(Cu)合金からなる電極2が設けられた接合電極構造10であって、半導体層1と電極2との界面に、その界面付近の半導体層1自体や電極2自体の熱拡散領域からなるオーミックコンタクト層3を備えている。

(もっと読む)

スパッタリングターゲット及び透明導電膜及び透明導電ガラス基板

【課題】 特定の金属を含有する透明導電材料を画素電極、透明電極に使用することにより、バリヤーメタル等を堆積するための工程が不要な簡略化されたTFT(薄膜トランジスタ)基板の製造方法を提供することである。

【解決手段】 酸化インジウムを主成分とし、W、Mo、Nb、Ni、Pt、Pdからなる第1金属群M1から選ばれた1種又は2種以上の金属又はその金属の酸化物と、ランタノイド系金属からなる第2金属群M2から選ばれた1種又は2種以上の金属の酸化物と、を含むスパッタリングターゲットを利用して、透明導電膜を作製する。この透明導電膜を画素電極として利用することによって、ソース電極7等との接触抵抗を小さく抑えることができる。更に、バリヤーメタル等を用いる必要がなくなったため、バリヤーメタル等を堆積する工程をなくすことができ、TFT基板の製造工程が簡略化される。

(もっと読む)

現像液耐性に優れた表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ現像液耐性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で透明導電膜と直接接続されるAl合金膜であって、上記Al合金膜は、グループAに属するNiおよび/またはCoの元素を2.0原子%以下(0原子%を含まない)、並びにグループBに属する少なくとも一種の元素を0.05〜2.5原子%含み、上記グループBの元素はGd、Nd、La、Y、Sc、Pr、Dy、Ce、Ho、Er、Tb、Pm、Tm、Yb、Lu、Hf、Zr、Zn、Mg、Ti、Mn、およびGeから構成されている。

(もっと読む)

表示装置およびこれに用いるCu合金膜

【課題】Cu系材料の特徴である低電気抵抗を維持しつつ、絶縁膜を構成するSiN膜や半導体膜におけるSiN層との密着性に優れると共に、エッチング時に良好にテーパ状にエッチングできるCu合金膜を提供する。

【解決手段】絶縁膜および/または半導体膜と直接接触する表示装置用Cu合金膜であって、該Cu合金膜は、上記SiN膜やSiN層と直接接触する第一層と、該第一層上に形成される第二層とを含み、前記第一層は、窒素を0.4原子%以上5.0原子%未満含むと共に、Ni、Al、Zn、MnおよびFeよりなる群から選択される1種以上の元素(X元素)を0.1〜0.5原子%、および/または、Ge、Hf、Nb、MoおよびWよりなる群から選択される1種以上の元素(Z元素)を0.1〜0.3原子%含み、かつ前記第一層の膜厚が2〜100nmである表示装置用Cu合金膜。

(もっと読む)

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

表示デバイスおよびその製法

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供する。

【解決手段】基板上に配置された薄膜トランジスタと、透明電極によって形成された透明導電膜、および、これら薄膜トランジスタと透明導電膜を電気的に接続するアルミニウム合金膜を有し、該アルミニウム合金膜と前記透明導電膜の界面には該アルミニウム合金の酸化皮膜が形成されており、該酸化皮膜の膜厚が1〜10nmで、該酸化皮膜中の酸素含有量が44原子%以下である表示デバイスとその製法を開示する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

表示装置およびこれに用いるCu合金膜

【課題】Cu系材料の特徴である低電気抵抗を維持しつつ、ガラス基板との密着性に優れると共に、エッチング時にアンダーカットを生じることなく良好にテーパ状にエッチングできるCu合金膜を提供する。

【解決手段】ガラス基板と直接接触する表示装置用Cu合金膜であって、該Cu合金膜は、該基板と直接接触する第一層と該第一層上に形成される第二層とを含み、前記第一層が、窒素を0.4原子%以上5.0原子%未満含むと共に、Ni、Al、Zn、MnおよびFeよりなる群から選択される1種以上の元素(X元素)を0.1原子%以上0.5原子%以下、および/または、Ge、Hf、Nb、MoおよびWよりなる群から選択される1種以上の元素(Z元素)を0.1原子%以上0.3原子%以下含むものであり、かつ前記第一層の膜厚が2nm以上100nm以下であることを特徴とする表示装置用Cu合金膜。

(もっと読む)

グラフェンと金属電極との電気的接合デバイス、それを用いた電子デバイス,電子集積回路及び光/電子集積回路

【課題】グラフェンと金属電極との間の接触抵抗を低減する。

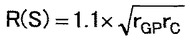

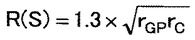

【解決手段】グラフェンの単位面積あたりの電気抵抗をrGP[Ω/μm2]、グラフェンと金属電極との単位面積当たりの界面抵抗をrC[Ωμm2]とすると、接触面積をSとして、接触抵抗は

と計算できる。rGPを10Ω/μm2、rCを10Ωμm2とした場合の計算結果を示し、接触面積を

にすることにより、接触抵抗を収束値の10%増し、あるいは30%増しの値にまで、低減することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】絶縁表面上にゲート電極と、酸化シリコンを含む酸化物半導体層と、ゲート電極と酸化物半導体層の間に絶縁層と、酸化シリコンを含む酸化物半導体層とソース電極層またはドレイン電極層との間にソース領域またはドレイン領域とを有し、ソース領域またはドレイン領域は、縮退した酸化物半導体材料または酸窒化物材料を用いる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】本発明は、エッチングプロセスを簡略化して、半導体層18を薄く形成することを目的とする。

【解決手段】ゲート電極14を形成する。ゲート電極14を覆うようにゲート絶縁膜16を形成する。ゲート絶縁膜16上の少なくともゲート電極14と重なる領域に半導体層18を形成する。半導体層18の第1領域20及び第2領域22に挟まれる第3領域24上にチャネル保護膜26を形成する。第1領域20及び第2領域22並びにチャネル保護膜26に対して、ドーパントを含有するガスによるプラズマ処理を行って、第1領域20及び第2領域22の表層28の不純物濃度を高める。プラズマ処理が行われた第1領域20及び第2領域22の表層28上に、それぞれ、ソース電極32及びドレイン電極34を形成する。

(もっと読む)

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純CuまたはCu合金のCu系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてCu系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純CuまたはCu合金のCu系合金膜とを備えた配線構造であって、前記半導体層と前記Cu系合金膜との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F、O)層を構成する窒素、炭素、フッ素、および酸素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

表示装置用Al合金膜、薄膜トランジスタ基板および表示装置

【課題】Al合金膜とTFTの半導体層との間のバリアメタル層を省略可能な新規のSiダイレクトコンタクト技術を提供する。詳細には、Al合金膜をTFTの半導体層と直接接続しても、AlとSiの相互拡散を防止でき、良好なTFT特性が得られると共に、TFTの製造工程でAl合金膜に約100〜300℃の熱履歴が加わった場合でも、低い電気抵抗と優れた耐熱性が得られる新規なSiダイレクトコンタクト技術を提供する。

【解決手段】本発明の表示装置用Al合金膜は、表示装置の基板上で、薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、上記Al合金膜は、Geを0.1〜4原子%;La、GdおよびNdよりなる群から選ばれる少なくとも1種を0.1〜1原子%;並びにTa、Nb、Re、ZrおよびTiよりなる群から選ばれる少なくとも1種を含有する。

(もっと読む)

半導体装置

【課題】ゲート配線として耐熱性の導電性材料であるタングステン層を用いた場合に、タングステン層の比抵抗を低くすることによって、配線抵抗を十分に低減することを目的とする。

【解決手段】半導体層と、ゲート配線と、前記半導体層と前記ゲート配線との間に挟まれたゲート絶縁層とを有し、前記ゲート配線はタングステン層を有し、前記タングステン層中の酸素濃度を30ppm以下とすることによって、配線抵抗を十分に低減することができる。

(もっと読む)

半導体装置

【課題】配線抵抗の低い半導体装置を提供すること、透過率の高い半導体装置を提供すること、または開口率の高い半導体装置を提供することを課題とする。

【解決手段】ゲート電極、半導体層、ソース電極又はドレイン電極を透光性を有する材料を用いて形成し、ゲート配線又はソース配線等の配線を透光性を有する材料より抵抗率が低い材料で設ける。また、ソース配線及び/又はゲート配線を、透光性を有する材料と当該透光性を有する材料より抵抗率が低い材料を積層させて設ける。これにより、配線抵抗が低く、透過率の高い半導体装置を提供することができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。

【解決手段】半導体層を酸化物半導体層とする逆スタガ型薄膜トランジスタを含む半導体装置において、酸化物半導体層上にバッファ層を有する。バッファ層は、半導体層のチャネル形成領域と、ソース電極層及びドレイン電極層とに接する。バッファ層は膜内に抵抗分布を有し、半導体層のチャネル形成領域上に設けられる領域の電気伝導度は半導体層のチャネル形成領域の電気伝導度より低く、ソース電極層及びドレイン電極層と接する領域の電気伝導度は半導体層のチャネル形成領域の電気伝導度より高い。

(もっと読む)

電界効果トランジスタ

【課題】従来の光学素子に電界効果トランジスタを適用するとき、PN接合部の光リークを抑えるために、トランジスタの周囲に遮光領域を設定する必要が有り、回路面積が大きくなるという課題があった。また、反射光に対して遮光性が十分でないという問題があった。

【解決手段】本発明の電界効果トランジスタは、ゲート電極上に、PN接合部に平面的に重なるように遮光部材を有する。この遮光部材により、PN接合部を遮光することができる。また、電界効果トランジスタ面積が増大しないため、回路の面積を小さく設定できる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】低抵抗なAl配線材料を用いて、生産コストの低下および生産性の向上を図ることができる薄膜トランジスタの製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、Arガスを用いたスパッタリングによって純AlまたはAl合金を第1層として成膜する工程と、前記第1層の上層に、Ar+N2混合ガスまたはAr+NH3混合ガスを用いたスパッタリングによって、前記第1層の材料に加えて窒化アルミニウムも部分的に含む第2層を成膜する工程と、別途形成するコンタクトホールを介して透明膜電極と第1電極の前記第2層とを電気的に接続する工程を含むものである。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

221 - 240 / 732

[ Back to top ]