Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

201 - 220 / 732

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に画素と駆動回路が設けられ、駆動回路の第1の薄膜トランジスタ及び画素の第2の薄膜トランジスタは、ゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、ゲート絶縁層、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸化物半導体層の一部と接する酸化物絶縁層と、を有し、第2の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、及び酸化物絶縁層は透光性を有し、第1の薄膜トランジスタのソース電極層及びドレイン電極層は、第2の薄膜トランジスタのソース電極層及びドレイン電極層と材料が異なり、第2の薄膜トランジスタのソース電極層及びドレイン電極層よりも低抵抗である。

(もっと読む)

薄膜トランジスタ

【課題】本発明は、薄膜トランジスタに関する。

【解決手段】本発明の薄膜トランジスタは、ソース電極と、前記ソース電極と分離して設置されるドレイン電極と、半導体層と、絶縁層と、ゲート電極を含む。前記半導体層が、前記ソース電極と、前記ドレイン電極とに電気的に接続され、前記ゲート電極が、前記絶縁層により、前記半導体層と、前記ソース電極と、前記ドレイン電極と絶縁状態で設置され、前記ソース電極と、ドレイン電極と、ゲート電極とは、それぞれカーボンナノチューブ―金属複合材料体からなる。前記カーボンナノチューブ―金属複合材料体は、カーボンナノチューブ構造体と、前記カーボンナノチューブ構造体に被覆された金属層とを含む。前記カーボンナノチューブ構造体は、複数のカーボンナノチューブのみからなる。

(もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法

【課題】単純化された工程を通じて表示能力が優れた薄膜トランジスタ基板を製造する方法に関する。

【解決手段】画面表示部と周辺部とを含む基板の上にゲート配線をITOまたはIZOとの接触特性が良好な下部金属膜と低抵抗上部金属膜との二重膜構造で形成し、ゲート絶縁膜、半導体層、接触層を連続蒸着する。次いで、二重膜構造のデータ配線及びその下部の接触層パターンを形成する。保護膜を蒸着した後、その上に感光膜を塗布し、その次、画面表示部の透過率と周辺部の透過率とが異なる一つ以上のマスクを用いて感光膜を露光・現像して部分に応じて厚さが異なる感光膜パターンを形成する。このような感光膜パターンを通じて保護膜及びその下部の膜をエッチングして半導体パターン及び接触窓を形成し、その上にITOまたはIZOで画素電極と補助ゲートパッド及び補助データパッドを形成する。

(もっと読む)

電界効果型トランジスタ

【課題】チャネル領域を構成する有機半導体材料層と良好なオーミック・コンタクトを形成することができるソース/ドレイン電極を備えた電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタは、ゲート電極12と、ゲート絶縁層13と、ソース/ドレイン電極21と、チャネル領域15を構成する有機半導体材料層14とを備え、ソース/ドレイン電極21は、金属から成る導体部22、及び、導体部22を少なくとも部分的に被覆し、不純物がドーピングされた有機導電材料層23から成り、有機導電材料層23を介して、チャネル領域15と導体部22との間の電気的接続が形成される。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】IGZO層とITO層とを電気的に接続する場合には、易加工性を備え電気抵抗率が低いアルミ等の金属と高融点金属としてのチタン等との積層構造を用いる必要があるが、積層構造を形成する場合、複数の金属層を形成する必要がある。そのため製造工程が増えると共に、パーティクル等の発生確率が増え、歩留まりを落とすという課題がある。

【解決手段】ITO等の金属酸化物を用いた画素電極2aが、層間絶縁層9に形成されたコンタクトホール9aを介してIGZO層を用いた配線層7aと電気的に接続している。画素電極2aとAl−Nd合金を用いた上電極6cと直接接触させた場合、コンタクト抵抗が高くなるが、配線層7aにIGZO層を用い、画素電極2aにITO等の第2金属酸化物配線層を用いた場合、互いの構造が類似していることから、密接させるだけで接触抵抗の増大を招くことなく電気的に導通を取ることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

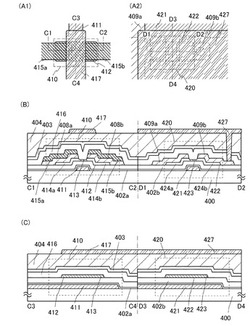

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置

【課題】オン抵抗、出力容量を低減した半導体装置を提供する。

【解決手段】絶縁層2の上に互いに接して設けられた、第2導電型の第1の半導体層34、前記第1の半導体層よりも不純物濃度の低い第2導電型の第2の半導体層33、第1導電型の第3の半導体層31、前記第3の半導体層よりも不純物濃度の高い第1導電型の第4の半導体層32、前記第4の半導体層の表面に設けられた第2導電型の第5の半導体層35と、前記第2の半導体層と前記第3の半導体層との境界の上に設けられたトレンチ溝51と、前記トレンチ溝内及び前記トレンチ溝外の前記第2,第3,第4の半導体層の上に絶縁膜42を介して設けられた制御電極23と、前記第1の半導体層の上に設けられた第1の主電極21と、前記第4,第5の半導体層の上に前記制御電極と離隔して設けられた第2の主電極22と、を備える半導体装置。

(もっと読む)

表示装置用Al合金膜、表示装置およびAl合金スパッタリングターゲット

【課題】バリアメタル層を省略して透明画素電極と直接接続させた場合にも低コンタクト抵抗を示し、且つ、表示装置の製造過程における現像液耐食性や剥離液耐食性も高められた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、Al合金膜は、グループAに属するNiおよび/またはCoの元素を0.5原子%以下(0原子%を含まない。)と、Geを0.2〜2.0原子%と、グループBに属するYおよび/またはZrの元素を3原子%以下(0原子%を含まない。)とを含有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 高速動作が可能な半導体装置を提供する。

【解決手段】 半導体基板上の絶縁層上に形成された半導体層と、ゲート絶縁膜を介して前記半導体層上に配置されたゲート電極と、前記ゲート絶縁膜及びゲート電極の側壁に沿うように形成された側壁絶縁膜と、前記絶縁層に底面が接する合金層を含んで構成されたソース/ドレイン層と、 前記合金層と前記半導体層との界面に自己整合的に偏析され、前記半導体層の結晶方位面に沿ってチャネル領域に対する接合面が形成された不純物導入層とを有する半導体装置を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネル形成領域として酸化物半導体層を用いる薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体層を窒素雰囲気下で加熱して低抵抗化し、低抵抗な酸化物半導体層を形成する。また、低抵抗な酸化物半導体層においてゲート電極層と重なる領域を選択的に高抵抗化して高抵抗な酸化物半導体領域を形成する。酸化物半導体層の高抵抗化は、該酸化物半導体層に接して、スパッタ法により酸化珪素を形成することによって行う。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に、酸化物半導体層より導電率の高いバッファ層を形成し、該バッファ層の上にソース電極層及びドレイン電極層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

トランジスタを有するトランジスタ基板及びトランジスタを有するトランジスタ基板の製造方法

【課題】微結晶シリコンをチャンネル領域として用い、コンタクト歩留まりを向上させ、良好な特性を備えるトランジスタを有するトランジスタ基板及びその製造方法を提供する。

【解決手段】トランジスタ100は、基板11と、ゲート電極112と、ゲート絶縁膜113と、第1の半導体層114と、第2の半導体層115と、ストッパ膜116と、オーミックコンタクト層117、118と、ドレイン電極119と、ソース電極120と、を備える。微結晶シリコンを用いた第1の半導体層114上に第2の半導体層115を積層させた上で、第1の半導体層114及び第2の半導体層115の側面でオーミックコンタクト層117、118とコンタクトを取ることにより、コンタクト歩留まりを向上させ、良好な特性を備えるトランジスタを有するトランジスタ基板及びその製造方法を提供することができる。

(もっと読む)

配線層構造及びその製造方法

【課題】半導体基板又はガラス基板の下地基板に対する密着性が高く、下地基板への拡散バリア性に優れ、かつ水素プラズマ耐性に優れた低抵抗な配線層構造、及びその製造方法を提供する。

【解決手段】半導体又はガラス基板の下地基板1と、下地基板1上に形成された酸素含有Cu合金層2と、酸素含有Cu合金層2上に形成された、Al、Zr、Tiのうち少なくとも一種を含有する酸化物層3と、酸化物層3上に形成された、Al、Zr、Tiのうち少なくとも一種を含有するCu合金層4と、Cu合金層4上に形成された、Cu導電層5とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】高開口率な表示装置を提供する。

【解決手段】薄膜トランジスタと、保持容量とが設けられた画素と、走査線と、走査線に直交して設けられた信号線と、を有し、走査線の上方には、薄膜トランジスタのソース領域、ドレイン領域、及びチャネル形成領域が形成される部分と保持容量の下部電極となる部分とを有する半導体膜が設けられ、半導体膜上には絶縁膜が設けられ、半導体膜のチャネル形成領域となる部分の上方には、絶縁膜を介して走査線と電気的に接続されたゲート電極が設けられ、半導体膜の下部電極となる部分の上方には、絶縁膜を介して保持容量の上部電極が設けられ、半導体膜は、基板に平行であり、ゲート電極は、保持容量の上部電極より半導体膜を基準に高い場所に設けられ、ゲート電極及び上部電極の上方には、信号線が設けられている表示装置。

(もっと読む)

酸化物薄膜トランジスタ及びその製造方法

【課題】素子の劣化及び均一度の低下を防止する酸化物薄膜トランジスタ及びその製造方法を提供する。

【解決手段】酸化物薄膜トランジスタの製造方法は、基板110上にゲート電極121を形成する段階と、基板110上にゲート絶縁膜115を形成する段階と、ゲート絶縁膜115上にチャネル領域の側面にテーパを有する1次アクティブ層124aを形成し、1次アクティブ層124a上にソース/ドレイン電極を形成する段階と、ソース/ドレイン電極122、123の上部に、非晶質酸化亜鉛系半導体からなる2次アクティブ層124bを、1次アクティブ層124aのテーパと接触するように形成する段階とを含み、1次アクティブ層124aは、ソース/ドレイン電極122、123のウェットエッチング中に低い選択比でエッチングされることにより、側面にテーパが形成される。

(もっと読む)

半導体素子の接触部及びその製造方法並びに表示装置用薄膜トランジスタ表示板及びその製造方法

【課題】比抵抗が低いながらも接触特性が良い接触部を含み、優れた接触特性を有する接触部を含む薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】絶縁基板と、ゲート線と、ゲート絶縁層と、半導体層と、データ線と、前記データ線と分離されているドレーン電極と、前記半導体層を覆っていて前記ドレーン電極を露出する第1接触孔、前記ゲート線の一部を露出する第2接触孔、前記データ線の一部を露出する第3接触孔を有する保護膜と、前記第1接触孔を通じて前記ドレーン電極と連結される画素電極と、前記第2接触孔を通じて前記ゲート線と連結されているゲート接触補助部材と、前記第3接触孔を通じて前記データ線に連結されるデータ接触補助部材とを含み、前記データ接触補助部材は凹凸を有することを特徴とする薄膜トランジスタ表示板を提供する。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、および電子機器

【課題】ソース・ドレイン−有機半導体層間のコンタクト抵抗および配線抵抗を低く抑えて特性の向上を図りつつも、有機半導体層の膜剥がれを防止して信頼性の向上を図ることが可能な薄膜トランジスタを提供する。

【解決手段】対向配置される電極部17s(P),17d(P)と、これらから引き出された配線部17s(L),17d(L)とで構成されたソース17s・ドレイン17dと、ソース17s・ドレイン17dの電極部17s(P),17d(P)上に積層させた状態で、電極部17s(P)−17d(P)間にわたって設けられた有機半導体層19とを備えている。そしてソース17s・ドレイン17dは、電極部17s(P),17d(P)と配線部17s(L),17d(L)とが同一の層を用いて構成される。さらに少なくとも互いに対向配置される電極部17s(P),17d(P)の縁部が、配線部17s(L),17d(L)よりも薄膜化されている。

(もっと読む)

201 - 220 / 732

[ Back to top ]