Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

121 - 140 / 732

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電界効果移動度が大きい酸化物半導体層を用いた半導体装置の作製方法を提供することを課題の一つとする。また、高速動作可能な半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化物半導体層をハロゲン元素により終端化させて、酸化物半導体層と、酸化物半導体層と接する導電層のコンタクト抵抗の増大を抑制することで、酸化物半導体層と導電層のコンタクト抵抗が良好になり、電界効果移動度が高いトランジスタを作製することができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

トランジスタ及びその製造方法。

【課題】活性層中への電極材の拡散の抑制、電極材の低電気抵抗化、さらには活性層へのダメージ低減を図ることができる、酸化物半導体からなる活性層を有する電界効果型トランジスタ及びその製造方法を提供すること。

【解決手段】本発明の一実施形態に係るトランジスタは、酸化物半導体からなる活性層と、Ti系材料またはMo系材料からなる第1の電極層と、第1の電極層の材料よりも比抵抗の小さい材料からなる第2の電極層とを具備する。

上記構成によれば、酸化物半導体からなる活性層に対する拡散が小さい第1の電極層と、比抵抗が小さい第2の電極層を積層することにより、活性層と電極層の層界面でのFET特性が良好であり、電気抵抗の小さい電極を備えたFETを得ることが可能である。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

成膜方法及び薄膜トランジスタの作製方法

【課題】3層以上の膜を成膜するに際して、第1の膜の成分が第3の膜に含まれることを防ぐ成膜方法を提供する。

【解決手段】上部電極104と下部電極102が設けられた成膜装置100により3層以上の膜を成膜する多層膜の成膜に際して、下部電極102上に基板110を配して第1の膜112を成膜し、前記第1の膜112の形成時よりも上部電極104と前記基板110の間の距離を長くし、前記第1の膜112上に第2の膜114を成膜し、前記第2の膜114の形成時よりも前記上部電極104と前記基板110の間の前記距離を短くし、前記第2の膜114上に第3の膜116を成膜する。

(もっと読む)

半導体装置、光学装置及びセンサ装置

【課題】ソース電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧および信頼性が高い電界効果トランジスタを提供する。

【解決手段】基板1上に形成されたキャリア走行層3と、前記キャリア走行層上に形成され前記キャリア走行層よりもバンドギャップエネルギーが高いキャリア供給層4a、4bと、前記キャリア供給層から前記キャリア走行層の表面または内部に到る深さまで形成されたリセス部5と、前記キャリア供給層上に形成されたドレイン電極11と、前記リセス部に形成され、前記ドレイン電極側のキャリア供給層と重畳するように延設したゲート電極7と、前記リセス部の底面と前記ゲート電極との間に形成された第1絶縁膜6と、前記ゲート電極と前記ドレイン電極側のキャリア供給層との間に形成され前記第1絶縁膜よりも誘電率が高い第2絶縁膜8aとを備える。

(もっと読む)

半導体装置

【課題】大画面化しても低消費電力、歩留まり及び信頼性の向上を実現するための半導体

装置の構造及びその作製方法を提供する。

【解決手段】画面で使われる画素薄膜トランジスタを逆スタガ型薄膜トランジスタで作製

する。その逆スタガ型薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上

に作製する。また、ソース配線と逆スタガ型薄膜トランジスタ、画素電極と逆スタガ型薄

膜トランジスタをつなぐ金属配線を同一工程で作製する。

(もっと読む)

半導体装置とその製造方法

【課題】良好な特性を有し且つ微細化を実現した半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、平面状シリコン層212上の柱状シリコン層208、柱状シリコン層208の底部領域に形成された第1のn+型シリコン層113、柱状シリコン層208の上部領域に形成された第2のn+型シリコン層144、第1及び第2のn+型シリコン層113,144の間のチャネル領域の周囲に形成されたゲート絶縁膜140、ゲート絶縁膜140の周囲に形成され第1の金属シリコン化合物層159aを有するゲート電極210、ゲート電極210と平面状シリコン層212の間に形成された絶縁膜129a、柱状シリコン層208の上部側壁に形成された絶縁膜サイドウォール223、平面状シリコン層212に形成された第2の金属シリコン化合物層160、及び第2のn+型シリコン層144上に形成されたコンタクト216を備える。

(もっと読む)

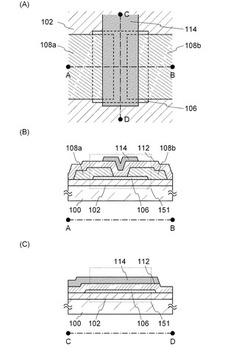

面エピ形状とソース/ドレインの部分的に覆われるシリサイド周辺とに関するフィンフェット

【課題】低い寄生抵抗(例えば、Rpara)および/または高い駆動電流の改善された特性を有するフィンフェットを提供する。

【解決手段】フィンフェット100およびフィンフェットの製造方法が提供される。フィンフェットは、半導体基板106上に、2つまたは複数のフィン102,104と、前記フィンの側面に設けられるエピタキシャル層108,110と、前記エピタキシャル層の表面上を覆うように設けられる金属−半導体化合物112,114とを備える。フィンは、前記半導体基板の表面上に対して実質的に垂直な側面を有する。前記エピタキシャル層は、前記フィンの側面に対して斜角を有して延設される表面を有する。フィンフェットは、前記金属−半導体化合物上に設けられるコンタクト116を含み得る。

(もっと読む)

有機FET

【課題】有機FETにおいて、電極から活性層へのキャリア注入効率を向上させること。

【解決手段】有機半導体層3とソース電極5および有機半導体層3とドレイン電極6との間に、電極表面との密着性が良好な界面層4を挿入することで、キャリア注入効率が向上する。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

表示装置用Al合金膜

【課題】シリコン半導体層および/または透明導電膜との間のバリアメタル層を省略しても、AlとSiの相互拡散を抑制でき、低抵抗のオーミック特性を有する電気的接触が得られると共に、十分な耐熱性を有する表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜および/または薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、Al合金膜は、30原子%以上のMoを含有するAl−Mo合金、またはMoと、Mn、Nd、Ni、Mg、およびFeよりなるX群から選択される少なくとも1種とを含有するAl−Mo−X合金の単層から構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

薄膜トランジスタおよびその製造方法、並びに表示装置

【課題】セルフアライン構造の薄膜トランジスタの特性を安定させることが可能な薄膜トランジスタおよびその製造方法、並びに表示装置を提供する。

【解決手段】酸化物半導体膜20のチャネル領域20A上にゲート絶縁膜30およびゲート電極40をこの順に同一形状で形成する。酸化物半導体膜20,ゲート絶縁膜30およびゲート電極40の上に金属膜を形成し、この金属膜に対して熱処理を行うことにより、金属膜を酸化させて高抵抗膜50を形成すると共に、ソース領域20Sおよびドレイン領域20Dの上面から深さ方向における少なくとも一部に低抵抗領域21を形成する。低抵抗領域21は、アルミニウム(Al)等をドーパントとして含むか、またはチャネル領域20Aよりも酸素濃度が低いことにより低抵抗化されている。変動要素の多いプラズマ処理を用いずに高抵抗領域21を形成可能となり、安定した特性が得られる。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

電界効果トランジスタ、およびその製造方法

【課題】高い移動度、低いオン抵抗を備えたノーマリオフ型の電界効果トランジスタを提供する。

【解決手段】III族窒化物系化合物半導体からなるチャネル層104と、前記チャネル層上に形成されたAlInGaNからなる界面層106と、前記界面層上に形成され、前記界面層に達するリセス部を備えたIII族窒化物系化合物半導体からなる電子供給層108と、前記リセス部を挟んで、前記電子供給層108上に形成されたソース電極110およびドレイン電極112と、前記リセス部の内表面に形成された絶縁膜120と、前記絶縁膜上に形成されたゲート電極114とを備える。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 ソース/ドレイン電極と活性層との間に微結晶半導体からなるコンタクト層を設ける構成の薄膜トランジスタにおいて、直接堆積法によって形成されるコンタクト層の表面に凹凸ができ、凹部の膜厚が薄くなるためにオフリーク電流が生じ、電気特性が低下する。コンタクト層の凹部がオフリーク電流を抑制するのに必要な膜厚となるまで形成すると、コンタクト層表面の凹凸を活性層5で覆うことのできない部分が生じ、オン電流が流れる際の抵抗となる。

【解決手段】 コンタクト層4の凹部が、オフリーク電流を抑制するのに十分な膜厚になるまで形成した後、その表面を平坦化処理して活性層を形成する。これにより、コンタクト層4の表面を活性層5でほぼ均一に覆うことができ、オフリーク電流が低減され、オン電流の大きい特性のTFTを得ることができる。

(もっと読む)

121 - 140 / 732

[ Back to top ]