Fターム[5F110AA25]の内容

Fターム[5F110AA25]に分類される特許

1 - 20 / 22

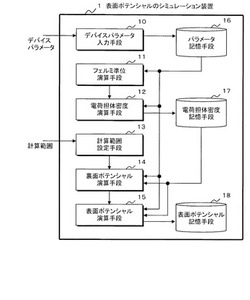

表面ポテンシャルのシミュレーション装置及び表面ポテンシャルのシミュレーションプログラム

【課題】半導体膜中にキャリアを捕獲する欠陥を含む蓄積型の電界効果型薄膜トランジスタについて、表面ポテンシャルを高速かつ高精度に計算する。

【解決手段】シミュレーション装置1は、電気的中性条件に基づいて、フラットバンド条件でのフェルミ準位を算出するフェルミ準位演算手段11と、このフェルミ準位を用いてフラットバンド条件での帯電した欠陥の密度を含む電荷担体密度を算出する電荷担体密度演算手段12と、ポアソン方程式から解析的に導出されるポテンシャルとゲート電圧との間の関係式に、半導体膜中の電荷分布が一定として表面及び裏面ポテンシャルを関連付けた近似式を代入して得た方程式に、電荷担体密度算出手段12で算出した電荷担体密度を代入して裏面ポテンシャルを算出する裏面ポテンシャル演算手段14と、裏面ポテンシャルを前記近似式に代入して表面ポテンシャルを算出する表面ポテンシャル演算手段15とを備える。

(もっと読む)

絶縁ゲート電界効果トランジスタのシミュレーション方法、シミュレーション装置および集積回路

【課題】広いレンジのゲート長には適用可能な、絶縁ゲート電界効果トランジスタのシミュレーション方法、シミュレーション装置および当該シミュレーション方法によって設計された集積回路を提供する。

【解決手段】ボディコンタクト142を有するSOI絶縁ゲート電界効果トランジスタ10のソース電流またはドレイン電流を、ゲート−ボディオーバラップ領域160の電流を余剰のゲート幅に流れる電流として考慮に入れて求める際に、余剰のゲート幅のゲート長依存性を考慮にいれてソース電流またはドレイン電流をシミュレーションする。

(もっと読む)

記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能であり、記憶素子を構成するトランジスタをオンすることなく、記憶したデータを高速で読み出すことができる記憶装置を提供する。

【解決手段】記憶装置において、酸化物半導体層をチャネル領域として有するトランジスタ及び保持容量素子を有するメモリセルと、容量素子と、を電気的に接続させてノードを構成し、該ノードは保持容量素子を介した容量結合により保持データに応じて昇圧され、この電位を増幅回路によって読み出すことで、データの識別を行うことができる。

(もっと読む)

半導体装置

【課題】大電力の制御を行う、高耐圧の半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上の、ゲート電極と重畳する酸化物半導体層と、酸化物半導体層と接し、端部をゲート電極と重畳するソース電極及びドレイン電極と、を有し、ゲート電極と酸化物半導体層が重畳する領域において、ゲート絶縁層は、ドレイン電極と端部を重畳する第1の領域と、前記第1の領域と隣接する第2の領域と、を有し、第1の領域の静電容量は第2の領域の静電容量より小さいトランジスタを提供すること。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法、ならびにプログラム

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法、ならびにプログラムを提供する。

【解決手段】本発明は、基板上にゲート電極、ゲート絶縁層、半導体層、ソース電極およびドレイン電極が少なくとも設けられた薄膜トランジスタの製造方法である。ソース電極およびドレイン電極を形成する工程において、基板の歪み、または基板の伸縮率に基づいて、露光データを、スケーリング処理を用いて薄膜トランジスタのチャネル長を固定した状態で補正して第1の補正データを作成する。この第1の補正データに基づいて、ソース電極およびドレイン電極の形成領域にレーザ光を照射し、その形成領域を親液性にする。この形成領域に、ソース電極およびドレイン電極となる液滴を、打滴データに基づいて打滴する。

(もっと読む)

ばらつきを考慮した半導体集積回路の設計方法

【課題】少数の離散的な電荷によって生じるトランジスタ特性のばらつきを考慮した半導体集積回路の設計方法を提供する。

【解決手段】単一の電荷が付加されることにより生じるトランジスタ特性の変位xの確率密度関数P1(x)を決定する工程と、P1(x)と、付加される電荷の個数nの出現確率と、を元に回路設計上想定すべき設計余裕Mを決定する工程と、を備える。単一の電荷が特性に影響を与えるほど微細なトランジスタを有する半導体集積回路においても、正確にばらつきが計算できる。

(もっと読む)

シミュレーション装置、及びシミュレーション方法

【課題】トラップ準位を取り込んだ物理モデルに基づき、比較的短時間で高精度な回路解析を行うことができるシミュレーション装置を提供する。

【解決手段】シミュレーション装置は、入力装置11、記憶装置12、演算装置16、制御装置15及び出力装置17を備える。入力装置から入力されたTFTにおけるゲート電極端に対応する多結晶シリコン薄膜のゲート電極側表面のソース領域端とドレイン領域端における第1、第2イオン化トラップ密度NtS0,NtSL、上記ソース領域端の第1電位φS0、上記ゲート電極が形成された表面に対向する裏面側のソース領域端の第2電位φb0、上記ゲート電極側表面のドレイン領域端の第3電位φSL、及び上記裏面側の前記ドレイン領域端の第4電位φbLに基づいて演算を行ってドレイン電流Idsを算出する。

(もっと読む)

結晶化領域に設けられた薄膜トランジスタの電気特性を求めるシミュレータによりシミュレーションする方法および結晶化領域に設けられた薄膜トランジスタのチャネル領域に含まれるクーロン散乱中心密度を計算及び抽出するための物理解析モデル。

【課題】Poly−Si TFTについてユニバーサルプロットを適用し、移動度を決めている結晶粒界について物理解析するモデルを提供する。

【解決手段】 Poly−Si TFTの移動度μを解析する物理解析モデルを提供するものである。該TFTの移動度μおよびVg−Id特性を測定し、測定された移動度μおよびVg−Id特性からクーロン散乱移動度μ(Coulomb)、フォノン散乱移動度μ(phonon)、そして表面ラフネス散乱μ(surface)の3つの移動度と実効電界Eeffを算出する。実効電界Eeffから自由キャリア密度nを求め、クーロン散乱移動度μ(Coulomb)と自由キャリア密度nとの相関特性を用いてクーロン散乱中心密度N(Coulomb)を求めることを含む物理解析モデル。

(もっと読む)

薄膜トランジスタのソース−ドレイン電流モデリング方法及び装置

【課題】薄膜トランジスタのソース−ドレイン電流モデリング方法及び装置を提供する。

【解決手段】本発明による薄膜トランジスタのソース−ドレイン電流モデリング方法は、標本入力値及び標本出力値を含む標本データを入力される段階と、前記標本データに相応してモデリング変数を調整する段階と、前記調整されたモデリング変数に相応して電流モデル値を計算する段階と、前記計算された電流モデル値と前記標本出力値とを比較した結果値があらかじめ設定された基準値より少ない場合には、前記調整されたモデリング変数を電流モデルに適用して電流モデルをフィッティング(fitting)する段階と、前記フィッティングされた電流モデルに実際入力データを入力する段階と、前記実際入力データに相応して結果値を出力する段階とを含み、前記電流モデルは、薄膜トランジスタのソース−ドレイン電流を予測するモデルである。

(もっと読む)

パワー半導体素子の評価方法および評価装置

【課題】 自己発熱していない状態のパワー半導体素子の電流・電圧特性を、比較的簡易な手法により精度良く得ることのできるパワー半導体素子の評価方法および評価装置を実現する。

【解決手段】 自己発熱状態の評価対象LDMOS4の電流・電圧特性を測定し(S1)、自己発熱していない状態におけるドレイン電流値をId0、S1により測定されたドレイン電流値をId、S1における測定開始時のパワー半導体素子の絶対温度をTo、ドレイン電圧(Vd)を上昇させたときの温度上昇分をΔT、n=1.5〜2とした場合に、次式、Id0=Id×((To+ΔT)/To)nを用いて自己発熱していないときの電流値Id0を求め、評価対象LDMOS4の自己発熱していない状態における電流・電圧特性を演算する(S2)。

(もっと読む)

半導体装置

【課題】MOSFETの高速化と低消費電力化を図る。

【解決手段】CMOSインバータ1のpMOSFET10およびnMOSFET20をそれぞれ、ゲートGへの入力信号Vinの切替えに同期してチャネル領域にバイアス電圧が印加される構造とする。そして、そのバイアス電圧を、容量C1,C2,C3,C4を用いて調整する。それにより、pMOSFET10およびnMOSFET20の各しきい値電圧が、それらのオン・オフに応じて、それぞれ適した値に調整され、オン状態の電流増加による高速化と、オフ状態のリーク電流低減による低消費電力化が可能になる。

(もっと読む)

半導体装置及び当該半導体装置を具備する電子機器

【課題】チャネルドープまたはチャネル領域を微細加工することなく、容易にしきい値電圧の制御が可能なMOSトランジスタを具備する半導体装置を提供することを課題とする。

【解決手段】MOSトランジスタにおいて、ソース領域及びドレイン領域と、ソース領域及びドレイン領域とは逆極性の不純物元素を添加してチャネル領域に隣接して形成した不純物領域と、でPN接合ダイオードを形成する。そして、不純物領域の不純物濃度の範囲は、ソース領域及びドレイン領域と、不純物領域と、がPN接合ダイオードを形成できる濃度範囲で添加されているものとする。

(もっと読む)

電流モデル作成方法および電子回路

【課題】電界効果トランジスタの特性に精度よくフィッティングし、従来のシリコン系の複雑な電流モデル式に比べて簡便な電流モデル作成方法を提供する。

【解決手段】電界効果トランジスタのドレイン電流のシミュレーションに用いられる電流モデルを実測の電流-電圧特性データから求めるための電流モデル作成方法であって、電流モデルは、ドレイン電流の主要部となる第1の電流項、ドレイン電流の立ち上がりに関する第2の電流項、およびリーク電流に関する第3の電流項の3つの電流項の和からなるものである。

(もっと読む)

回路信頼性のシミュレーション方法及びそのシステム

【課題】回路信頼性のシミュレーション方法及びシステムを提供する。

【解決手段】該方法及びシステムは、一定期間動作後の薄膜トランジスタの素子パラメータの変動を演算し、該変動に応じて、回路シミュレーションに回路信頼性解析を追加するために、オペレーションタイミング波形を演算する。これにより、回路のオペレーションをより現実的に評価することができる。

(もっと読む)

トランジスタモデルを用いたシミュレーション方法、及び、トランジスタモデルを用いたシミュレーション方法に基づく、電界効果型トランジスタから成る回路の動作制御方法

【課題】電界効果型トランジスタのチャネル形成領域におけるポテンシャル分布の変化に起因する閾値電圧の変化を反映させて動作解析を行うためのトランジスタモデルを用いたシミュレーション方法を提供する。

【解決手段】電界効果型トランジスタのチャネル形成領域におけるポテンシャル分布の変化に起因する閾値電圧の変化を反映させて動作解析を行うためのトランジスタモデル10を用いたシミュレーション方法であって、

(1)チャネル形成領域におけるポテンシャル分布の変化とチャネル形成領域における局在準位によって捕獲/放出されるキャリアとの関係を反映するように規定された閾値電圧計算用モデル20によって得られる値に基づいて閾値電圧変化量を計算し、

(2)該閾値電圧変化量に基づいて閾値電圧の値を補正し、

(3)該補正された閾値電圧の値に基づいてトランジスタモデル10から成る回路モデルの動作を解析する。

(もっと読む)

シミュレーション装置、シミュレーション方法、及び半導体装置の製造方法

【課題】欠陥準位を取り込んだ物理モデルに基づき、比較的短時間で高精度な回路解析を行うことができるシミュレーション装置を提供する。

【解決手段】入力装置11、記憶装置12、演算装置16、制御装置15及び出力装置17を備えるシミュレーション装置が開示されている。入力装置から入力されたTFTにおけるゲート電極端に対応する多結晶シリコン薄膜のゲート電極側表面のソース領域端の第1電位φS0、多結晶シリコン薄膜におけるゲート電極が形成された表面に対向する裏面側のソース領域端の第2電位φb0、TFTにおけるゲート電極端に対応する多結晶シリコン薄膜のゲート電極側表面のドレイン領域端の第3電位φSL、及び多結晶シリコン薄膜におけるゲート電極が形成された表面に対向する裏面側の前記ドレイン領域端の第4電位φbLに基づいて演算を行ってドレイン電流Idsを算出し、欠陥準位を含めてモデル化する。

(もっと読む)

半導体デバイス特性シミュレーション方法、半導体デバイス特性シミュレーション装置および半導体デバイス特性シミュレーションプログラム

【課題】新規開発デバイスの特性シミュレーションを高い精度で行うこと。

【解決手段】新規開発デバイスと構造や特性が近い既存デバイスモデルを用いてパラメータを補正しながらシミュレーションを行い、シミュレーションによる電極間容量が測定データと同等であると判定されたデバイスモデルに対して、その電流源モデルを測定データに基づいて作成した電流源モデルで入れ替え、電流源モデルを入れ替えたデバイスモデルを用いて特性のシミュレーションを行う。

(もっと読む)

シミュレーション装置、シミュレーション方法、シミュレーションプログラム、記録媒体、及び半導体装置

【課題】理論から一貫してデバイスのIV特性を予測でき、特にナノオーダーサイズの微小デバイスの特性予測に好適に用いることができるシミュレーション装置を提供する。

【解決手段】本発明のシミュレーション装置は、前記デバイスの原子構造モデルを作成する原子構造作成部21と、前記原子構造モデルにおける電子構造計算を実行する電子構造計算部22と、前記電子構造に基づき量子効果及び原子構造を反映させて当該デバイスの第1の電流−電圧特性を算出するIV特性計算部23と、前記計算により得られた第1の電流−電圧特性に対して、電圧補正値による補正処理を実行する補正処理部24と、半古典近似法を用いて第2の電流−電圧特性を計算するIV特性計算部25と、前記第1、第2のIV特性を結合する結合処理部26と、を有する。

(もっと読む)

トランジスタのシミュレーション方法及びシミュレーション装置

【課題】構造的な乱れや不純物の存在による状態密度の変化等の影響を受ける、非晶質トランジスタを、精度よくシミュレーションを行う方法を提供する。

【解決手段】半導体層とゲート絶縁層の界面の蓄積電荷を、半導体層とゲート絶縁層を誘電体とした二層積層構造における電圧印加時の界面の蓄積電荷とみなして求める第1の工程と、前記界面の蓄積電荷を基に、前記ソース電極とドレイン電極の間に流れる電流を求める第2の工程と、前記ソース電極及びドレイン電極から前記半導体層に注入される電荷を求める第3の工程と、前記半導体層に内在する電荷を求める第4の工程と、前記第3及び第4の工程で導出した電荷を基に半導体層の伝導率を求める第5の工程と、前記第2の工程で求めた電流の式に第5の工程で求めた伝導率を導入することによりトランジスタ特性を算出する第6の工程とを有する回路のシミュレーション方法。

(もっと読む)

デバイス計算方法

【課題】 短い時間で計算できるため実践性が高く、かつ、キャリア速度のオーバーシュートを高い精度で計算できるデバイスの計算方法を提供する。

【解決手段】1次元ポアソン方程式に併せて、5つの多重加速流定義をまとめた図8中のすべての式(流速の式と境界条件の式も含む)を用いることによって、半導体デバイス内部の電気的特性並びに電気的特性分布を推定する。

(もっと読む)

1 - 20 / 22

[ Back to top ]