Fターム[5F110BB09]の内容

Fターム[5F110BB09]の下位に属するFターム

イメージセンサ (451)

Fターム[5F110BB09]に分類される特許

481 - 498 / 498

π電子共役系有機シラン化合物を用いた機能性有機薄膜及びその製造方法

【課題】 溶液プロセスを用いた簡便な方法により形成できるとともに、基板表面に強固に吸着でき、かつ、高い秩序性(結晶性)および高密パッキング特性を有する機能性有機薄膜およびその製造方法を提供すること。

【解決手段】 式;A−B−C−SiX1X2X3(Aは水素原子がハロゲン原子によって置換されていてもよい1価脂肪族炭化水素基であって、ハロゲン原子によって置換されていない場合は炭素数16〜30、ハロゲン原子によって置換されている場合は炭素数13〜25のもの;Bは酸素原子または硫黄原子;Cはπ電子共役を示す2価の有機基;X1〜X3は加水分解により水酸基を与える基)の有機シラン化合物を用いた機能性有機薄膜。上記有機シラン化合物のシリル基を加水分解して基板表面と反応させ、該基板に直接吸着した単分子膜を形成した後、該単分子膜上の未反応の有機シラン化合物を非水系有機溶剤を用いて洗浄除去する機能性有機薄膜の製造方法。

(もっと読む)

有機EL表示装置

【課題】 LCDや有機EL表示装置は表示部全体の輝度が均一であることが望ましいが、特に有機EL表示装置は、画素毎の輝度ムラが大きく問題である。また有機EL素子は輝度半減期があり、長寿命化も課題であった。

【解決手段】 画素毎にフォトセンサを配置し、有機EL素子の発光量に応じて画素毎に輝度を調整する。輝度の調整は発光量の小さい画素に合わせて輝度の大きい画素の電流量を小さくすることにより実現する。これにより低消費電力化を図り輝度ムラを補正できる。また受光回路で構成されるフォトセンサを画素毎に配置することにより、輝度ムラの補正を行い、更に、輝度半減期における輝度補正が可能となり、長寿命化が図れる。

(もっと読む)

光量検出回路

【課題】 薄膜トランジスタのフォトセンサは、光量は非常に微小なものであり、フィードバックが困難である。

【解決手段】 薄膜トランジスタのフォトセンサに、出力電流を電圧に変換する検出回路を付加する。これにより微小な電流をフィードバックが可能な所望の範囲の電圧に変換できる。また、回路は3つのTFTおよび1つの容量、または2つのTFTと1つの容量、1つの抵抗で構成されるので部品点数が削減できる。また動作もHレベルのパルスの入力のみでよく、簡易な光量検出回路を実現できる。

(もっと読む)

半導体装置及び通信システム

【課題】 本発明はプラスチック若しくはプラスチックフィルム基板のように熱的に脆弱な基板に、多結晶半導体を用いて高機能集積回路を形成した半導体装置であって、さらに無線で電力又は信号の送受信を行う半導体装置、及びその通信システムを提供することを課題とする。

【解決手段】 本発明は、ストレス・ピール・オフ法等の剥離方法を用い、熱的に脆弱なプラスチック基板へ、高機能集積回路を固定した半導体装置、具体的にはプロセッサであって、無線通信、例えばアンテナ又は受光素子により電力又は信号の送受信を行うことを特徴とする。

(もっと読む)

生体関連物質測定装置及び測定方法

【課題】ランニングコストが安く、検出用プローブが容易に固定化でき、簡便に使用できる生体分子検出素子を提供する。

【解決手段】ソース2、ドレイン3間のゲート絶縁物4の表面に導電性電極5を設けた絶縁ゲート電界効果トランジスタ1を用い、導電性電極5の表面に生体分子検出用プローブ6を固定化する。測定の際には、表面に生体分子検出用プローブ6を固定化した導電性電極5と参照電極7を測定セル8中の試料溶液9中に配置し、参照電極7に電源10により交流電圧を印加し、試料溶液9中に含まれるDNAやタンパク等の測定測定対象物と生体分子検出用プローブ6との結合の前後で変化する絶縁ゲート電界効果トランジスタ1の電気特性変化、すなわちソース2とドレイン3との間を流れる電流値の変化を検出する。

(もっと読む)

光量検出回路およびそれを用いた表示パネル

【課題】 ダイオードによるフォトセンサはその構造上リフレッシュができず、光が当たっていない時のリーク特性が不安定であるため、フォトセンサには不適当である。また、薄膜トランジスタのフォトセンサは、光量は非常に微小なものであり、フィードバックが困難となる問題があった。

【解決手段】 薄膜トランジスタのフォトセンサに、出力電流を電圧に変換する検出回路を付加する。これにより微小な電流をフィードバックが可能な所望の範囲の電圧に変換できる。また、回路を構成する抵抗、容量、フォトセンサの接続数を変動させることによりフォトセンサの感度を変化させることができる。

(もっと読む)

半導層および絶縁層を形成するために混合溶液を使ってボトムゲート型薄膜トランジスタを形成する改良された方法

【課題】電子デバイスにおいて、ポリマ層を形成し封じ込める。

【解決手段】絶縁性ポリマ層によって保護された半導性ポリマ層を形成する改良された方法を説明する。この方法では、半導性ポリマおよび絶縁性ポリマを形成する物質を溶媒中で溶解する。混合溶液を基板の上に堆積すると、半導性ポリマと絶縁性ポリマとが分離する。溶媒が気化すると、半導性物質はTFTのアクティグ領域を形成し、絶縁性ポリマは、半導性ポリマが空気に露出されることを最小限にする。

(もっと読む)

シリコン・オン・インシュレータ・ラッチアップ・パルス放射線検出器

【課題】シリコン・オン・インシュレータ技術を使用して形成した放射線検出器を提供すること。

【解決手段】この放射線検出器は、絶縁基板上に形成され、PNPN構造を有するシリコン層と、このPNPN構造上に形成され、PNゲートを有するゲート層とを備える。放射線検出器内の入射放射線に応答してのみ、ラッチアップが生じる。第2の態様は、シリコン・オン・インシュレータPNPNダイオード構造を備えており、放射線検出器内で入射放射線に応答してのみラッチアップが生じる、放射線検出器である。第3の態様は、絶縁基板上に形成されたシリコン層を備えており、このシリコン層が、PNPN構造とPNPN構造の上に形成されたゲート層とを備え、このゲート層がPNゲートを備えており、放射線検出器内で入射放射線に応答してのみラッチアップが生じる、シリコン・オン・インシュレータ放射線検出器である。

(もっと読む)

電界効果トランジスタ

【課題】 電界効果トランジスタのキャリアの移動度を向上させる。

【解決手段】 電界効果トランジスタに、強誘電性及び強磁性をともに有する物質を含有する絶縁部16と絶縁部16に対向して設けられ強磁性を少なくとも有する物質を含有する強磁性部14とを設ける。

(もっと読む)

多機能ドープ導電性ポリマー系電界効果デバイス

電界駆動デバイス及び作動方法が提供される。各デバイスは、印加電界に対して多機能の応答を提供するために、一種以上のドープ導電性ポリマーを使用している。デバイスは、デバイス(10)用のゲートコンタクト(22)を提供するように作動できる導電層(30)と、デバイス(10)用のソース(24)及びドレイン(26)コンタクト並びに活性層を提供するように作動できる導電性ポリマー層(14)と、導電層(12)と導電性ポリマー層(14)との間に形成された絶縁性ポリマー層(16)とを有し、前記層の組合わせにより、複数の応答機能の内の少なくとも2機能を行うようにデバイス(10)が作動できる。 (もっと読む)

エレクトロルミネッセント表示装置

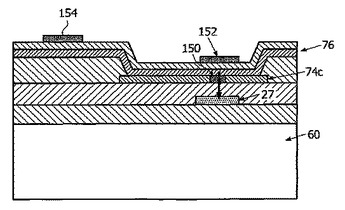

アクティブマトリックス型表示装置は共通基板(60)上に設けられた表示画素の配列を有する。各画素は、下部電極(74)及び実質的に透明な上部電極(80a)を有する上面放出型の電流駆動型発光表示素子(2)を有する。表示素子(2)の光出力を検出する光検出デバイス(27)が基板(60)と表示素子(2)との間に配置され、駆動トランジスタ(22)が光検出デバイス(27)の出力に応じて制御される。表示素子の下部電極(27)は、下部電極への入射光の最大で20%を透過させるために部分的に透過性であり、透過された光の少なくとも一部が下方の光検出デバイス(27)に導かれる。  (もっと読む)

(もっと読む)

金属トランジスターデバイス

本発明はトランジスターデバイスのチャネル領域の絶縁基板上に形成される金属薄膜あるいは複合金属層が含まれるデプレッションあるいはエンハンスメントモードの金属トランジスターに関する。

(もっと読む)

(もっと読む)

高速CMOS共存Ge−オン−インシュレータ光検出器の構造および製作方法

【課題】SiCMOS技術と共存可能な高速高効率光検出器を作る問題に対処すること。

【解決手段】本構造は、薄いSOI基板の上のGe吸収層から成り、分離領域、交互になるn型およびp型コンタクト、および低抵抗表面電極を利用する。本デバイスは、下の基板で生成されたキャリアを分離するために埋込み絶縁物を利用して高帯域幅を、Ge吸収層を利用して広いスペクトルにわたった高量子効率を、薄い吸収層および狭い電極間隔を利用して低電圧動作を、さらに平面構造およびIV族吸収材料の使用によってCMOSデバイスとの共存性を、達成する。本光検出器を製作する方法は、薄いSOIまたはエピタキシャル酸化物へのGeの直接成長および高品質吸収層を達成するための後の熱アニールを使用する。この方法は、相互拡散に利用可能なSiの量を制限し、それによって、下のSiによるGe層の実質的な希釈を起こすことなく、Ge層をアニールすることができるようになる。

(もっと読む)

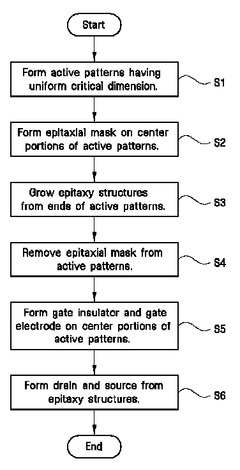

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

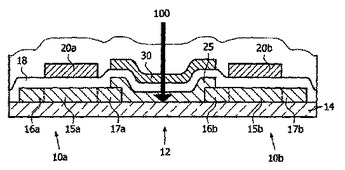

光センサーを備えたアクティブマトリックス型画素デバイス

基板に支持され、ポリシリコンTFT(10)及びアモルファスシリコン薄膜PINダイオード(12)を含む回路を有するアクティブマトリックス型画素デバイス、例えばEL表示装置、が提供される。ポリシリコンアイランドが形成された後に、アモルファスシリコン層がPINダイオード用に堆積されることにより、アモルファスシリコンは高温処理にさらされなくなる。TFTはドープされたソース/ドレイン領域(16a、17a)を有し、その一方(17a)はまた、ダイオードにN型又はP型のドープ領域を提供する。有利なことに、フォトダイオードに別個のドープ領域を設けることが不要になり、処理コストが削減される。反対導電型にドープされたソース/ドレイン領域(16b、17b)を有する第2のTFT(10b)が、ダイオードに他方のドープ領域(16b)を提供し、真性領域(25)が2つのTFT間にそれぞれのポリシリコンアイランドの各々に重なるように横方向に配置される。  (もっと読む)

(もっと読む)

高温電子素子

少なくともいくつかの実施例では、200℃を上回る温度での使用に適した電子素子は、炭化シリコン基板上に形成された集積回路と、厚い不活性化層とを有する。その他の実施例では、200℃を上回る温度での使用に適した電子素子は、サファイア基板上に配置されたシリコンから形成された集積回路と、厚い不活性化層とを有する。電子素子は、炭化水素掘削作業及び生産作業の関連で実装される。  (もっと読む)

(もっと読む)

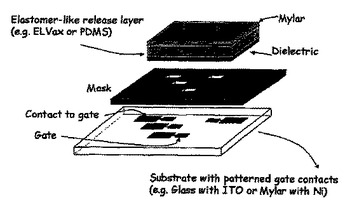

マスクを通した積層

本発明はドナー基板からレシーバ基板に材料のパターンを積層によって転写する方法である。転写された材料のパターンは、積層の際にドナーとレシーバとの間に挿入されたマスクの開口によって画定される。この技法は可撓性ポリマーレシーバ基板に適合しており、可撓性表示装置用の薄膜トランジスタを作製するのに有用である。

(もっと読む)

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法

【課題】 本発明は薄膜トランジスタアレイ及びその製造方法と液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法に関するものであり、均一性と性能に優れた薄膜トランジスタ及びその製造方法を生産性が高く低コストで提供することを目的とする。

【解決手段】 ゲート電極側面に側壁を形成することによって、自己整合的にLDDまたはオフセット領域を形成し、また、層間絶縁膜を複数の層で形成し、これら複数の層間絶縁膜上にソース・ドレイン電極とソースバス配線と画素電極を一括して形成する。

(もっと読む)

481 - 498 / 498

[ Back to top ]