Fターム[5F110DD21]の内容

Fターム[5F110DD21]に分類される特許

521 - 538 / 538

半導体装置及びその製造方法

【課題】電力用トランジスタと制御用半導体素子とを共通の基板上に備え、電力用トランジスタにおける電力損失が従来よりも大幅に低減された半導体装置を提供する。

【解決手段】半導体装置200は、トランジスタ2と、トランジスタ2のゲート電位を制御する半導体素子10、11とを備え、トランジスタ2および半導体素子10、11は共通の炭化珪素基板1の上に形成されており、トランジスタ2と半導体素子10、11とを電気的に分離する素子分離領域12をさらに含む。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

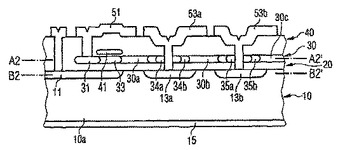

【課題】 接合基板上に例えば非単結晶シリコン半導体と単結晶シリコン半導体とを混在させると共に、COG技術によるディスプレイパネル製造よりも高い生産性を有し、接合工程を±1μm以内の高精度で行い、接合した単結晶シリコン基板から細い多数の配線に接続でき、高精度で高機能のディスプレイ半導体を効率的にかつ省スペースで製造し得る半導体装置の製造方法及び製造装置を提供する。

【解決手段】 半導体構造の少なくとも一部が形成された1個以上の単結晶Si基板10を、表面にエッジ32aを有する位置決め用基板30上に載置し、1個以上同時に位置決め用基板30の表面に平行にエッジ32aまで移動させて位置決めした後、一時固定する。単結晶Si基板10を、多結晶Siガラス基板40における、位置決め用基板30のエッジ32aに対応させた設定位置に一括で接合する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】 電界効果トランジスタの製造において、フォトリソグラフィーによって電極を形成するとゲート電極とソース/ドレイン電極間に位置ずれが生じる。

【解決手段】 頂上部のみが分離するように斜面上に活性層と絶縁層を形成する工程と、谷部および前記頂上部に電極を形成する工程を少なくとも含むことを特徴とする電界効果トランジスタの製造方法。

(もっと読む)

SOIおよびバルク・シリコン領域を含む半導体デバイス内のSTI形成

【課題】シリコン・オン・インシュレータ(SOI)領域およびバルク・シリコン領域内にシリコン・トレンチ分離部(STI)を形成する方法、および該方法により形成した半導体デバイスを開示する。

【解決手段】STIは、STIマスクを使用し、バルク・シリコン領域内の所望の深さまでエッチングし且つSOI領域の埋め込み絶縁体で停止する時限エッチングを実行し、SOI領域の埋め込み絶縁体を貫通してエッチングすることにより、SOI領域およびバルク・シリコン領域内で同時にSTIをエッチングすることができる。このプロセスの埋め込み絶縁体のエッチングは、ハードマスク除去ステップの一部として、それほど複雑でなく実行することができる。さらに、バルク領域とSOI領域の両方に同じ深さを選択することにより、その後のCMPプロセスでの問題が回避される。本発明は、窒化シリコンの残留物が存在することがあるSOI領域とバルク領域との境界において不要なものを取り除く。

(もっと読む)

電気光学装置及びプロジェクタ

【課題】 液晶装置等の電気光学装置において、画素電極を電気的に接続するためのコンタクトホール及びその付近でも耐光性を高め、高品位の画像を表示する。

【解決手段】 電気光学装置は、TFTアレイ基板(10)上に、透明な画素電極(9a)と、これにコンタクトホール(85)を介して接続されたTFT(30)と、画素電極とTFTとの間に積層されておりTFTのチャネル領域を上方から覆うと共に平面的に見てコンタクトホールを避けるように切り欠かれている容量線(300)とを備える。更に、この切り欠かれている領域を覆う部分遮光膜(401)を備える。

(もっと読む)

電気光学装置及び電子機器、並びに電気光学装置の製造方法

【課題】 電気光学装置において、他の不具合を発生させずに光リーク電流の発生を抑制し、高品位な表示を可能とする。

【解決手段】 基板上に、チャネル領域を有する半導体層を含んで構成された薄膜トランジスタと、薄膜トランジスタにより駆動される表示用電極と、半導体層の上層側及び下層側の少なくとも一方に積層された層間絶縁膜と、該層間絶縁膜の半導体層側とは反対側に積層された、チャネル領域を遮光するための遮光膜とを備えている。層間絶縁膜における半導体層とは反対側の表面には、チャネル領域のうち少なくともチャネル領域の縁部を遮光可能な領域において、半導体層に向かって局所的に窪んだ凹部が形成されている。遮光膜は、少なくとも凹部内に形成されている。

(もっと読む)

炭素微粒子構造体とその製造方法、およびこれを製造するための炭素微粒子転写体と炭素微粒子構造体製造用溶液、並びに炭素微粒子構造体を用いた炭素微粒子構造体電子素子とその製造方法、そして集積回路

【課題】 製造プロセスの簡便性を維持しつつ、半導体材料としての高性能を実現し得る新規な炭素微粒子構造体とその製造方法を提供すること。また、かかる炭素微粒子構造体の製造に適した物を提供すること。さらに、前記炭素微粒子構造体を用いた炭素微粒子構造体電子素子および集積回路を提供すること

【解決手段】 グラファイト構造を有する複数の炭素微粒子と、少なくともその一端がそれぞれ異なる前記炭素微粒子に結合された複数の官能基同士の化学結合により形成された架橋部位とを備え、前記複数の炭素微粒子が前記架橋部位と共に網目構造を構成してなることを特徴とする炭素微粒子構造体、とその製造方法、およびこれを製造するための炭素微粒子転写体と炭素微粒子構造体製造用溶液、並びに炭素微粒子構造体を用いた炭素微粒子構造体電子素子とその製造方法、そして集積回路である。

(もっと読む)

テーパ状単位セル金属酸化物半導体高電圧デバイス構造

電界効果電子デバイス(100,600)(例えばVDMOS等のFET)は、誘電体層(104,608)に隣接して配置されたフィールドプレート(105,607)を有しており、当該フィールドプレートは、半導体層(103,602)に隣接して配置されている。この場合、デバイスのドリフト領域は半導体層中にある。ドーピングレベルはドリフト領域に亘って略非線形的に変化し、デバイスは略一定の低減された表面電界を示す。電界効果デバイスの製造方法は、デバイスの半導体層のドリフト領域に非線形で不均一なドーピング密度を与えることを含んでいる。この場合、半導体層及び誘電体層の両方が一定でない厚さを有している。誘電体層は、low−k誘電材料によって形成され得る。  (もっと読む)

(もっと読む)

絶縁耐力の高いSOI半導体素子

本発明は、第1半導体域と第2半導体域との間に配置されたフィールド電極および/またはフィールド領域を備えた、SOI半導体素子に関するものである。電気的結合を、フィールド電極とフィールド領域との間で行うことができる。  (もっと読む)

(もっと読む)

ノード・キャパシタンスを増加した半導体メモリ・デバイス

【課題】 ノード・キャパシタンスを増加した半導体メモリ・デバイスを提供することにある。

【解決手段】 集積回路半導体メモリ・デバイス(100)は、ゲートから基板へのキャパシタンスを増加し、それにより、ソフト・エラー率を低減するために、ストレージ・トランジスタのゲートの下に基板(112)の一部分(130)には存在しないBOX層として特徴付けられた第1の誘電体層(116)を有する。第1の誘電体層とは異なる特性を有する第2の誘電体層(132)は、基板のその部分(130)を少なくとも部分的に覆う。このデバイスは、フィン(122)と、ゲートとフィンとの間のゲート誘電体層(124、126)とを含むFinFETデバイスにすることができ、第2の誘電体層はゲート誘電体層より漏れが少ない。

(もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

絶縁構造部上の半導体チャンネル

半導体装置基板上に貫通誘電体層を形成するステップと、貫通誘電体層の上部にトレンチ誘電体層を形成するステップと、貫通誘電体層を露出させるため、トレンチ誘電体層を貫通する溝を形成するステップと、基板を露出させるため、前記溝内の貫通誘電体層に貫通孔を形成するステップと、溝内および前記貫通孔内に半導体材料を形成するステップと、を有する方法を示した。装置基板と、該装置基板の表面に形成された誘電体層と、誘電体層上に形成された、装置基板と相間する結晶構造を有する装置基部と、を有する装置を示した。  (もっと読む)

(もっと読む)

高解像度構造を有する有機電子部品及びその生産方法

【課題】本発明は、高解像度構造を有する有機電子部品、特に低ソースドレーン間の距離を有する有機電界効果トランジスタ(OFET)及びその生産方法に関する。

【解決手段】有機電子部品は、生産中レーザーを用いて作られた凹部及び/又は修正された区域を有し、その中には、例えば、金属の導体トラック/電極が配置される。

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

薄膜電子部品の製造方法および製造装置ならびに薄膜電子部品

本発明は、薄膜電子部品の製造方法およびこの方法を実施する装置に関する。また、本発明は、この方法に従って製造された薄膜電子部品に関する。まず、実質的に誘電性を有する基板上に、導電性材料から成るガルヴァニックに均一な最下段の導電層が形成され、この最下段の導電層から導電領域がガルヴァニックに相互に分離して、電極パターンが形成される。この電極パターン上には、薄膜部品に必要とされる上部の不活性層または活性層を1層または数層形成することが可能である。本発明によれば、この最下段の導電層が分離することによる電極パターンの形成は、ダイカットエンボス加工に基づく切断作業を最下段の導電層に行うことによる。すなわち、切断作業に使用する切断部材の浮彫りが、基板上に永久変形が生じさせ、同時に、導電層から、ガルヴァニックに相互に分離した導電領域に至る領域をエンボス加工する。本発明は、ロールツーロール方式における薄膜部品の製造に適している。

(もっと読む)

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

電気光学装置及び電子機器

【課題】 液晶装置等の電気光学装置において、耐光性を高め、高品位の画像を表示する。

【解決手段】 電気光学装置は、TFTアレイ基板(10)上に、画素電極(9a)と、これに接続されたTFT(30)と、これに接続された配線(3a、6a)と、TFTの少なくともチャネル領域を上側から覆う上側遮光層(300、6a)と、このTFTの少なくともチャネル領域を下側から覆う下側遮光層(11a)とを備える。基板には、配線に対向する領域に格子状やストライプ状の溝(10cv)が掘られており、この溝内でチャネル領域に対向する領域に凹部(401)が更に掘られている。下側遮光膜は、該凹部内に形成されている。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

521 - 538 / 538

[ Back to top ]