Fターム[5F110EE07]の内容

Fターム[5F110EE07]に分類される特許

161 - 180 / 2,190

半導体装置の作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信

頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】絶縁表面上において、ゲート絶縁膜を間に挟んでゲート電極上に酸化物半導

体膜を形成し、酸化物半導体膜上に、チタン、モリブデンまたはタングステンを含む第1

の導電膜を形成し、第1の導電膜上に、電気陰性度が水素より低い金属を含む第2の導電

膜を形成し、第1の導電膜及び第2の導電膜をエッチングすることでソース電極及びドレ

イン電極を形成し、酸化物半導体膜、ソース電極及びドレイン電極上に、酸化物半導体膜

と接する絶縁膜を形成する半導体装置の作製方法。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】本発明は、低温かつ簡便で安価な製造工程により作製可能であり、トランジスタ特性に優れる、ダブルゲート構造を有する薄膜トランジスタおよびその製造方法を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成された第1ゲート電極と、上記第1ゲート電極を覆うように形成された第1ゲート絶縁層と、上記第1ゲート絶縁層上に形成され、低抵抗領域であるソースコンタクト領域およびドレインコンタクト領域ならびに高抵抗領域であるチャネル領域を有する酸化物半導体層と、上記ソースコンタクト領域に接して形成されたソース電極と、上記ドレインコンタクト領域に接して形成されたドレイン電極と、上記酸化物半導体層上に形成され、絶縁性有機材料を含む第2ゲート絶縁層と、上記第2ゲート絶縁層上に形成された第2ゲート電極とを有することを特徴とする薄膜トランジスタを提供する。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の

影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置

を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電

極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トラン

ジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を

用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。半導体装置に設けられる該薄膜トランジスタは多階調マスクによって形成されたレジストマスクを用いて作製する。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層421と、ゲート電極層上に設けられるゲート絶縁層402と、ゲート絶縁層上に設けられる第1の酸化物半導体層442と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層443と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

半導体装置

【課題】電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なプログラマブルなアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルを複数並列に接続されたプログラマブル回路とし、ユニットセル毎に導通または非導通の切り替えを行う。また、当該ユニットセルのスイッチとして、オフ電流を十分に小さくすることができる第1のトランジスタと、ゲート電極が第1のトランジスタのソース電極又はドレイン電極と電気的に接続された第2のトランジスタと、を含む構成とし、当該第2のトランジスタのゲート電位によってユニットセルの導通または非導通を制御する。

(もっと読む)

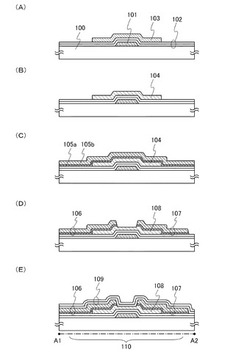

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

薄膜半導体装置と薄膜半導体装置を用いた表示装置

【課題】IGZO等の酸化物半導体膜からなる薄膜半導体装置において、無酸素雰囲気中で加熱しても酸素が酸化物半導体膜に拡散してTFT特性を発現する薄膜半導体装置を提供すること。

【解決手段】薄膜半導体装置は、ガラスの基板20、ゲート電極23G,ゲート絶縁膜21、ソース電極23S、ドレイン電極23D、IGZOの酸化物半導体膜24、二酸化マンガン(MnO2)の酸素放出絶縁膜25、保護膜22からなる。薄膜半導体装置は、蛍光表示装置等の薄膜形成時における加熱工程、焼成工程、封着工程において加熱すると、酸素が酸素放出絶縁膜25から放出されて酸化物半導体膜24に拡散してTFT特性を発現する。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

薄膜トランジスタの製造方法およびロール状薄膜トランジスタ

【課題】本発明は、低温かつ安価な製造工程により作製可能であり、トランジスタ特性に優れる薄膜トランジスタおよびその製造方法を提供することを主目的とするものである。

【解決手段】本発明は、基板と、ゲート電極と、ゲート絶縁層と、酸化物半導体層と、ソース電極と、ドレイン電極と、を有する薄膜トランジスタの製造方法であって、酸化性ガスを含む雰囲気で酸化物半導体層を形成する酸化物半導体層形成工程と、上記酸化物半導体層形成工程後、上記酸化物半導体層の少なくともチャネル領域に酸素欠損を付与して上記チャネル領域のキャリア濃度を制御するキャリア濃度制御工程と、を有することを特徴とする薄膜トランジスタの製造方法を提供する。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】ソース電極およびドレイン電極と有機半導体層とにおける電荷注入効率の向上と性能の確保とを両立させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含む金属含有材料により形成された有機半導体層と、互いに離間されたソース電極およびドレイン電極と、有機半導体層とソース電極およびドレイン電極とが重なる領域において有機半導体層とソース電極およびドレイン電極との間に挿入され、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含まない非金属含有材料により形成された有機導電層とを備える。

(もっと読む)

電子デバイス

【課題】薄膜トランジスタおよび/または電子デバイスの電荷キャリア移動度を増大させ、高い移動度および優れた安定性を達成する。

【解決手段】薄膜トランジスタの半導体層は、半導体組成物として、ポリマー結合剤および小分子半導体を含む。また、半導体層は、ソース電極およびドレイン電極の間の方向に配列したアライメント層上に堆積されている。アライメント層は、電子デバイスの電界効果移動度を増大させるために使用される。

(もっと読む)

薄膜トランジスタ

【課題】本発明は、優れた動作速度および安定性を有し、低温プロセスでの製造が可能な薄膜トランジスタを提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に配置された酸化物半導体層と、上記酸化物半導体層表面にチャネル領域となる間隔を空けて形成された二つの低抵抗層と、上記酸化物半導体層上の一部に形成され、シランカップリング剤を有する界面層と、上記界面層を介して上記二つの低抵抗層とそれぞれ接続するように配置されたソース電極およびドレイン電極と、上記界面層を覆うように形成され、樹脂を含有するゲート絶縁層と、上記チャネル領域を含むように上記ゲート絶縁層上に形成されたゲート電極と、を有することを特徴とする薄膜トランジスタを提供することにより上記課題を解決するものである。

(もっと読む)

有機薄膜トランジスタの評価方法

【課題】処有機薄膜トランジスタのチャネル領域の電荷状態の微視的様相を観測でき、電荷トラップなどの欠陥による電荷密度の変化を捉えることが可能な、有機薄膜トランジスタの評価方法を提供する。

【解決手段】基板上にゲート電極と、ソース電極と、ドレイン電極と、ゲート絶縁膜層と、有機半導体層とを備え、前記電極を介して印加する電圧によって該電極で画されたチャネル領域の電荷状態が制御を受ける薄膜トランジスタの評価方法であって、前記電極を通じて矩形波または正弦波により時間振動する変調電圧を印加するとともに、前記チャネル領域にレーザー光を照射してその透過光を得、前記変調電圧の高電圧時における透過光強度(T)と、該透過光強度(T)から前記変調電圧の低電圧時における透過光強度を差し引いた値(ΔT)を測定して、それらの値(TとΔT)に基づいて前記チャネル領域の電荷密度分布を求める。

(もっと読む)

161 - 180 / 2,190

[ Back to top ]