Fターム[5F110EE07]の内容

Fターム[5F110EE07]に分類される特許

201 - 220 / 2,190

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、非晶質酸化物半導体膜を形成し、該非晶質酸化物半導体膜に酸素を導入して酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、結晶性酸化物半導体膜を形成する。

(もっと読む)

信号処理装置

【課題】消費電力を抑えることができる信号処理装置を提供する。

【解決手段】信号処理装置が有する記憶回路に、酸化物半導体にチャネルが形成されるトランジスタを適用することで、電力の供給を停止している間もデータの保持(記憶)を可能とする。記憶回路に記憶されているデータは、信号処理装置への電力の供給を停止している間も、破壊すること無く読み出すことができる。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体装置

【課題】大電力の制御を行う、高耐圧の半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上の、ゲート電極と重畳する酸化物半導体層と、酸化物半導体層と接し、端部をゲート電極と重畳するソース電極及びドレイン電極と、を有し、ゲート電極と酸化物半導体層が重畳する領域において、ゲート絶縁層は、ドレイン電極と端部を重畳する第1の領域と、前記第1の領域と隣接する第2の領域と、を有し、第1の領域の静電容量は第2の領域の静電容量より小さいトランジスタを提供すること。

(もっと読む)

薄膜トランジスタ基板およびその製造方法

【課題】高い表示品位を有する表示装置用の薄膜トランジスタ基板およびこれらを生産効率よく実現することができる製造方法を提供する。

【解決手段】基板1上の複数の部分に配設された半導体膜2と、半導体膜2上に、該半導体膜2と接し互いに離間して配設されたソース電極およびドレイン電極4と、半導体膜2、ソース電極3およびドレイン電極4を覆うゲート絶縁膜6と、ゲート絶縁膜6を介して、ソース電極3およびドレイン電極4の間に跨るように配設された、ゲート電極7とを有した薄膜トランジスタ201と、半導体膜2上に、該半導体膜と接して配設された補助容量電極10と、下層に半導体膜2を有してソース電極から延在するソース配線31と、ゲート電極7から延在するゲート配線71と、ドレイン電極4に電気的に接続された画素電極9と、隣り合う画素の補助容量電極10どうしを電気的に接続する、補助容量電極接続配線12とを備えている。

(もっと読む)

半導体装置

【課題】周辺の回路構成を複雑にすることなく、繰り返しのデータの書き込みの際の劣化を低減することが可能な、不揮発性スイッチとして用いる半導体装置を提供する。

【解決手段】電源電圧が停止しても導通状態に関するデータの保持を、チャネル形成領域に酸化物半導体層を有する薄膜トランジスタに接続されたデータ保持部で行う構成とする。そしてデータ保持部は、ダーリントン接続された電界効果トランジスタ及びバイポーラトランジスタを有する電流増幅回路における、電界効果トランジスタのゲートに接続することでデータ保持部の電荷をリークすることなく、導通状態を制御する。

(もっと読む)

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供す

ることを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導

体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードであ

る。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれ

る電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度

化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導

体よりもバンドギャップが大きい。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

酸化物半導体層

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、特性の改善された酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを課題の一つとする。

【解決手段】絶縁表面を有する基板上にゲート電極層を形成し、ゲート電極層上にゲート絶縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層上にソース電極層及びドレイン電極層を形成し、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸素を含む絶縁層を形成し、酸素を含む絶縁層上に水素を含む絶縁層を形成した後、熱処理を行うことにより、水素を含む絶縁層中の水素を少なくとも酸化物半導体層に供給することを特徴とする半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】新たな構造の酸化物半導体層を用いた新たな構造の半導体装置を提供することを

目的の一とする。

【解決手段】絶縁表面を有する基板上の、第1の酸化物半導体層の表面から内部に向かっ

て成長させた結晶領域を有する第1の酸化物半導体層と、第1の酸化物半導体層上の第2

の酸化物半導体層と、第2の酸化物半導体層と接するソース電極層およびドレイン電極層

と、第2の酸化物半導体層、ソース電極層、およびドレイン電極層を覆うゲート絶縁層と

、ゲート絶縁層上の、第2の酸化物半導体層と重畳する領域のゲート電極層と、を有し、

第2の酸化物半導体層は、結晶領域から成長させた結晶を有する層である半導体装置であ

る。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置をより少ない工程で作製する。

【解決手段】トランジスタと、画素電極とを有し、トランジスタは、第1のゲート電極と、第1のゲート電極上の第1の絶縁層と、第1の絶縁層上の半導体層と、半導体層上の第2の絶縁層と、第2の絶縁層上の第2のゲート電極とを有し、第1のゲート電極は、第1の絶縁層を介して、半導体層と重なる領域を有し、第2のゲート電極は、第2の絶縁層を介して、半導体層と重なる領域を有し、画素電極は、第2の絶縁層上に設けられ、第1の領域は、第2のゲート電極の少なくとも一部が、半導体層の少なくとも一部と重なる領域のうちの、少なくとも一部の領域であり、第2の領域は、画素電極が設けられた領域のうちの、少なくとも一部の領域であり、第1の領域における第2の絶縁層は、第2の領域における第2の絶縁層よりも薄い。

(もっと読む)

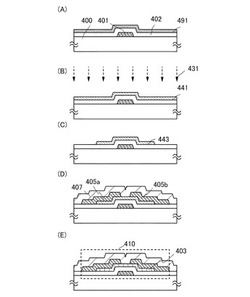

半導体装置の作製方法

【課題】チャネル形成領域が形成される半導体層のチャネル形成領域と逆側近傍の加工方法を工夫した半導体装置の作製方法を提供する。

【解決手段】少なくとも結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、少なくとも第1のエッチングと第2のエッチングを行い、第1のエッチングは非晶質半導体膜の一部を残存させつつ行い、第2のエッチングは非晶質半導体膜上の被覆膜を除去させた後に、非晶質半導体膜に対するエッチングレートが高く、且つ結晶性半導体膜に対するエッチングレートが低い条件により行い、積層半導体膜に設けられた結晶性半導体膜の一部を露出させる。

(もっと読む)

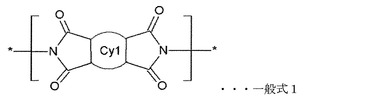

有機保護膜組成物およびこれから製造される有機保護膜を含む薄膜トランジスタ、並びに電子素子

【課題】有機薄膜トランジスタの長期的な信頼性を向上させることのできる有機保護膜組成物を提供する。

【解決手段】下記の一般式1および一般式2の構造単位を含むオリゴマーまたはポリマーと、架橋剤と、を含む。

(もっと読む)

(もっと読む)

有機薄膜トランジスタ及び有機薄膜トランジスタの製造方法

【課題】有機半導体層の形成位置について、別途精密な制御を必要とすることなく、高精細なパターニングが行われた有機半導体層を有する有機薄膜トランジスタ及びその製造方法を提供することにある。

【解決手段】ソース電極1、ドレイン電極2、ゲート電極3、有機半導体層4及びゲート絶縁膜5を備え前記ソース電極1及び前記ドレイン電極2の表面エネルギーが、いずれも30mN/m以下であることを特徴とする。

(もっと読む)

アレイ基板及びその製造方法

【課題】アレイ基板及びその製造方法を提供する。

【解決手段】本発明による製造方法は、基板に無機材料の突起を形成するステップと;それぞれ第一透明導電層と第一金属層からなる反射領域パターン、ゲートライン及びゲートラインから分岐して出されるゲート電極と共通電極を形成するステップと;半導体層からなる活性化ランドパターンと第二金属層からなるデータラインパターンを形成し、活性化ランドパターン上でデータラインに接続されるソース電極とドレイン電極、及び半導体層からなるチャネルを形成するステップと;基板に無機材料を塗布し、無機材料に対して焼き戻し工程を行って一平坦層を形成し、ドレイン電極にビアホールを形成するステップと;反射領域に、ビアホールを介してドレイン電極に接続され且つ第二透明導電層からなる画素電極を形成するステップと、を有する。

(もっと読む)

酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法

【課題】酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法を提供すること。

【解決手段】酸化物半導体素子は、基板上に配置されるゲート電極と、リセス構造を含むゲート絶縁層と、ゲート絶縁層の一側上に配置されるソース電極と、ゲート絶縁層の他側上に配置されるドレーン電極と、ゲート絶縁層、ソース電極、及びドレーン電極上に配置されるアクティブパターンとを含むようにすることができる。リセス構造はゲート電極の上部に位置するようにすることができ、アクティブパターンはリセス構造を埋め立てるようにすることができる。酸化物半導体素子がリセス構造を有するゲート絶縁層を具備することによって、電荷移動度、閾値電圧分布、動作電流などの多様な電気的特性を向上させることができる。

(もっと読む)

半導体装置

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。

【解決手段】酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物

半導体膜を形成した後、酸化物半導体膜が露出した状態で第1の加熱処理を行う。次いで

、酸化物半導体膜中の水分、または水素などの不純物をさらに低減するために、イオン注

入法またはイオンドーピング法などを用いて、酸化物半導体膜に酸素を添加した後、再び

、酸化物半導体膜が露出した状態で第2の加熱処理を行う。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

201 - 220 / 2,190

[ Back to top ]