Fターム[5F110EE14]の内容

Fターム[5F110EE14]の下位に属するFターム

三層以上 (1,118)

Fターム[5F110EE14]に分類される特許

121 - 140 / 3,665

半導体装置

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】耐圧をより向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体積層構造8と、基板1と化合物半導体積層構造8との間に形成された非晶質性絶縁膜2と、が設けられている。

(もっと読む)

電子装置およびその製造方法

【課題】開口部を形成されることにより、大きなバンドギャップを有するグラフェンシートを有する電子装置を提供する。

【解決手段】基板と、前記基板上に形成されたグラフェンシート23と、前記グラフェンシートの一端に形成されたソース電極23Sと、前記グラフェンシートの他端に形成されたドレイン電極23Dと、前記グラフェンシート上ゲート絶縁膜を介して形成され、前記グラフェンシートにゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部23Aよりなる開口部列と、を備え、前記複数の開口部はいずれも、三つのジグザグ端により画成されて正三角形の形状を有し、前記ジグザグ端のうち二つは、前記ソース電極とドレイン電極を結んだ方向に対し30°の角度をなし、もう一つのジグザグ端は90°の角度をなし、それぞれの正三角形の向きを揃えて形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

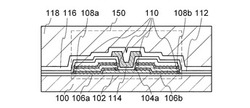

薄膜トランジスタ、その製造方法、および表示装置

【課題】酸化物半導体を用いた低温プロセスで形成する信頼性の高い薄膜トランジスタ、その製造方法、および表示装置を提供する。

【解決手段】薄膜トランジスタ1は、基板100と、前記基板上の一部に設けられたゲート電極110と、前記ゲート電極を覆う第1の絶縁膜120と、前記第1の絶縁膜を介して前記ゲート電極上に設けられた酸化物半導体膜130と、前記酸化物半導体膜上の一部に設けられた第2の絶縁膜150と、前記酸化物半導体膜から露出する酸化物半導体膜の一部と接続されたソース電極140Sおよびドレイン電極140Dと、を備え、前記酸化物半導体膜はInと、Gaと、Znのうち少なくとも一つの元素を含む酸化物半導体を有し、前記第1の絶縁膜中に含有される水素濃度が5×1020atm/cm−3以上であり、かつ、前記第2の絶縁膜中に含有される水素濃度が1019atm/cm−3以下である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

横型半導体装置及びその製造方法

【課題】既存のCMOS製造工程に対して工程の追加や変更を行うことなく、素子に要求される耐圧に応じて横型半導体装置が有するLocos酸化膜を最適に制御することができる、横型半導体装置の製造方法を提供する。

【解決手段】半導体基板(100、101)上のLocos形成領域に、遮蔽部及び開口部が所定の幅及び間隔で設けられたパターン(113a、113b)を有するマスク(113)を形成する(工程3a、3b)。マスク(113)を用いた熱酸化処理を施してLocos形成領域を酸化させ、半導体基板(100、101)のドリフト領域上に厚さが異なる(115a、155b)Locos酸化膜(105a、105b)を同時に形成する(工程4a、4b)。

(もっと読む)

薄膜トランジスタ、画像表示装置

【課題】酸化物半導体層のバックチャネル部を半導体層成膜後の薄膜トランジスタ作製工程によるダメージから保護し、良好なトランジスタ特性を得ると共に、薄膜トランジスタ作製の工程数を削減することである。

【解決手段】基板1と、基板1上に設けられたゲート電極2と、基板1上に設けられ、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上に設けられ、アモルファス酸化物からなる半導体層4と、半導体層4上に設けられた保護膜5と、ゲート絶縁膜3上に設けられたソース電極6、及びドレイン電極7と、を備え、保護膜5を、金属材料の化成処理、又は陽極酸化によって形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

半導体装置

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な

容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜

上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、

前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、

容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、より安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極およびドレイン電極と、保護膜と、を有し、該保護膜は金属酸化膜を有し、該金属酸化膜は、膜密度が3.2g/cm3以上である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】GaとSiとの反応を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、Si基板1と、Si基板1の表面に形成されたSi酸化層3と、Si酸化層3上に形成され、Si酸化層3の一部を露出する核形成層2と、Si酸化層3及び核形成層2上に形成された化合物半導体積層構造9と、が設けられている。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電気特性の安定した半導体装置を提供する。とくに、酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜と接して形成されたソース電極、及びドレイン電極と、を有し、ゲート絶縁膜は、少なくとも酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された酸素放出型の酸化膜と、により構成され、酸素放出型の酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、現在実用化されている量産技術からの膜構成、プロセス条件、または生産装置等の変更が少なく、半導体装置に安定した電気特性を付与し、信頼性の高い半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、を有し、ゲート絶縁膜は、窒化酸化シリコン膜と、窒化酸化シリコン膜上に形成された酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された金属酸化膜と、を含み、金属酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

有機電界効果型トランジスタ

【課題】カーボンナノチューブを含有する活性層を有する有機電界効果型トランジスタにおいて、熱プロセス、経時変化、外部環境に対して、移動度、Von、ヒステリシスの性能を安定化すること。

【解決手段】ゲート電極、ゲート絶縁層、カーボンナノチューブを含有する活性層、該活性層に対して前記ゲート絶縁層と反対側に形成された架橋構造を持つポリシロキサンを含む第2絶縁層、ソース電極およびドレイン電極を有する有機電界効果型トランジスタ。

(もっと読む)

121 - 140 / 3,665

[ Back to top ]