Fターム[5F110EE27]の内容

Fターム[5F110EE27]の下位に属するFターム

Fターム[5F110EE27]に分類される特許

61 - 80 / 196

半導体デバイスの動作方法

【課題】高いバイアス電圧を必要とせずに、メモリセルとして動作可能なマルチゲート半導体デバイスを提供する。

【解決手段】マルチゲートMOSFETをベースとした、比較的低いバイアス電圧を要するキャパシタレスのメモリデバイス。充分な本体係数を用意し、VTフィードバックループを導入することによって、閾値電圧をゲート−本体間電圧を関連させる蓄積層を用いて、ヒステリシスウインドウ(H)を導入できる。MOSFETは、「1」値または「0」値を保存することができ(54,51)、(プログラムウインドウPWの範囲内で)保存した値を読み出し、ホールドする(50)。デバイスは、1.5Vなどの比較的低い動作電圧、1016動作サイクルなどの高い信頼性、〜5秒などの長い保持時間で動作する。

(もっと読む)

半導体装置及び表示装置

【課題】直流変換回路を有する半導体装置の消費電力を低減することを課題の一とする。

【解決手段】直流変換回路と、マイクロプロセッサとを有し、直流変換回路は、変換回路と、制御回路とを有し、変換回路は、誘導素子と、トランジスタとを有し、制御回路は、比較回路と、論理回路とを有し、比較回路としてヒステリシスコンパレータを用い、制御回路では、比較回路が変換回路の出力信号と第1の基準電位又は第2の基準電位とを比較し、論理回路が比較回路の出力信号とマイクロプロセッサのクロック信号とを演算し、変換回路では、トランジスタが論理回路の出力信号に応じて誘導素子に流れる電流を制御し、誘導素子に流れる電流に応じて変換回路の出力信号を生成する。

(もっと読む)

半導体基板の保持用トレイ、並びに半導体基板および半導体装置の作製方法

【課題】複数枚の絶縁層被覆単結晶半導体基板に対して効率よくイオン注入を行い、大面積の単結晶半導体層を備えた半導体基板の作製方法を提供することを課題の一とする。

【解決手段】半導体基板の作製工程において、表面のファンデルワールス力を調整した保持用トレイに表面に絶縁層が形成された複数枚の単結晶半導体基板を貼り合わせ、複数枚の単結晶半導体基板にイオン照射工程を行うことで複数枚の単結晶半導体基板の所定の深さに脆化層を形成し、複数枚の単結晶半導体基板にファンデルワールス力を調整したベース基板を貼り合わせることでファンデルワールス力の差を利用して保持用トレイを選択的に分離し、剥離加熱処理を行い劈開面を形成して単結晶半導体基板をベース基板から分離することにより、絶縁層を介して単結晶半導体基板をベース基板に転載する。

(もっと読む)

電源回路

【課題】回路の動作が劣化するのを抑制すること、及び、回路全体の面積を抑制することを課題とする。

【解決手段】第1の電圧が入力される第1の端子と、第2の電圧が入力される第2の端子と、前記第1の端子及び第2の端子に接続され、前記第1の電圧と第2の電圧を比較するコンパレータと、前記コンパレータから出力された第1のデジタル信号を、平均化し、積分し、デジタルPWM処理するデジタル回路と、前記デジタル回路から出力された第2のデジタル信号を増幅するPWM出力ドライバと、前記増幅された第2のデジタル信号を平滑する平滑化回路とを有する電源回路を提供する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】酸化物半導体層を有するトランジスタにおいて、ゲート絶縁層を酸化ガリウム膜として、酸化物半導体層と接する構成とする。また、酸化物半導体層の上下を挟むように酸化ガリウム膜を配置することによって信頼性の向上を実現する。また、ゲート絶縁層は、酸化ガリウム膜と酸化ハフニウム膜の積層構造としてもよい。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】平坦性の高い表面を有する単結晶半導体層を備えた半導体基板の作製方法を提供することを目的の一とする。平坦性の高い単結晶半導体層を備えた半導体基板を用いて信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】半導体基板の作製工程において、単結晶半導体基板に希ガスイオン照射工程、レーザー照射工程および水素イオン照射工程を行うことで、単結晶半導体基板の所定の深さに大きな結晶欠陥を含有した薄い脆化領域を形成し、剥離加熱工程を行うことで脆化領域より表面側の単結晶半導体層をベース基板に転載する。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体基板に付着する異物の影響を低減し、歩留まりよく半導体基板を作製することを目的の一とする。安定な特性を有する半導体装置を歩留まりよく作製することを目的の一とする。

【解決手段】半導体基板の作製工程において、単結晶半導体基板に脆化領域を形成する際、単結晶半導体基板表面に対して複数の(少なくとも二つ以上の)異なる角度で斜め方向から水素イオンを照射することによって、単結晶半導体基板に付着する異物の影響を低減し、均一な単結晶半導体層を有する半導体基板を歩留まりよく作製することができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いる薄膜トランジスタにおいて、安定した電気特性を有する信頼性のよい薄膜トランジスタを提供することを課題の一つとする。

【解決手段】酸化物半導体膜を用いる薄膜トランジスタのチャネル長が1.5μm以上100μm以下、好ましくは3μm以上10μm以下の範囲において、−25℃以上150℃以下の動作温度範囲で、チャネル幅が1μmあたりのオフ電流の値を1×10−12A以下とすることで、安定した電気特性を有する半導体装置を作製することができる。特に半導体装置の一態様である表示装置において、オフ電流の変動に起因する消費電力を低減することができる。

(もっと読む)

記憶装置、半導体装置

【課題】データの書き込み不良を抑えつつ、面積を小さく抑えることができる不揮発性の記憶装置、または当該不揮発性の記憶装置を用いた半導体装置の提供を目的の一とする。

【解決手段】不揮発性の記憶素子を有する第1の記憶部と、上記第1の記憶部へのデータの書き込みが正確に行われたかどうかを検証するベリファイ動作において、上記データを一時的に保存するための第2の記憶部(データバッファ)とを有する。そして、第2の記憶部が、記憶素子と、当該記憶素子における電荷の保持を制御するための、オフ電流またはリーク電流が極めて小さい絶縁ゲート電界効果型トランジスタとを有する。

(もっと読む)

多環式化合物及び有機半導体デバイス

【課題】有機半導体活性層の薄膜を与え得る新規化合物の提供。

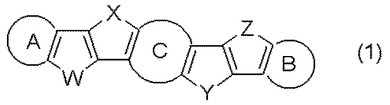

【解決手段】式(1)

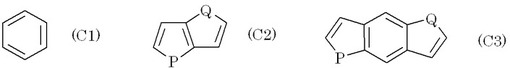

(式中、環構造Cは、式(C1)、式(C2)または式(C3)で示される環を表わす。

(式中、PおよびQは、硫黄原子、酸素原子、セレン原子またはテルル原子を表わす。W、X、YおよびZは、硫黄原子、セレン原子またはN−(R15)等を表わす。環構造Aおよび環構造Bは、芳香族性炭素環または芳香族性複素環を表わす。R15はアルキル基を表わす。))で示される多環式化合物。

(もっと読む)

昇圧回路及び昇圧回路を用いたRFIDタグ

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

半導体装置及びその作製方法

【課題】プラスチックフィルム基板などの柔軟性を有するフレキシブル基板に転写後のデバイスに対してFPCを圧着する際、クラック等の不良発生を防止する。

【解決手段】転写する被剥離層として、素子を有する回路を含む層405aと、端子電極405bとを形成し、その上にクラックを防止するための樹脂からなる保護層405cを形成す。FPCの接続を行う部分において、端子電極の電極面が露出している。FPC407を圧着して異方性導電フィルム406により接続を行う。この圧着工程において、保護層405cによって配線が保護されているため、加圧変形によるクラックの発生を防止することができる。

(もっと読む)

半導体装置

【課題】各種回路に配置される薄膜トランジスタの構造を、回路の機能に応じて適切なものとすることにより、半導体装置の動作特性および信頼性を向上させ、かつ、低消費電力化を図ると共に、工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】薄膜トランジスタのLDD領域を、テーパー部を有するゲート電極及びテーパー部を有するゲート絶縁膜に対応させて設ける。具体的には、第1のLDD領域はゲート電極のテーパー部の下に設けられ、第2のLDD領域はゲート絶縁膜のテーパー部の下に設けられる。

(もっと読む)

表示装置

【課題】表示装置の消費電力を低減すること及び表示の劣化(表示品質の低下)を抑制することを課題の一とする。また、本発明の一態様は、温度などの外部因子に対する表示の劣化(表示品質の低下)が抑制された液晶表示装置を提供することを課題の一とする。

【解決手段】表示装置の駆動回路部に、選択されたピクセルに逐次画像信号を書き込んで画像を画面に表示すると共に、同一画像を画面に表示する場合には、画像信号を書き込む動作を停止させ、トランジスタをオフ状態として画面に書き込まれた画像をそのまま保持させておく機能を設ける。このような機能をオフ電流を、室温にてチャネル幅1μm当たり10zA/μm未満、85℃にて100zA/μm未満と極めて低いレベルにまで低減されたトランジスタによって実現する。

(もっと読む)

半導体装置の作製方法

【課題】結晶粒の位置とその大きさを制御した結晶質半導体膜を作製し、さらにその結晶質半導体膜をTFTのチャネル形成領域に用いることにより高速動作を可能にする。

【解決手段】基板1上に、島状で且つ端部にテーパーを有する膜2を設け、無機絶縁膜3、非晶質半導体膜を形成する。そして、レーザーアニールにより非晶質半導体膜を結晶化させる。島状で且つ端部にテーパーを有する膜2または無機絶縁膜3の材料及び膜厚を適宜調節することによって半導体膜の冷却速度を遅くして結晶粒径の大きな第1領域4aを形成する。

(もっと読む)

表示装置

【課題】本発明の一態様は、表示装置の高画質化を図りつつ、消費電力を低減すること及び表示の劣化(表示品質の低下)を抑制することを課題の一とする。

【解決手段】酸化物半導体層がゲート絶縁層を介してゲート電極と重畳するように設けられたトランジスタと、トランジスタのソース側又はドレイン側に接続された液晶を駆動する画素電極と、画素電極と対向するように設けられた対向電極と、画素電極と対向電極との間に設けられた液晶層とを有するサブユニットを複数有するユニットが、一又は複数設けられたピクセルがマトリクス状に配置されて画像を表示する表示パネルにおいて、オフ電流が、室温にてチャネル幅1μm当たり10zA/μm未満、85℃にて100zA/μm未満であるトランジスタを用いる。

(もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

表示装置、及び当該表示装置を具備する電子機器

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソースまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソースまたはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供給される信号の出力が停止される期間を有する。

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

表示装置、及び当該表示装置を具備する電子機器

【課題】ブルー相を示す液晶材料を利用した表示装置において、消費電力の低い表示装置を提供する。

【解決手段】トランジスタを含む画素が設けられた画素部を有する第1の基板と、前記第1の基板と対向する第2の基板と、前記第1の基板及び前記第2の基板の間に配置された液晶層とを有し、前記液晶層は、ブルー相を示す液晶材料を有し、前記トランジスタは、ゲートが走査線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソースまたはドレインの他方が電極に電気的に接続され、前記トランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。

(もっと読む)

61 - 80 / 196

[ Back to top ]