Fターム[5F110EE27]の内容

Fターム[5F110EE27]の下位に属するFターム

Fターム[5F110EE27]に分類される特許

141 - 160 / 196

半導体装置及びその作製方法

【課題】ゲート絶縁膜の膜厚が薄くなった部分、即ち、段差部による半導体素子特性への影響を低減し、半導体素子の信頼性を向上させることを目的とする。また、そのような半導体素子を有する半導体装置を実現するための作製方法を提供することも課題とする。

【解決手段】絶縁表面上に形成される半導体層と、半導体層上に形成される第1の絶縁層と、半導体層の端部を酸素を含む雰囲気下でプラズマ処理することにより形成される第2の絶縁層と、第1の絶縁層上及び第2の絶縁層上に形成されるゲート電極と、を有する。なお、第2の絶縁層は、半導体層のチャネル形成領域と接する酸化膜である。

(もっと読む)

窒化物系半導体ヘテロ接合電界効果トランジスタ

【課題】ノーマリオフ動作を達成でき、充分なチャンネル電流を得ることができ、かつしきい値電圧の制御が容易な窒化物系半導体ヘテロ接合電界効果トランジスタを提供する。

【解決手段】負の電荷を有する第三の層である浮遊ゲート層(32)が制御ゲート電極(34)とAlGaN 層(11)との間に設けられているので、実質的に浮遊ゲート層(32)に隣接するAlGaN 層(11)の電子に対するポテンシャルを実質的に高くし、チャンネルを空乏化する。これにより、ゲート電圧がゼロの時チャンネルに電流(ドレイン電流)を流れなくする、即ちいわゆるノーマリオフ動作を達成することが出来る。

(もっと読む)

薄膜半導体装置の製造方法

【課題】低い基板温度であっても成膜速度を維持して結晶性のシリコン薄膜を基板上に成膜可能で、これにより基板上への結晶性のシリコン薄膜の直接成膜を産業上において実用化すると共に、このシリコン薄膜を用いることで高性能化が図られた薄膜半導体装置の製造方法を提供する。

【解決手段】SinH2n+2(n=1,2,3,…)で表されるシラン系ガスと、ハロゲン化ゲルマニウムガスとを原料ガスとして用いたプラズマCVD法により、結晶構造を含むシリコン薄膜を基板上に成膜する工程を行う。ハロゲン化ゲルマニウムガスとしては、GeF2、GeF4、およびGeCl4のうちの少なくとも1つを用いる。原料ガスとしてさらにドーパントガスを用いることにより、活性化されたドーパントを含有するシリコン薄膜が成膜される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体膜のチャネル形成領域の端部の特性がトランジスタの特性へ及ぼす影響を低減することを課題とする。

【解決手段】基板上に半導体膜とゲート絶縁膜と第1の導電膜を順に積層した積層体を形成し、積層体を除去することによって、島状に設けられた複数の積層体とし、島状に設けられた積層体を覆うように絶縁膜を形成し、第1の導電膜の表面と高さが概略一致するように絶縁膜の一部を除去して第1の導電膜の表面を露出させ、第1の導電膜上及び残存した第1の絶縁膜上に第2の導電膜を形成し、第2の導電膜上にレジストを形成し、レジストをマスクとして、第1の導電膜及び第2の導電膜を選択的に除去する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】ゲート絶縁膜の被覆不良によるゲート電極と半導体層とのショート及びリーク電流などの不良が防止された信頼性の高い半導体装置、及びそのような半導体装置の作製方法を提供することを目的とする。

【解決手段】絶縁表面上に複数の半導体素子を形成するために、連続した半導体層中に半導体素子として機能する素子領域と、抵抗が高く素子領域間を電気的に分離する機能を有する素子分離領域を形成する。素子分離領域は、連続した半導体層において、素子間を電気的に分離するために、選択的に酸素、窒素、及び炭素のうち少なくとも一種以上の不純物元素を添加して形成する。

(もっと読む)

半導体集積回路及びその作製方法、並びに半導体集積回路を用いた半導体装置

【課題】半導体基板にスルーホールを形成する工程や、半導体基板を裏面から研磨する工程は、非常に長い時間を要し生産性を低下させる要因となる。また、半導体基板を積層する構造であるため、積層して形成された半導体集積回路は厚くなり機械的な柔軟性に劣っている。

【解決手段】複数の基板上に剥離層を形成し、剥離層上に半導体素子、および貫通配線のための開口部を形成する。そして、半導体素子を有する層を基板から剥離し、重ね合わせて積層し、開口部に導電性を有する層を形成して貫通配線を形成することによって半導体集積回路を作製する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】絶縁層の被覆不良によるゲート電極層と半導体層とのショート及びリーク電流などの不良が防止された信頼性の高い半導体装置、及びそのような半導体装置の作製方法を提供することを目的とする。

【解決手段】絶縁表面上に複数の半導体素子を形成するために、半導体層を複数の島状の半導体層に分離せず、連続した半導体層中に半導体素子として機能する複数の素子領域を電気的に絶縁分離する素子分離領域として、高い抵抗を有する第1の素子分離領域及び素子領域と接し素子領域の有するソース領域及びドレイン領域と逆導電型を有する第2の素子分離領域を形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】絶縁層の被覆不良によるゲート電極層と半導体層とのショート及びリーク電流などの不良が防止された信頼性の高い半導体装置、及びそのような半導体装置の作製方法を提供することを目的とする。

【解決手段】絶縁表面上に複数の半導体素子を形成するために、連続した一つの半導体層中に半導体素子として機能する素子領域と、PN接合の繰り返しにより素子領域間を電気的に分離する機能を有する素子分離領域を形成する。素子分離領域は、連続した一つの半導体層において、素子間を電気的に分離するために、選択的に酸素、窒素、及び炭素のうち少なくとも一種以上の不純物元素及び接する素子領域と逆導電型を付与する不純物元素を添加して形成する。

(もっと読む)

半導体装置

【課題】増幅回路内の寄生抵抗を、補正抵抗を設置することで調整し、増幅回路を安定に動作させる。

【解決手段】カレントミラー回路において、カレントミラー回路内の寄生抵抗に対して、寄生抵抗を補正する補正抵抗が設置されている半導体装置であり、カレントミラー回路は、少なくとも2つの薄膜トランジスタを有するものである。薄膜トランジスタのそれぞれは、チャネル形成領域、ソース領域またはドレイン領域を有する島状半導体膜、ゲート絶縁膜、ゲート電極、ソース電極またはドレイン電極を有しており、補正抵抗は、ゲート電極、ソース電極、もしくはドレイン電極のいずれか1つの寄生抵抗を補正するものである。また補正抵抗はそれぞれ、ゲート電極、ソース電極またはドレイン電極、もしくはソース領域またはドレイン領域と同じ材料を含む導電層を有するものである。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリの消去動作として、PウェルやNウェルなどの基板端子を用いないで、不揮発性メモリ素子における電荷蓄積部に注入された電荷を放出する、すなわちNAND型不揮発性メモリのデータの消去動作する方法を提供することを課題とする。

【解決手段】NAND型不揮発性メモリにおけるデータの消去方法において、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出について、ビット線、ソース線、及び制御ゲートに電位を印加することにより行う。そして、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出を、電荷を放出する不揮発性メモリ素子のソース端子、ドレイン端子、及び制御ゲートに電位を印加することにより行う。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板上に画素と不揮発性メモリとを備え、前記不揮発性メモリは、基板上に形成される半導体活性層と、前記半導体活性層上に形成される絶縁膜と、前記絶縁膜上に形成されるフローティングゲイト電極と、前記フローティングゲイト電極を酸化して得られる酸化膜と、前記酸化膜に接して形成されるコントロールゲイト電極と、を備え、前記画素と前記不揮発性メモリとは、前記基板上に一体形成される。このことによって上記課題が達成される。

(もっと読む)

発光装置及び素子基板

【課題】 スイッチング用トランジスタのオフ電流を低く抑え、容量素子の大容量化を図らずとも、駆動用トランジスタの特性のばらつきに起因する、画素間における発光素子の輝度ムラを抑えることができる発光装置及び素子基板の提案を課題とする。

【解決手段】 本発明では、駆動用トランジスタのゲートの電位は固定し、前記駆動用トランジスタは飽和領域で動作させ、常に電流を流せる状態にしておく。前記駆動用トランジスタと直列に線形領域で動作する電流制御用トランジスタを配し、スイッチング用トランジスタを介して画素の発光、非発光の信号を伝えるビデオ信号を前記電流制御用トランジスタのゲートに入力する。

(もっと読む)

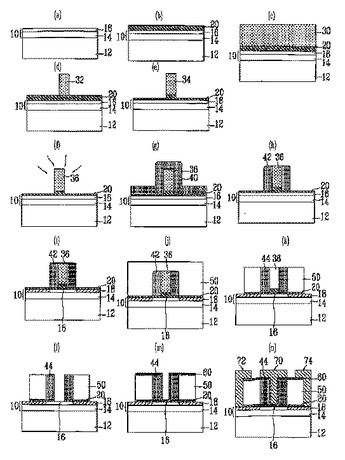

異なった動作機能を示すゲートを有する2重ゲート半導体デバイスおよびその製造方法

2重ゲートFinFETおよびその製造方法を提供する。FinFETは、フィン(20)の各側面に隣接して第1および第2ゲート(72、74)を有し、第1ゲートのフィンに対面する少なくとも一部分を多結晶シリコンによって形成し、第2ゲートのフィンに対面する少なくとも一部分を金属シリサイド化合物によって形成する。2個のゲートの異なった組成は、それぞれ異なった動作機能を提供し、短チャンネル効果を減少させる。  (もっと読む)

(もっと読む)

P型薄膜トランジスタ、N型薄膜トランジスタ及び半導体装置

【課題】TFT特性の低下、バイアスストレスによるTFT特性の変動を抑えられるP型薄膜トランジスタ、N型薄膜トランジスタ、半導体装置及び表示装置を提供する。

【解決手段】基板上に、チャネル領域、ソース及びドレインを有する半導体層と、第1絶縁膜と、第1ゲート電極と、第2絶縁膜と、第2ゲート電極とがこの順に積層された構造を有するP型薄膜トランジスタであって、上記第1ゲート電極は、フローティングゲートを構成し、上記P型薄膜トランジスタは、第2ゲート電極に印加されるゲート電圧がソースの電位を基準として−20V以上、+10V以下のときに、半導体層及び第1ゲート電極が重複する領域の第1絶縁膜に印加される電界強度と、第1ゲート電極及び第2ゲート電極が重複する領域の第2絶縁膜に印加される電界強度とが、ともに3.4MV/cm未満であるP型薄膜トランジスタである。

(もっと読む)

半導体素子の製造方法

本発明は、リソグラフィ工程を経たフォトレジストの特性を変化させてダミー構造物を形成し、これをゲート電極形成工程に適用した半導体素子の製造方法に関することで、半導体基板上の最上部にバッファー層を形成するステップと、前記バッファー層の上部に無機物フォトレジストを塗布してリソグラフィを通じてフォトレジストパターンを形成するステップと、前記形成されたパターンに特定ガスを使用して熱処理を行うステップと、前記熱処理された構造物の上部に均一な厚さの絶縁膜を蒸着した後に前記パターンが露出されるように前記蒸着された膜をエッチングするステップと、前記工程を経た構造物に絶縁膜を蒸着し、前記パターンが露出されるように前記絶縁膜をエッチングするステップと、前記露出されたパターンを除去するステップと、前記パターンが除去された位置にゲート酸化膜を形成するステップと、前記形成されたゲート酸化膜の上部にゲート電極を形成するステップと、を含む。本発明によれば、ナノ素子を製作するための構造を形成する時、リソグラフィを通じて形成された膜の特性が後続熱処理を通じて改善されるので、多様な素子を製作するための構造を容易に形成することができる。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】電気回路の製造において、液滴吐出装置を用いて微細な配線などを形成する場合、吐出位置や吐出タイミングなどを含めて、より高い精度の吐出制御が要求されている。

【解決手段】CADツールを用いて電気回路の設計図面データを作成した後、その設計図面データを水平方向のドット間隔Xdpと垂直方向のドット間隔Ydpを1つの単位とする正方格子の第1ラスタデータに変換し、さらに水平方向のドット間隔Xdpとドット間隔Ydp/V(V>1)とを1つの単位とする長方格子の第2ラスタデータを作成する。なお、第1ラスタデータから第2ラスタデータに変換する前後で同じ任意吐出回数とする。

(もっと読む)

マルチプル・ゲート・トランジスタを有する電圧制御発振器及びそのための方法

電圧制御発振器(VCO)(40)は、複数の直列接続されたインバータ(42,44,46)を有する。各インバータ内で、第1のトランジスタ(48)は、第1の電源電圧端子(VDD)に結合された第1の制御電極と、第2の制御電極と、複数の直列接続されたインバータのうちの別のインバータの出力端子に結合された第1の制御電極と、第1のバイアス信号を受け取る第2の制御電極とを有する。第2のトランジスタ(50)は、第1のトランジスタの第2の電流電極に結合された第1の電流電極と、第2の電源電圧端子(VSS)に結合された第2の電流電極と、第1のトランジスタの第1の制御電極に結合された第1の制御電極とを有する。各インバータの第1のトランジスタの第2の制御電極は、同じ又は別個のアナログ制御信号(VGP,VPP又はDNP)を受け取って、その第1のトランジスタのスレッショルド電圧を調整して、VCOの信号の周波数及び位相に影響を与える。  (もっと読む)

(もっと読む)

レーザ照射装置、レーザ照射方法、及び半導体装置の作製方法

【課題】CWレーザを半導体膜上に相対的に走査させながら照射すると、走査方向に延びた長い結晶粒が形成される。このようにして形成された半導体膜は、走査方向において単結晶に近い特性のものとなる。しかしながら、CWレーザの干渉性が高いため、均一なレーザ照射を行うのが難しい。

【解決手段】レーザと、前記レーザから射出されるレーザビームを照射面またはその近傍にて楕円または長方形状のビームに加工する手段と、前記レーザビームに対して前記照射面を相対的に移動させる手段と、前記照射面の移動方向の単位ベクトルと前記照射面に対する前記レーザビームの入射方向の単位ベクトルとの内積を一定とする手段とを有する。

(もっと読む)

半導体装置の作製方法

【課題】信頼性を向上させた半導体装置の作製方法の提供を課題とする。

【解決手段】基板上に第1の導電層を形成する工程と、第1の導電層上に、金、銀または銅の導電性粒子(導電性微粒子ともよぶ)と樹脂を含む第2の導電層を形成する工程と、第2の導電層にレーザービームを照射して、前記第1の導電層と前記第2の導電層が接する面積(部分)を増加させる工程とを含む半導体装置の作製方法を提供する。レーザービームを照射する工程を含むことにより、第1の導電層上に、導電性粒子と樹脂からなる第2の導電層を形成した場合でも、第1の導電層と第2の導電層が接する部分を増加させ、第1の導電層と第2の導電層の間の電気的な接続不良を改善することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】バリア性を向上させ、小型化、薄型化および軽量化を実現させ、フレキシブル性をもたせた半導体装置の提供を課題とする。

【解決手段】一対の基板の内側の空間に複数のトランジスタを含む積層体を設けることにより、有害な物質の侵入を抑制し、バリア性を向上させた半導体装置を提供する。また、研削研磨を行うことによって薄膜化した一対の基板を用いることにより、小型化、薄型化、軽量化を実現した半導体装置を提供する。また、フレキシブル性をもたせ、高付加価値化を実現した半導体装置を提供する。

(もっと読む)

141 - 160 / 196

[ Back to top ]