Fターム[5F110EE27]の内容

Fターム[5F110EE27]の下位に属するFターム

Fターム[5F110EE27]に分類される特許

101 - 120 / 196

半導体装置

【課題】 小型であり、順方向と逆方向の双方で導通可能(スイッチング可能)な半導体装置を提供する。

【解決手段】 第1導電型の第1領域30と、第2導電型であり、第1領域30に接している第2領域32と、第1導電型であり、第2領域32によって第1領域から分離されている第3領域36と、第2導電型であり、第3領域36によって第2領域32から分離されている第4領域22と、第1導電型であり、第4領域22によって第3領域36から分離されている第5領域20と、第1領域30及び第2領域34と導通している第1電極56と、第4領域22及び第5領域20と導通している第2電極54と、第2領域32に対して絶縁膜42を介して対向している第1ゲート電極44と、第4領域22に対して絶縁膜50を介して対向している第2ゲート電極52を備えていることを特徴とする半導体装置。

(もっと読む)

記憶素子及び記憶素子の作製方法

【課題】低電圧で書き込み、読み出しを行うことができる、消費電力の小さい安価な記憶素子と、その製造方法を提供する。

【解決手段】絶縁性基板100上の第1の導電体101上に、0.1μm以上10μm以下の大きさの導電性を有する粒子、溶媒及び樹脂を含む導電性ペースト102を配置し、溶媒を気化させて導電性ペースト102中に含まれる導電性を有する粒子103同士を接触させ、導電性ペースト102の導電性を向上させる。一方、第1の導電体101と導電性を有する粒子103の間には、薄い樹脂の層105が残存し、樹脂の層105は、電圧印加によって絶縁破壊させることが可能である。そのため、樹脂の層105は、メモリ層として機能させることが可能である。このように、メモリ層を有する第2の導電体106を形成することができる。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の生産性を低下させることなく、半導体層の特性を向上し、半導体層の面内ばらつきを抑制し、半導体層の特性を均一にすることを目的の一とする。

【解決手段】単結晶半導体基板の一表面にイオンを照射して、該単結晶半導体基板中に損傷領域を形成し、単結晶半導体基板の一表面上に絶縁層を形成し、絶縁表面を有する基板の表面と絶縁層の表面とを接触させて、絶縁表面を有する基板と単結晶半導体基板とを貼り合わせ、加熱処理を施すことにより、損傷領域において単結晶半導体基板を分離して絶縁表面を有する基板上に半導体層を形成し、半導体層の一表面に、半導体層を溶融させない条件でフラッシュランプからの光を照射して、欠陥を修復させる。

(もっと読む)

半導体装置の作製方法

【課題】薄型化及び小型化を達成しながら、外部ストレス、及び静電気放電に耐性を有する信頼性の高い半導体装置を提供することを目的の一とする。また、作製工程においても外部ストレス、又は静電気放電に起因する形状や特性の不良を防ぎ、歩留まり良く半導体装置を作製することを目的の一とする。さらに低コストで生産性高く半導体装置を作製することを目的の一とする。

【解決手段】半導体集積回路を囲いこむように覆う導電性遮蔽体により、半導体集積回路の静電気放電による静電気破壊(回路の誤動作や半導体素子の損傷)を防止する。導電性遮蔽体はめっき法により電気的に接続するように形成する。また、導電性遮蔽体の形成にめっき法を用いるために、低コストで生産性高く半導体装置を作製することができる。

(もっと読む)

半導体装置

【課題】薄型化及び小型化を達成しながら、外部ストレス、及び静電気放電に耐性を有する信頼性の高い半導体装置を提供することを目的の一とする。または、作製工程においても外部ストレス、又は静電気放電に起因する形状や特性の不良を防ぎ、歩留まり良く半導体装置を作製することを目的の一とする。

【解決手段】互いに対向するように設けられた第1の絶縁体及び第2の絶縁体と、対向する第1の絶縁体と第2の絶縁体との間に設けられた半導体集積回路及びアンテナと、第1の絶縁体の一表面に設けられた導電性遮蔽体と、第2の絶縁体の一表面に設けられた導電性遮蔽体とを設け、第1の絶縁体の一表面に設けられた導電性遮蔽体と、第2の絶縁体の一表面に設けられた導電性遮蔽体を電気的に接続する。

(もっと読む)

不揮発性半導体記憶装置及びその作製方法

【課題】書き込みや消去を繰り返し行った場合であっても、読み出し不良を抑制することを目的の一とする。又は、メモリトランジスタの面積の増大を抑制しつつ、書き込み電圧、消去電圧を低減することを目的の一とする。

【解決手段】基板上に設けられた書き込み動作及び消去動作に用いる第1の半導体層及び読み出し動作に用いる第2の半導体層上に、絶縁膜を介してフローティングゲートとコントロールゲートを設け、第1の半導体層を用いてフローティングゲートへの電子の注入・放出を行い、第2の半導体層を用いて読み出しを行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセル面積を増加することなく、メモリトランジスタの書き込み電圧および消去電圧を低減する不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルには、第1の島状半導体領域102、フローティングゲート109、コントロールゲート111が有するメモリトランジスタが設けられている。さらに、フローティングゲート109の下方には、絶縁膜を介して第2の島状半導体領域101が形成されている。第2の島状半導体領域101は、コントロールゲート111に電気的に接続されているため、第2の島状半導体領域101とフローティングゲート109間に静電容量が形成される。この静電容量はメモリトランジスタのカップリング比の増加に寄与するため、メモリセルの面積を増加することなく、カップリング比を高くすることが可能になる。また、カップリング比を低下することなく、メモリセルの面積を縮小することが可能になる。

(もっと読む)

半導体基板の作製方法及び半導体装置

【課題】高性能な半導体素子を形成することを可能とする半導体基板および半導体装置の作製方法を提供する。

【解決手段】脆化層を有する単結晶半導体基板と、ベース基板とを絶縁層を介して貼り合わせ、熱処理によって、脆化層を境として単結晶半導体基板を分離して、ベース基板上に単結晶半導体層を固定する。次いで、モニタ基板の複数の領域に対して互いに異なるエネルギー密度条件でレーザ光を照射し、レーザ光を照射後の単結晶半導体層のそれぞれの領域の炭素濃度及び水素濃度の深さ方向の濃度分布を測定し、炭素濃度が極大を有し、且つ水素濃度がショルダーピークを有するレーザ光の照射強度を最適なレーザ光の照射強度とする。モニタ基板を用いて検出した最適のエネルギー密度で、単結晶半導体層にレーザ光を照射し、半導体基板を作製する。

(もっと読む)

半導体装置の駆動方法

【課題】トランジスタのしきい値電圧のばらつき及び移動度のばらつきを低減する半導体装置の駆動方法を提供することを課題とする。

【解決手段】トランジスタと、トランジスタのゲートに電気的に接続された容量素子とを有し、トランジスタのしきい値電圧に応じた電圧と映像信号電圧との和の電圧に応じて容量素子に保持された電荷を、一度トランジスタを介して放電させることで、トランジスタに流れる電流のばらつき、またはトランジスタの移動度のばらつきを低減する。

(もっと読む)

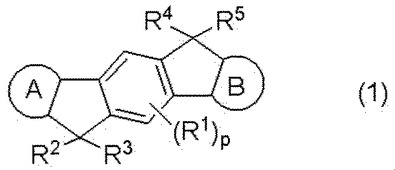

有機半導体材料

【課題】有機半導体材料となりうる化合物を提供すること。

【解決手段】下記一般式(1)で表されるジヒドロインダセン化合物。

(式中、環構造A、Bは、同一又は相異なり、置換されていてもよいベンゼン環、置換されていてもよいチオフェン環等を表す。)

(もっと読む)

SOI基板の作製方法

【課題】単結晶半導体層と半導体基板との密着性を向上させ、貼り合わせ不良を低減し、貼り合わせ工程及び半導体装置製造工程においても十分な接着強度をもつSOI基板の作製方法を提供することを目的とする。

【解決手段】脆化層を形成する単結晶半導体基板側にハロゲンを含む絶縁膜を形成し、該ハロゲンを含む絶縁膜に対してプラズマ処理を行い、ハロゲンを含む絶縁膜と半導体基板の一方の面とが向かい合うようにボンディング(接着)させ、熱処理を行うことにより、脆化層において単結晶半導体基板を分割して、単結晶半導体層が接着された半導体基板と単結晶半導体基板とに分離し、半導体基板に接着された単結晶半導体層に対して平坦化処理を行う。

(もっと読む)

半導体基板の製造方法

【課題】半導体基板における半導体層表面の平坦性を向上させることを目的の一とする。又は、半導体基板の生産性を向上させることを目的の一とする。

【解決手段】単結晶半導体基板の一表面にイオンを照射して損傷領域を形成し、単結晶半導体基板の一表面上に絶縁層を形成し、絶縁表面を有する基板の表面と絶縁層の表面とを接触させて、絶縁表面を有する基板と単結晶半導体基板とを貼り合わせ、加熱処理を施すことにより、損傷領域において単結晶半導体基板を分離して絶縁表面を有する基板上に単結晶半導体層を形成し、単結晶半導体層をパターニングして複数の島状半導体層を形成し、島状半導体層の一に、該島状半導体層の全面を覆うように成形されたレーザ光を照射する。

(もっと読む)

縮合多環芳香族化合物のシート状結晶を基板上に積層することを含む新規有機半導体薄膜の製造方法、及び液状分散体

【課題】常温ウェットプロセスによる高いキャリア移動度を発現する有機半導体薄膜の製造方法、及当該方法により製造された有機半導体薄膜を有する半導体素子の提供。

【解決手段】以下のステップ:

有機半導体材料である縮合多環芳香族化合物のシート状結晶を液状媒体に分散して分散体を形成し;

得られた分散体を基板上にトランスファした後、前記液状媒体を、80℃以下の温度で、前記縮合多環芳香族化合物の溶液の形成を経由せずに、前記分散体から除去して、前記基板上に、前記縮合多環芳香族化合物のシート状結晶を積層する;

を含む、基板上への有機半導体薄膜の製造方法。

(もっと読む)

有機発光トランジスタ

【課題】複数のゲートを有する有機発光トランジスタの構造をより簡素化すること。

【解決手段】基板(1)と、基板上に配置された第1ゲート電極(2)と、基板上に、第1ゲート電極と離間して配置された第2ゲート電極(3)と、第1ゲート電極及び第2ゲート電極の少なくとも一部を覆い、基板上に配置されたゲート絶縁膜(4)と、ゲート絶縁膜上に配置された第1ソース/ドレイン電極(5)と、第1ソース/ドレイン電極の少なくとも一部を覆い、かつ第1ゲート電極及び第2ゲート電極の各々と重畳してゲート絶縁膜上に配置された第1有機半導体層(6)と、第1有機半導体層上に配置された第2ソース/ドレイン電極と、第2ソース/ドレイン電極の少なくとも一部を覆い、かつ第1ゲート電極及び第2ゲート電極の各々と重畳して第1有機半導体層上に配置された第2有機半導体層(8)と、を備える有機発光トランジスタである。

(もっと読む)

半導体記憶装置及びその製造方法と半導体記憶装置の動作方法

【課題】書込み速度の向上と、かつ読出しディスターブの抑制を両立させることが可能な半導体記憶装置を提供する。

【解決手段】半導体層上に電荷蓄積膜とゲート電極105を形成し、ゲート電極105の下部に形成されたチャネル領域の両側の半導体層に2つの第1導電型の拡散領域A及びBを形成する。チャネル領域は、一方の拡散領域Aが接する側のチャネル幅Waよりも他方の拡散領域Bが接する側のチャネル幅Wbの方が大きく形成される。記憶動作時には一方の拡散領域Aへ他方の拡散領域Bよりも高い電圧を印加し、読出し時には他方の拡散領域Bへ一方の拡散領域Aよりも高い電圧を印加する。

(もっと読む)

半導体装置の作製方法、半導体装置及び電子機器

【課題】耐熱性の低い基板をベース基板とするSOI基板で、レーザ光で表面を溶融させることにより、機械的な研磨が不要な半導体装置を提供する。

【解決手段】ベース基板101、絶縁層116、接合層114、半導体層115を有するSOI基板に、レーザー光122を照射することにより半導体層115上面を溶融させ、冷却、固化することで、機械的な研磨を行わなくても、平坦性が優れたSOI半導体装置を提供できる。また、レーザー光の端部が照射された領域の半導体層は半導体素子として用いずに、レーザー光の端部以外が照射された領域の半導体層を半導体素子として用いることにより、半導体装置の性能を大きく向上することができる。

(もっと読む)

電気光学装置、電子機器、電気光学装置の製造方法

【課題】不揮発性メモリと画素TFTが同一基板上に併設されており、かつ高信頼性とされた液晶装置を提供する。

【解決手段】本発明の電気光学装置は、画素部と、これを駆動させる駆動回路と、不揮発性メモリと、を備えた電気光学装置である。画素部及び前記駆動回路の少なくとも一方におけるスイッチング素子は、不揮発性メモリとともに基板10A上に形成されている。スイッチング素子のゲート絶縁膜は、第1絶縁膜35と第2絶縁膜36と第3絶縁膜38との積層構造からなっており、不揮発性メモリは、第2絶縁膜36を介して半導体層33上に設けられたフローティングゲート電極37と、第3絶縁膜38を介してフローティングゲート電極37上に設けられたコントロールゲート電極39Aと、を有するメモリセル110aを備えている。

(もっと読む)

半導体装置、及びその作製方法

【課題】半導体基板(SOI基板)の大面積化を課題とする。また、効率のよい半導体基板の作製方法を提案することを課題とする。また、上記の半導体基板の特性を向上することを課題とする。また、上記の半導体基板を用いた半導体装置及び電子機器を提供することを課題とする。

【解決手段】半導体基板(SOI基板)の大面積化及び作製効率の向上を図るために、複数の単結晶半導体基板を同時に処理して、半導体基板を作製する。具体的には、複数の単結晶半導体基板の処理を同時に可能とするトレイを用いて、一連の工程を行う。また、ベース基板に形成した単結晶半導体層に対してエッチング処理又はエッチバック処理を施すことにより、単結晶半導体層に存在する損傷領域を除去すると共に、隣接する単結晶半導体層の間隙におけるベース基板の表面の一部を除去して、ベース基板に凹部を形成する。

(もっと読む)

半導体装置、およびその作製方法

【課題】ばらつきを抑え、かつ、製造歩留まりの高い半導体装置を作製することを課題とする。

【解決手段】

絶縁表面を有する基板上に、チャネル形成領域が非単結晶半導体層で形成される薄膜トランジスタを有し、前記非単結晶半導体層は、厚さが5nm以上50nm以下であり、一方向に略平行に延びる結晶粒界を含み、該結晶粒界の間隔は10nm以上、500nm以下であることを特徴とする、半導体装置及びその作製方法を提供する。

(もっと読む)

半導体装置

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に複数の電界効果トランジスタがそれぞれ層間絶縁層を介して積層している半導体装置とする。複数の電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は層間絶縁層上にそれぞれ設けられた絶縁層に接して接合されている。複数の電界効果トランジスタはそれぞれ前記半導体層に歪みを与える絶縁膜で覆われている。

(もっと読む)

101 - 120 / 196

[ Back to top ]