Fターム[5F110EE27]の内容

Fターム[5F110EE27]の下位に属するFターム

Fターム[5F110EE27]に分類される特許

161 - 180 / 196

半導体装置の作製方法

【課題】基板上に半導体素子を設けた後に当該基板を薄膜化または除去した場合であっても、外部からの不純物元素や水分等の侵入による半導体素子への影響を抑制する半導体装置の作製方法を提供することを目的とする。

【解決手段】基板に表面処理を行い基板の一方の面に保護膜として機能する絶縁膜を形成し、絶縁膜上に薄膜トランジスタ等の半導体素子を形成し、基板を薄膜化することを特徴としている。表面処理としては、基板に不純物元素の添加やプラズマ処理を行う。基板を薄膜化する手段としては、基板の他方の面から研削処理または研磨処理等を行うことによって基板を部分的に除去することによって行うことができる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】電界効果トランジスタにおけるパンチスルーとリーク電流の抑制をはかることができ、素子信頼性の向上をはかる。

【解決手段】表面部にチャネル領域が形成される第1導電型の第1の半導体領域100と、チャネル領域上にゲート絶縁膜101を介して形成されたゲート電極102と、チャネル領域を挟んで形成されたソース・ドレイン電極108と、ソース・ドレイン電極108とチャネル領域との間に形成され、ソース・ドレインのエクステンション領域となる第2導電型の第2の半導体領域105と、ソース・ドレイン電極108と第1,第2の半導体領域100,105との間に形成され、第2の半導体領域105よりも不純物濃度の高い第2導電型の第3の半導体領域109とを備えた電界効果トランジスタであり、第3の半導体領域109はソース・ドレイン電極108からの偏析によって形成されている。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】 FETデバイスにおける閾値電圧をより良く制御できるデバイスを提供すること。

【解決手段】 基板(101)と、基板(101)の上のシリコン・ゲルマニウム(SiGe)層(103)と、SiGe層(103)の上の、SiGe層(103)に隣接した半導体層(105)と、基板(101)、SiGe層(103)及び半導体層(105)に隣接した絶縁層(109a)と、絶縁層(109a)に隣接した一対の第1のゲート構造体(111)と、絶縁層(109a)の上の第2のゲート構造体(113)とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層(109a)は、SiGe層(103)の側面、並びに半導体層(105)の上面、半導体層(105)の下面及び半導体(105)の側面に隣接していることが好ましい。SiGe層(103)は、炭素を含むことが好ましい。一対の第1のゲート構造体(111)が、第2のゲート構造体(113)に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体(111)の対は、絶縁層(109a)によりカプセル封入されることが好ましい。

(もっと読む)

薄膜トランジスタの製造方法

【課題】薄膜トランジスタにおいて、しきい値電圧を高めに設定しなくてもトランジスタがオフ時のリーク電流を抑え、薄膜トランジスタの駆動能力の低下を防止する。

【解決手段】アモルファスシリコン膜2をレーザーアニール等の加熱処理により、結晶化してポリシリコン膜3を形成する。そして、薄膜トランジスタのしきい値電圧を制御するため、不純物をポリシリコン膜3の中にイオン注入する。その後、ポリシリコン膜3を選択的にドライエッチングまたはウエットエッチングしてポリシリコン・アイランド3Iを形成する。このとき、ポリシリコン・アイランド3Iの端部がテーパー形状となるように等方性エッチングの条件でエッチングを行う。

(もっと読む)

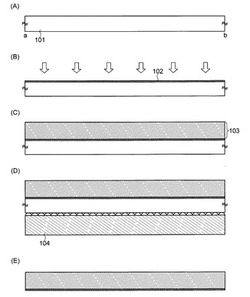

半導体装置の作製方法及び半導体装置

【課題】低コストで信頼性が高く、薄膜化された半導体装置の作製方法、及びその方法によって作製された半導体装置を提供する。

【解決手段】基板上に剥離層を形成し、剥離層上にトランジスタを形成し、トランジスタ上に絶縁層を形成した後、剥離層の一部を露出させる開口部を形成し、基板からトランジスタを物理的手段により剥離する。ここで、剥離層の形成は、基板上に金属膜を形成し、溶液を用いる方法でその金属膜上に接して金属酸化膜を形成することによって行われる。

(もっと読む)

半導体装置の作製方法

【課題】耐熱性の低い基板にも低抵抗のTiシリサイド層を形成することを課題とする。

【解決手段】Tiシリサイド層の加熱処理工程にレーザー光を用いることで、耐熱性の低い基板上にも低抵抗のTiシリサイド層を形成することができる。シリコンを含む半導体膜に接してTi膜を成膜し、第一の加熱処理により高抵抗のTiシリサイド層を形成し、レーザー照射を用いた第二の加熱処理により、高抵抗のTiシリサイド層を低抵抗のTiシリサイド層にする。本発明によりTiシリサイド層を形成するために高温で加熱処理する必要がないため、基板を制限なく用いることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】大量生産が可能で、従来のガラス基板や単結晶シリコン基板とは異なり、低コストでかつ非常に厚さの薄い薄膜集積回路、及び該薄膜集積回路を用いた薄膜集積回路装置又はICチップの構造、プロセスを提供することを目的としている。

【解決手段】シリコン基板の一表面上に第1の絶縁膜を形成し、前記第1の絶縁膜上に少なくとも2つ以上の薄膜集積回路を有する層を形成し、前記薄膜集積回路を有する層を覆うように樹脂層を形成し、前記樹脂層を覆うようにフィルムを形成し、前記シリコン基板の前記薄膜集積回路を有する層を形成した一表面の裏面を研削し、前記シリコン基板の研削した面を研磨する。

(もっと読む)

高トポグラフィ・パターニング方法

【課題】次の処理を簡単にすることができる均一なパターン密度が得られ、アクティブ・パターニング・リソグラフィについての緩和要求が得られる高トポグラフィ・パターニング方法を提供する。

【解決手段】半導体材料の構造分離方法は、少なくとも一つの高架線(elevated line)を含む半導体材料のパターンを設けるステップと、前記パターン内に前記少なくとも一つの高架線を少なくとも含むデバイス領域を画成するステップと、前記デバイス領域の外側の前記半導体材料の導電性を変化させ、前記デバイス領域を電気的に分離するステップとを含む。

(もっと読む)

半導体装置

【課題】 従来例に比して、短チャネル効果を抑制し、かつ移動度を向上させるSOI構造のp型MOS-FETによる半導体装置を提供する。

【解決手段】 本発明の半導体装置は、p型MOS-FETであり、半導体基板と、該半導体表面に形成された絶縁層と、該絶縁層表面に形成され、素子形成領域を有する半導体層と、該半導体層に形成されたチャネル部ならびにソース及びドレインと、前記チャネル部上にゲート絶縁膜を介して形成されたゲート電極とを有し、前記チャネル部のゲート電極と対向するチャネル形成面が(110)面方位である。

(もっと読む)

薄膜トランジスタの作製方法及び薄膜トランジスタ

【課題】実質的なチャネル長の長さを短くし、半導体装置を微細化することができる半導体装置及びその作製方法を提供する。また、実質的なチャネル長の長さを短くすることによってゲート容量を減少させることができ、半導体装置の高速動作及び高性能化を実現できる半導体装置及び、その作製方法を提供する。また、製造工程を簡略化することができる作製方法を提供することを課題とする。

【解決手段】絶縁表面を有する基板上に形成されたる島状半導体膜と、島状半導体膜上に形成されたゲート電極とを有する半導体装置であって、ゲート電極は高密度プラズマにより表面を酸化されることによって、スリミング化し、実質的なチャネル長を短くしている。

(もっと読む)

電界変調型単電子トランジスタ

【課題】単電子トランジスタが、より安定した状態でより高温で動作できるようにする。

【解決手段】ソース103,細線部105,及びドレイン104が配列された第1方向に対して垂直な第2方向の細線部105の寸法は、ソース103及びドレイン104の第2方向の寸法より小さくされ、ゲート電極107は、細線部105の第2方向の側に配置され、ゲート電極107の側において、細線部105はソース103及びドレイン104より凹んで配置されている。なお、基板101は、細線部105に対し、第1方向に対して垂直な第3方向の側に配置されている。

(もっと読む)

記憶素子マトリックス及びその製造方法

【課題】

本発明は、高密度な、fin型FETを用いたDRAMの記憶素子を行列状態に敷きつめた記憶素子マトリックスの構造及びその製造方法を提供することを目的とする。

【解決手段】

上記を解決するため、絶縁支持基板上の孤立した半導体領域と、半導体領域に形成されている記憶素子と、共通線とを備える記憶素子マトリックスを提供する。そして、その記憶素子は、ソース領域と、ドレイン領域と、半導体領域の第1側面に、ゲート絶縁膜を介し、配設された前面ゲート電極と、半導体領域の前記第1側面に対向する第2側面に、ゲート絶縁膜を介し、配設された背面ゲート電極とを備えている。また、共通線は、前記絶縁支持基板中の溝に埋め込まれており、前記記憶素子マトリックスの辺方向に平行して延在し、辺方向に並べられた各前記記憶素子の前記前面ゲート電極と前記背面ゲート電極の内、少なくとも、一方を、辺方向にそって接続することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】透明導電膜とエッチングガスが反応して細かいパーティクルが形成されるのを防ぎ、良好な特性を持つ半導体装置を作製することを課題とする。

【解決手段】透明導電膜を形成し、前記透明導電膜上に第1の導電膜を形成し、前記第1の導電膜上に第2の導電膜を形成し、前記第2の導電膜を、塩素を含むガスでエッチングし、前記第1の導電膜を、フッ素を含むガスでエッチングすることを特徴とする半導体装置の作製方法に関するものである。塩素を含むガスで第2の導電膜をエッチングする際には、第1の導電膜により透明導電膜が保護され、フッ素を含むガスで第1の導電膜をエッチングする際には、透明導電膜とフッ素を含むガスは反応しないので、パーティクルが形成されない。

(もっと読む)

半導体装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】粗面を有する層を形成し、粗面上に導電性材料を含む組成物に対するぬれ性の低い領域と、組成物に対するぬれ性の高い領域を形成し、ぬれ性の高い領域に前記組成物を用いて導電層を形成する。ぬれ性が大きく異なる領域(ぬれ性に大きく差を有する領域)を形成できるので、液状の導電性材料又は絶縁性材料が、被形成領域のみに正確に付着する。よって、所望のパターンに正確に導電層、絶縁層を形成することができる

(もっと読む)

デバイス計算方法

【課題】 短い時間で計算できるため実践性が高く、かつ、キャリア速度のオーバーシュートを高い精度で計算できるデバイスの計算方法を提供する。

【解決手段】1次元ポアソン方程式に併せて、5つの多重加速流定義をまとめた図8中のすべての式(流速の式と境界条件の式も含む)を用いることによって、半導体デバイス内部の電気的特性並びに電気的特性分布を推定する。

(もっと読む)

表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な表示装置の作製方法を提供する。更には、少ない原料でコスト削減が可能であり、且つ歩留まりが高い表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒元素を有する層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】 大面積のガラス基板上に薄膜からなる集積回路を形成した後、基板から剥離を行い、接触、好ましくは非接触でデータの受信または送信が可能な微小なデバイスを大量に効率よく作製する方法を提供することを課題とする。特に薄膜からなる集積回路は、非常に薄いため、搬送時に飛んでしまう恐れがあり、取り扱いが難しかった。

【解決手段】

本発明は、分離層に対して少なくとも異なる2種類の方法を用いてダメージ(レーザ光照射によるダメージ、エッチングによるダメージ、または物理的手段によるダメージ)を複数回与えることにより、基板から被剥離層を効率よく剥離する。また、剥離後のデバイスに反りを持たせることによって、個々のデバイスの取り扱いを容易とする。

(もっと読む)

共振トランジスタ及び通信装置

【課題】 本発明は、微小共振器を用いて、高周波化で、高SN比化、高いパワー化を可能にした共振トランジスタ、より具体的にはビーム型共振バルクトランジスタ及びビーム型共振薄膜トランジスタを提供するものである。

【解決手段】 本発明の共振トランジスタ1は、ドレイン領域4とソース領域2とチャネル領域3を有すると共に、前記チャネル領域3上に空間16を介して対向するゲート振動子5を有し、前記ゲート振動子5の共振によって前記ドレイン領域4に流れるドレイン電流が交流変化することを特徴とする。

(もっと読む)

表示装置の作製方法

【課題】 本発明は、材料の利用効率を向上させ、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する表示装置の作製方法を提供する。

【解決手段】 本発明は、非晶質半導体膜に触媒元素を添加し加熱して、結晶性半導体膜を形成するとともに該結晶性半導体膜から触媒元素を除き、その後逆スタガ型薄膜トランジスタを作製する。また本発明は、薄膜トランジスタのゲート電極層と画素電極層を同工程同材料を用いて液滴吐出法により選択的に形成し、工程の簡略化と、材料のロスの軽減を達成する。

(もっと読む)

表示装置及びその作製方法、並びにテレビジョン装置

【課題】 本発明は、材料の利用効率を向上させ、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する表示装置の作製方法を提供する。

【解決手段】 本発明は、非晶質半導体膜に触媒元素を添加し加熱して、結晶性半導体膜を形成するとともに該結晶性半導体膜から触媒元素を除き、その後逆スタガ型薄膜トランジスタを作製する。また本発明は、薄膜トランジスタのゲート電極層と画素電極層を同工程同材料を用いて形成し、工程の簡略化と、材料のロスの軽減を達成する。

(もっと読む)

161 - 180 / 196

[ Back to top ]