Fターム[5F110EE27]の内容

Fターム[5F110EE27]の下位に属するFターム

Fターム[5F110EE27]に分類される特許

41 - 60 / 196

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、少なくとも酸化物半導体膜中に希ガスイオンを注入する注入工程を行い、減圧下、窒素雰囲気下、又は希ガス雰囲気下において、希ガスイオンを注入した酸化物半導体膜に加熱工程を行って希ガスイオンを注入した酸化物半導体膜中に含まれる水素若しくは水を放出させ、酸化物半導体膜を高純度化する。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

半導体装置、モジュール及び電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、上層と、上層よりも広い幅を有する下層とからなる2層構造とする。TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。上層の端面から突出させた下層部分と、ITOとを接合させる。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】オフ電流が低減できる半導体装置及び半導体装置を提供する。

【解決手段】絶縁表面上に形成され、ソース領域、ドレイン領域、及びチャネル形成領域を含む単結晶半導体層と、単結晶半導体層を覆うゲート絶縁膜と、ゲート絶縁膜を介して、チャネル形成領域に重畳するゲート電極と、ソース領域に接続されるソース電極と、ドレイン領域に接続されるドレイン電極と、を有し、ソース領域及びドレイン領域のうち、少なくともドレイン領域は、チャネル形成領域に隣接する第1の不純物領域と、第1の不純物領域に隣接する第2の不純物領域と、を含み、第1の不純物領域の深さ方向の不純物濃度分布の極大は、第2の不純物領域の深さ方向の不純物濃度分布の極大よりも絶縁表面側にあり、ドレイン電極は、ドレイン領域に含まれる第2の不純物領域の一部と接続する半導体装置を提供する。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジ

スタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁

層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化

物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トラ

ンジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極

層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソ

ース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレ

イン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジ

スタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁

層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化

物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トラ

ンジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極

層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソ

ース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレ

イン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

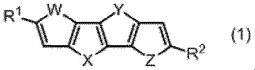

置換カルコゲノアセン化合物及び該化合物を含有する有機半導体デバイス

【課題】有機半導体デバイスに用いることのできる置換カルコゲノアセン化合物を提供するとともに、該化合物を用いた、キャリア電界効果移動度が十分な有機半導体デバイスを提供する。

【解決手段】式(1)で表される置換カルコゲノアセン化合物。

(式中、

W、X、Y及びZは、酸素原子、硫黄原子、セレン原子又はテルル原子を表す。

R1及びR2は、炭素数1〜30のフッ素原子を有していてもよいアルキル基、炭素数1〜30のフッ素原子を有していてもよいアルコキシ基、炭素数1〜30のフッ素原子を有していてもよいアルキルチオ基、炭素数2〜30のフッ素原子を有していてもよいアルキニル基、炭素数7〜36のフッ素原子を有していてもよいアリール基又は炭素数5〜34のフッ素原子を有していてもよいヘテロアリール基を表す。)

(もっと読む)

半導体装置及びトランジスタの駆動方法

【課題】光照射されてトランジスタの電気特性が変動した場合でも、その電気特性をほぼ光照射前の状態にする手法を提供する。

【解決手段】酸化物半導体を用いたトランジスタのゲート電極に、正のバイアス電圧を10msec以上印加することにより、光照射されて変動した当該トランジスタの電気特性をほぼ光照射前の状態にすることが可能になる。なお、当該トランジスタのゲート電極に対する正のバイアス電圧印加は、当該トランジスタが受光する光量を参照して適切なタイミングで行う。これより光照射されても表示品位の低下が抑制された表示装置を実現することができる。

(もっと読む)

発光表示装置及び発光表示装置の作製方法

【課題】薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製する方法を提供する。

【解決手段】剥離層を介して基板上に素子領域を形成する際に、半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行う。更に素子領域を基板から剥離して、じん性の高い第1の支持体に設け、第1の支持体及びじん性の高い第2の支持体で液晶素子を挟持することで、薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製できる。

(もっと読む)

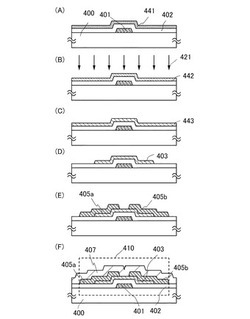

発光表示装置の作製方法

【課題】トランジスタの作製工程を簡略化し、フォトマスクの枚数を従来よりも少なくするだけでなく、新たな工程を増やすことなく発光表示装置を作製することを目的とする。

【解決手段】トランジスタを構成する半導体層に真性または実質的に真性な高抵抗の酸化物半導体を使用することによって、個々のトランジスタに対して半導体層を島状に加工する工程を省くことができる。半導体層または半導体層の上層に形成した絶縁層を開口する工程において該半導体層の不要な部分を同時にエッチングし、フォトリソグラフィ工程を削減する。

(もっと読む)

発光表示装置の作製方法

【課題】トランジスタの作製工程を簡略化し、フォトマスクの枚数を従来よりも少なくするだけでなく、新たな工程を増やすことなく発光表示装置を作製することを目的とする。

【解決手段】トランジスタを構成する半導体層に真性または実質的に真性な高抵抗の酸化物半導体を使用することによって、個々のトランジスタに対して半導体層を島状に加工する工程を省くことができる。半導体層の上層に形成した絶縁層を開口する工程において該半導体層の不要な部分を同時にエッチングし、フォトリソグラフィ工程を削減する。

(もっと読む)

半導体基板の作製方法、及び半導体装置の作製方法

【課題】絶縁表面に欠陥の少ない単結晶半導体膜を有する半導体基板の、簡便な作製方法を提供することを課題の一つとする。また、歩留まりの良い半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】単結晶半導体基板の表面に絶縁層を形成し、絶縁層をエッチングしながら、絶縁層を介して単結晶半導体基板にイオン照射を行うことで、脆化領域を形成し、単結晶半導体基板の表面に接合層を形成し、単結晶半導体基板と、支持基板とを、接合層を介して貼り合わせ、熱処理を行うことにより、脆化領域内に劈開面を形成して、単結晶半導体基板の一部を分離する、半導体基板の作製方法を提供する。

(もっと読む)

半導体装置及び表示装置

【課題】直流変換回路を有する半導体装置の消費電力を低減することを課題の一とする。

【解決手段】直流変換回路と、マイクロプロセッサとを有し、直流変換回路は、変換回路と、制御回路とを有し、変換回路は、誘導素子と、トランジスタとを有し、制御回路は、比較回路と、論理回路とを有し、比較回路としてヒステリシスコンパレータを用い、制御回路では、比較回路が変換回路の出力信号と第1の基準電位又は第2の基準電位とを比較し、論理回路が比較回路の出力信号とマイクロプロセッサのクロック信号とを演算し、変換回路では、トランジスタが論理回路の出力信号に応じて誘導素子に流れる電流を制御し、誘導素子に流れる電流に応じて変換回路の出力信号を生成する。

(もっと読む)

41 - 60 / 196

[ Back to top ]