Fターム[5F110EE27]の内容

Fターム[5F110EE27]の下位に属するFターム

Fターム[5F110EE27]に分類される特許

81 - 100 / 196

SOI基板の作製方法およびSOI基板

【課題】ベース基板(例えばガラス基板)と半導体基板(例えば単結晶シリコン基板)とを貼り合わせてSOI基板を作製する際の半導体層(例えば単結晶シリコン層)の表面の荒れを抑制することを目的の一とする。

【解決手段】溝部が設けられた半導体基板に、イオンを照射して半導体基板中に脆化領域を形成し、絶縁層を介して半導体基板とベース基板を貼り合わせると共に、半導体基板の溝部とベース基板とにより囲まれた空間を形成し、熱処理を施すことにより、脆化領域において半導体基板を分離して、ベース基板上に絶縁層を介して半導体層を形成する。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置を低消費電力化又は長寿命化すること。

【解決手段】当該半導体装置は、電力供給源となる電池と、特定の回路とがチャネル形成領域が酸化物半導体によって構成されるトランジスタを介して電気的に接続することによって解決することができる。当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該半導体装置の待機時の消費電力を低減することができる。また、これにより当該半導体装置を長寿命化することができる。

(もっと読む)

変調回路及びそれを備えた半導体装置

【課題】変調回路の消費電力を低減する。

【解決手段】変調回路は、負荷と、スイッチとして機能するトランジスタとを有し、前記トランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有し、前記トランジスタのオフ電流は、1×10−13A以下である。または、変調回路は、負荷と、スイッチとして機能するトランジスタと、ダイオードとを有し、前記負荷、前記トランジスタ、及び前記ダイオードは、アンテナの両端間に直列に接続されており、前記トランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有し、前記トランジスタのオフ電流は、1×10−13A以下である。また、前記トランジスタのゲートに入力される信号により、当該トランジスタの導通・非導通が制御される。また、前記負荷は、抵抗、容量、または抵抗及び容量である。

(もっと読む)

スパッタリングターゲットおよびその製造方法、並びにトランジスタ

【課題】酸化物半導体膜を成膜する成膜技術を提供することを課題の一とする。

【解決手段】金属酸化物の焼結体を含み、その金属酸化物の焼結体の含有水素濃度が、たとえば、1×1016atoms/cm3未満と低いスパッタリングターゲットを用いて酸化物半導体膜を形成することで、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物の含有量が少ない酸化物半導体膜を成膜する。また、この酸化物半導体膜をトランジスタの活性層として適用する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】不対結合手に代表される欠陥を多く含む絶縁層を、酸素過剰な混合領域、又は酸素過剰な酸化物絶縁層を間に介して、酸化物半導体層上に形成し、酸化物半導体層に含まれる水素や水分(水素原子や、H2Oなど水素原子を含む化合物)などの不純物を、酸素過剰な混合領域、又は酸素過剰な酸化物絶縁層を通過させて欠陥を含む絶縁層に拡散させ、上記酸化物半導体層中の不純物濃度を低減する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】フッ素や塩素に代表されるハロゲン元素により、酸化物半導体層に含まれる水素や水分(水素原子や、H2Oなど水素原子を含む化合物)などの不純物を、酸化物半導体層より排除し、上記酸化物半導体層中の不純物濃度を低減する。ハロゲン元素は酸化物半導体層と接して設けられるゲート絶縁層及び/又は絶縁層に含ませて形成することができ、またハロゲン元素を含むガス雰囲気下でのプラズマ処理によって酸化物半導体層に付着させてもよい。

(もっと読む)

電子書籍

【課題】安定した電気的特性を有する薄膜トランジスタを有する表示パネルを供えた電子書籍を提供する。また、画像の保持特性の高い電子書籍を提供する。また、高解像度の電子書籍を提供する。また、消費電力の低い電子書籍を提供する。

【解決手段】酸化物半導体中で電子供与体(ドナー)となる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル形成領域が形成される薄膜トランジスタによって、電子書籍の表示パネルの表示を制御するものである。

(もっと読む)

半導体装置およびその作製方法

【課題】LSIやCPUやメモリに用いるトランジスタのリーク電流及び寄生容量を低減することを課題の一とする。

【解決手段】酸化物半導体中で電子供与体(ドナー)となる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル領域が形成される薄膜トランジスタを用い、LSIやCPUやメモリなどの半導体集積回路を作製する。水素濃度が十分に低減されて高純度化された酸化物半導体層を用いる薄膜トランジスタは、リーク電流による消費電力の少ない半導体装置を実現できる。

(もっと読む)

論理回路及び半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を出力信号として出力する構成とする。

(もっと読む)

トランジスタ,面状素子およびこれらの製造方法

【課題】トランジスタを比較的低温で製造する。

【解決手段】下部ゲート絶縁膜44をコントロールゲート42を構成する金属(アルミニウム)の酸化物により形成された下部酸化物層44aと自己組織化単分子膜により形成された下部SAM層44bとにより構成し、上部ゲート絶縁膜48をフローティングゲート46を構成する金属(アルミニウム)の酸化物により形成された上部酸化物層48aと自己組織化単分子膜により形成された上部SAM層48bとにより構成した。これにより、メモリセル40を比較的低温で製造することができる。

(もっと読む)

有機FETアレイ

【課題】pチャネルとnチャネルに共通の有機半導体層とソース、ドレイン電極材料の好適な組合せにより、実用上十分に良好な伝達特性を得ることが可能な有機FETアレイを提供する。

【解決手段】有機半導体層を用いたpチャネル電界効果トランジスタ(p型有機FET)と、有機半導体層を用いたnチャネル電界効果トランジスタ(n型有機FET)とを備えた有機FETアレイ。有機半導体層5はpチャネルとnチャネルに共通の材料の有機半導体単結晶により形成される。p型有機FETのソース及びドレイン電極は、仕事関数に基づいて制御される有機半導体層中の多数キャリアが正孔になるように選択されたpチャネル金属電極6により形成され、n型有機FETのソース及びドレイン電極は、仕事関数に基づいて制御される有機半導体層中の多数キャリアが電子になるように選択されたnチャネル金属電極7により形成される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に画素と駆動回路が設けられ、駆動回路の第1の薄膜トランジスタ及び画素の第2の薄膜トランジスタは、ゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、ゲート絶縁層、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸化物半導体層の一部と接する酸化物絶縁層と、を有し、第2の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、及び酸化物絶縁層は透光性を有し、第1の薄膜トランジスタのソース電極層及びドレイン電極層は、第2の薄膜トランジスタのソース電極層及びドレイン電極層と材料が異なり、第2の薄膜トランジスタのソース電極層及びドレイン電極層よりも低抵抗である。

(もっと読む)

窒化物系半導体電界効果トランジスタ

【課題】ノーマリオフ動作を達成し、十分なチャネル電流が得られ、かつ、しきい値電圧制御が容易な窒化物系半導体ヘテロ接合電界効果トランジスタを提供する。

【解決手段】GaN層10とAlGaN層11のヘテロ接合界面をチャネルとする電界効果トランジスタにおいて、負の電荷を有する第三の層40をゲート電極34下のゲート絶縁膜31中に設けるとともに、ヘテロ接合を形成する窒化物半導体内にフッ素イオンF−等の負のイオン41を注入する。第三の層40はCl−等の負のイオンが注入される。ゲート絶縁膜31中およびAlGaN層11中に適量の負のイオンを注入することにより、しきい値電圧が上がりノーマリオフ動作を確実に達成するとともに、十分なチャネル電流が得られる。

(もっと読む)

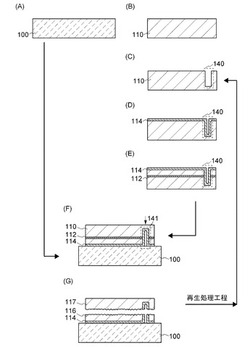

SOI基板の作製方法

【課題】単結晶シリコン基板よりも大面積な基板に、均一な質を有する複数の単結晶半導体層を貼り付けたSOI基板の作製方法を提供することを課題とする。

【解決手段】熱処理において、ベース基板支持及び単結晶半導体基板保持のトレイとして、凹部の底が深く、ベース基板に貼り付けられた単結晶半導体基板と接触しないトレイを用いて、単結晶半導体基板の熱分布の均一化を図る。また、該トレイの各々の凹部の間にベース基板支持部を設けることによって、該トレイとベース基板との接触面積を低減する。以上より、単結晶半導体基板から単結晶半導体層を分離する熱処理の際、単結晶半導体基板及びベース基板の熱分布が均一になるようにする。

(もっと読む)

SOI基板の作製方法およびSOI基板

【課題】ガラス基板と単結晶半導体基板とを貼り合わせてSOI基板を作製する際のシリコン層の表面の荒れを抑制することを目的の一とする。または、上記荒れを抑えて歩留まりの高い半導体装置を提供することを目的の一とする。

【解決手段】ボンド基板に加速されたイオンを照射して該ボンド基板に脆化領域を形成し、ボンド基板またはベース基板の表面に絶縁層を形成し、絶縁層を介してボンド基板とベース基板を貼り合わせると共に、ボンド基板とベース基板の一部に貼り合わない領域を形成し、熱処理を施すことにより、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成する。

(もっと読む)

フラットパネルX線イメージャ内のフォトダイオード及び他のセンサ構造、並びに薄膜電子工学を利用したフラットパネルX線イメージャ内のフォトダイオード及び他のセンサ構造のトポロジー均一性の改善方法

【解決手段】

電離放射線との相互作用で光子を放射するように構成されたシンチレーション層と、第1電極、光電性層、及びシンチレーション層の近傍に配置された光子透過性の第2電極を順番に含む光検出器とを有する放射線センサである。光電性層は、光子の一部との相互作用で電子正孔対を生成するように構成される。放射線センサは、第1電極に電気的に接続され、かつ光電性層内で生成された電子正孔対を示す撮像信号を測定するように構成された画素回路と、第1電極と画素回路の間において、画素回路上に、画素回路を含む平面の上方に第1電極が位置するように配置された平坦化層とを有する。第1電極と第2電極の少なくとも一方の電極の表面は、画素回路に少なくとも部分的に重なり、画素回路のフィーチャの上方に面屈曲を有する。面屈曲は、2分の1ミクロンを超える曲率半径を有する。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

表示装置

【課題】 簡易な構成で画素の開口率の向上と補助容量の確保とが実現できる表示装置を提供する。

【解決手段】 n行m列(n及びmは、それぞれ2以上の整数を表す。)のマトリクス状に配列された画素電極と、略格子状に設けられたn本のソースライン及びm本のゲートラインとを有する薄膜トランジスタアレイ基板を備えた表示装置であって、上記ゲートラインは、奇数行の画素電極と偶数行の画素電極との間に、奇数行用のゲートライン及び偶数行用のゲートラインがともに配置され、基板面に対して法線方向から見たときに、上記奇数行用のゲートラインと上記偶数行用のゲートラインと重なる領域にシールド電極を更に有し、上記シールド電極と上記画素電極とは電気的に分離されている表示装置である。

(もっと読む)

電気化学装置

【課題】大量生産可能の電気化学トランジスタを提供する。

【解決手段】電気化学トランジスタ装置は、ソース接点1と、ドレイン接点2と、少なくとも1つのゲート電極4と、ソース、ドレイン接点間に配置されており、それらと直接的に電気接触している電気化学的にアクティブな要素であるトランジスタ・チャネル3を含み、そのレドックス状態の変化を通じてその導電率を電気化学的に変える能力を有する有機材料からなる材料で作られている電気化学的にアクティブな要素と、電気化学的にアクティブな要素および前記少なくとも1つのゲート電極の間に介在し、それらと直接的に電気接触している凝固電解液5とを含み、電気化学的にアクティブな要素、前記ゲート電極間の電子流が阻止されるようになっている。この装置において、ソース接点およびドレイン接点間の電子の流れは、前記ゲート電極に印加された電圧によって制御可能である。

(もっと読む)

双方向ESDパワークランプ

【課題】 エリアの消費が少ない双方向ESDパワークランプを提供する。

【解決手段】 本発明は、第1のノードと第2のノードとの間に接続された導電性経路と、導電性経路をトリガすることができるトリガノードとを有する半導体構造(大きいNFET、大きいPFET)を備える双方向ESDパワークランプに関する。ESD過渡検出回路は、第1のノードと第2のノードとの間に接続され、かつトリガノードに接続され、かつ第1のノードでの第1のESD過渡の発生を検出する第1の部分(10乃至17)を備える。半導体構造は、絶縁体基板上に提供されて、基板を介した上記第1のノードと上記第2のノードとの間の寄生導電性経路が回避される。ESD過渡検出回路はさらに、第2のノードでの第2のESD過渡の発生を検出する第2の部分(M1,M2)を備える。

(もっと読む)

81 - 100 / 196

[ Back to top ]