Fターム[5F110EE31]の内容

Fターム[5F110EE31]の下位に属するFターム

堆積によるもの (1,135)

電極表面を酸化したもの (189)

Fターム[5F110EE31]に分類される特許

841 - 856 / 856

高さが異なる隆起したドレインおよびソース領域を有するトランジスタを形成するための先進技術

極めて小型の半導体デバイスにおけるエピタキシャル成長させた半導体領域の高さは、2つ以上のエピタキシャル成長を実行しうる異なるデバイス領域に対して、個別に調節することができる。エピタキシャル成長マスクは、特定のデバイス領域における半導体領域の形成を選択的に抑制する。他の実施形態において、2つ以上の異なるデバイス領域に対して、一般的なエピタキシャル成長プロセスを用いてもよく、選択されたエリアにあるすでにエピタキシャル成長させた半導体領域の高さを正確に低減するように、引き続き、選択されたデバイス領域に選択的酸化プロセスを実行することができる。  (もっと読む)

(もっと読む)

Si:CおよびSiGeエピタキシャル成長ソース/ドレインを用いた高性能で応力が向上されたMOSFETおよび製造方法

【課題】 半導体デバイスおよび半導体デバイスの製造方法を提供する。

【解決手段】 半導体デバイスはpFETおよびnFETのためのチャネルを含む。SiGe層はpFETチャネルのソースおよびドレイン領域に選択的に成長され、Si:C層はnFETチャネルのソースおよびドレイン領域に選択的に成長される。SiGe層およびSi:C層は、下に位置するSi層の格子ネットワークに一致して応力成分を生成する。1つの実施形態では、これによって、pFETチャネルでは圧縮成分が引き起こされ、nFETでは引張成分が引き起こされる。

(もっと読む)

高性能の歪みCMOSデバイス

【課題】 デバイス内の酸化に起因する圧縮応力を防止するために界面に覆い被さる浅いトレンチ分離領域(STI)を有する相補型金属酸化物半導体(CMOS)デバイスを提供すること。

【解決手段】 この半導体デバイス及び製造方法は、電流の流れの方向に平行な方向及び電流の流れに対し横方向に、Si−SiO2界面に覆い被さる張出し部を備えた浅いトレンチ分離領域を有するn型チャネル電界効果トランジスタ(n型FET)を提供する。また、このデバイス及び方法は、電流の流れに対し横方向に、Si−SiO2界面に覆い被さる張出し部を備えた浅いトレンチ分離領域を有するp型チャネル電界効果トランジスタ(p型FET)を提供する。しかしながら、p型FETの浅いトレンチ分離領域は、電流の流れの方向に平行な方向には張出し部を備えない。

(もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

CMOS電界効果トランジスタを製造するための方法及び装置

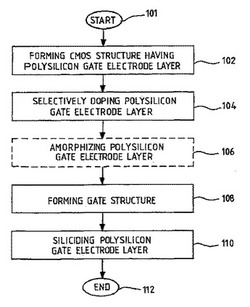

【課題】 集積回路の製造におけるCMOS電界効果トランジスタを製造するための改善された方法、及び、トランジスタの金属ゲートの仕事関数を制御するための改善された方法を提供すること。

【解決手段】 トランジスタのゲート電極を含むポリシリコン材料を選択的にドープするステップと、完全にシリサイド化するステップとを含む、相補型金属酸化膜半導体(CMOS)電界効果トランジスタを製造する方法である。一実施形態において、シリサイド化する前に、ポリシリコンがアモルファス化される。更に別の実施形態において、シリサイド化が、低い基板温度で実行される。

(もっと読む)

ダブルゲート電界効果トランジスタ装置を製造する方法、及びそのようなダブルゲート電界効果トランジスタ装置

本発明は、ダブルゲート電界効果トランジスタ装置を製造する方法、及び本方法により形成されるような装置を開示する。セミコンダクタ・オン・インシュレータ基板から開始し、第1のゲート、ソース、ドレイン、及びエクステンションを形成し、第2のゲートを形成する。次に、基板が第2の担体に接合され、半導体層の第2のサイドを露出させる。次に、アニーリングステップが、無拡散アニーリングとして実行される。当該無拡散アニーリングステップには、半導体層が、おおむね一様な厚さを有するだけでなく、おおむね平坦な表面を有する、という利点がある。これによって、前記アニーリングステップについて、実現可能な中で最良のアニーリング作用が確保される。ドーパントの非常に高度な活性化によって、エクステンションの非常にシャープな急峻性が達成される。  (もっと読む)

(もっと読む)

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

窒化シリコン酸化物ゲート誘電体を製造する方法

【課題】 ウェハ内における相対的に均一な厚さ及び窒素濃度を有するSiOxNy層を製造する方法を提供すること。

【解決手段】 基板を準備するステップと、該基板の上面に二酸化シリコン層を形成するステップと、還元雰囲気内でプラズマ窒化を実行し、該二酸化シリコン層を酸窒化シリコン層に変換するステップとを含む、ゲート誘電体層を製造する方法である。このように形成された誘電体層を、MOSFETの製造において用いることができる。

(もっと読む)

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

ゲートの枯渇を低減した注入ゲート電極を有する電界効果型トランジスタ、及び、このトランジスタを製造する方法

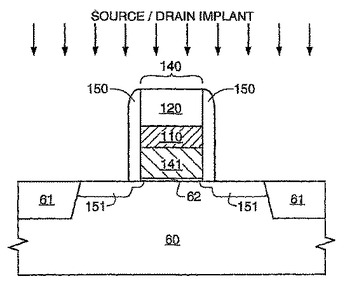

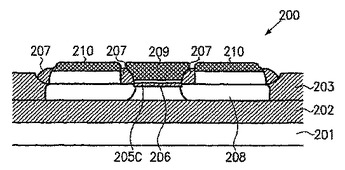

ドレイン領域及びソース領域(208)を規定する前に、注入マスク(220)を形成することにより、ゲートドーパント密度をドレインドーパント密度及びゲートドーパント密度から効果的に分離する。さらに、注入マスク(220)を除去した後に、ゲート電極(205)の横方向寸法は、十分に確立された側壁スペーサ(207)技術によって規定される。その結果、フォトリソグラフィ及び異方性エッチングに基づく従来の方法に対してデバイスの縮小に関する優位性を提供する。  (もっと読む)

(もっと読む)

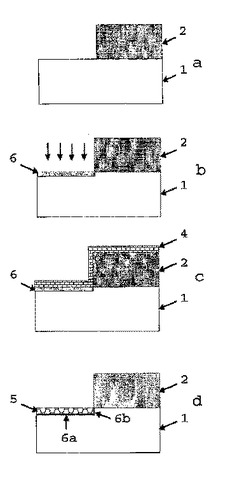

接点の製作方法とその接点を持つ電子部品

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

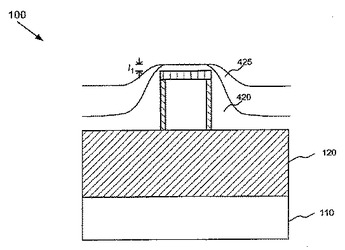

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

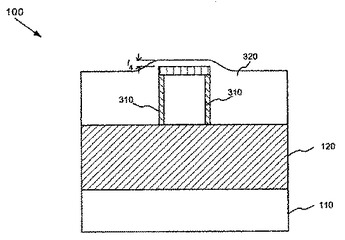

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

841 - 856 / 856

[ Back to top ]