Fターム[5F110EE31]の内容

Fターム[5F110EE31]の下位に属するFターム

堆積によるもの (1,135)

電極表面を酸化したもの (189)

Fターム[5F110EE31]に分類される特許

161 - 180 / 856

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】しきい値電圧を制御しやすく、信頼性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、支持基板(Si基板1)、絶縁層(埋め込み絶縁膜2)および、SOI層(極薄Si層3)が順に積層してなる基板と、極薄Si層3上の少なくとも一部に設けられたトランジスタと、を備え、トランジスタの直下の極薄Si層3が、空乏化しており、埋め込み絶縁膜2と極薄Si層3との間の界面に、界面準位生成不純物が位置しており、界面の界面準位生成不純物の濃度は、埋め込み絶縁膜2中の界面準位生成不純物の濃度より高い。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極(またはドレイン電極)と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタとして、しきい値電圧を正に制御したトランジスタを用いることで、読み出し電位を正の電位とする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位変換回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

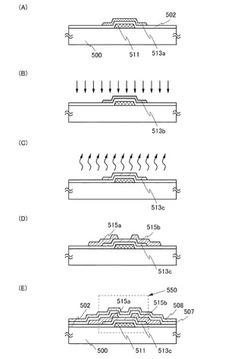

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタは、半導体特性を示す金属酸化物により設けられ、下部のトランジスタが有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、該ゲート電極層と同一の層の一部を上部のトランジスタのバックゲートとして機能させる。下部のトランジスタは、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタのソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

薄いBOX金属バックゲート型極薄SOIデバイス

半導体装置の製造方法、電気光学装置、電子機器

【課題】キャリアの移動度が高く、特性ばらつきが少ない半導体装置の製造方法、これを適用した半導体装置を備えた電気光学装置、電子機器を提供すること。

【解決手段】本適用例の半導体装置の製造方法は、基板上に第1多結晶質シリコン膜としての第1半導体層を形成する工程と、第1半導体層上に非結晶質シリコン膜を形成して、該非結晶質シリコン膜に対して、不活性ガス雰囲気中で第1半導体層上における該非結晶質シリコン膜の結晶核発生速度よりも結晶成長速度の方が速くなる温度で熱処理を施して該非結晶質シリコン膜を結晶化して第2多結晶質シリコン膜としての第2半導体層を形成する工程と、第1半導体層および第2半導体層をパターニングして半導体層を形成するエッチング工程と、を備えた。

(もっと読む)

半導体装置及びその作製方法

【課題】高い電気的特性、または、高い信頼性を有する半導体装置、若しくはその作製方法を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極と重なる酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、ゲート電極と酸化物半導体層との間に設けられたゲート絶縁層と、を有し、酸化物半導体層は、対向ターゲット方式を用いたスパッタリング法により成膜され、且つ酸化物半導体層に含まれるキャリア濃度が、1×1012/cm3未満である半導体装置を提供する。

(もっと読む)

半導体装置およびその作製方法

【課題】微小化されたトランジスタはゲート絶縁層の薄膜化を要求されるが、トンネル電流、つまりゲートリーク電流の増加により、ゲート絶縁層が酸化珪素膜の単層である場合はゲート絶縁層の薄膜化には物理的限界が生じつつある。

【解決手段】ゲート絶縁層に比誘電率が10以上のhigh−k膜を用いることで、微小化したトランジスタのゲートリーク電流を低減させる。酸化物半導体層と接する第2の絶縁層よりも比誘電率が高い第1の絶縁層としてhigh−k膜を用いることによって、酸化珪素膜で換算した場合のゲート絶縁層よりもゲート絶縁層の薄膜化ができる。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

半導体装置

【課題】素子が破壊されるほど高い電圧が印加された場合であっても、素子の破壊を抑制する。

【解決手段】第1の電圧が入力されることにより動作を行う半導体装置であって、第1の電圧の絶対値が基準値より大きいとき、第1の電圧の値を変化させる保護回路を具備し、保護回路は、第1の電圧に応じて第2の電圧を生成し、生成した第2の電圧を出力する制御信号生成回路と、電圧制御回路と、を備え、電圧制御回路は、ソース、ドレイン、及びゲートを有し、ゲートに制御信号として第2の電圧が入力され、第2の電圧に応じてオン状態又はオフ状態になることにより、第1の電圧の値をソース及びドレインの間に流れる電流量に応じて変化させるか否かを制御するトランジスタを含み、トランジスタは、チャネル形成層としての機能を有する酸化物半導体層をさらに有し、酸化物半導体層のバンドギャップは、2eV以上である。

(もっと読む)

半導体集積装置及び半導体集積装置の製造方法

【目的】耐放射線特性を高めることが可能な半導体集積装置及び半導体集積装置の製造方法を提供することを目的とする。

【構成】半導体支持基板上の絶縁層の上面に形成されているシリコン薄膜層内における上記絶縁層との境界に隣接する境界近傍領域中に、この境界に近いほど不純物の濃度が高くなる領域が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁ゲート型電界効果トランジスタのデバイス特性に変動が生じることやゲート絶縁膜が破壊されるのを抑制または防止できる半導体装置の製造方法を提供する。

【解決手段】絶縁層上に半導体層が形成された基板を準備し、半導体層の表面にアルゴンイオン注入を行い、アルゴンイオン注入後の半導体層上にゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成し、半導体層にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体装置

【課題】消費電力を抑えることができる半導体装置の提供を、目的の一とする。また、信頼性の高いプログラム素子を用いた半導体装置の提供を、目的の一とする。

【解決手段】基本ブロック間の接続構造を変更するのに合わせて、基本ブロックへの電源電圧の供給の有無も変更する。すなわち、基本ブロック間の接続構造を変更することで回路構成に寄与しない基本ブロックが生じた場合に、当該基本ブロックへの電源電圧の供給を停止する。さらに、基本ブロックへの電源電圧の供給を、オフ電流またはリーク電流が極めて小さい酸化物半導体を用いた絶縁ゲート電界効果型トランジスタを用いたプログラム素子によって、制御する。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】ボディー抵抗の低減化を図った部分分離ボディー固定SOI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのソース・ドレイン領域形成時において、N+ブロックレジスト51におけるN+ブロック領域41のゲート方向延長領域41aによって、ゲート方向延長領域41a下のウェル領域11には、N型の不純物が注入されることを回避する。ゲート電極9の長手方向延長線上においてN型の不純物が注入される恐れのあるウェル領域11である高抵抗形成領域を、従来の高抵抗形成領域A1より狭い高抵抗形成領域A2とすることができる。

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

非対称P型電界効果トランジスタおよびこれを形成するための方法

【課題】 ボディタイド非対称P型電界効果トランジスタを提供する。

【解決手段】 本発明の模範的な一実施形態では、非対称P型電界効果トランジスタは、チャネルを介してドレイン領域に結合されたソース領域と、チャネルの少なくとも一部分の上に重なるゲート構造体と、少なくとも部分的にチャネル内に配置されたハロー注入であって、ドレイン領域よりソース領域の近くに配置されたハロー注入と、チャネルに結合されたボディタイとを含む。他の模範的な一実施形態では、非対称P型電界効果トランジスタは対称P型電界効果トランジスタとして作用するように動作可能である。

(もっと読む)

161 - 180 / 856

[ Back to top ]