Fターム[5F110EE31]の内容

Fターム[5F110EE31]の下位に属するFターム

堆積によるもの (1,135)

電極表面を酸化したもの (189)

Fターム[5F110EE31]に分類される特許

101 - 120 / 856

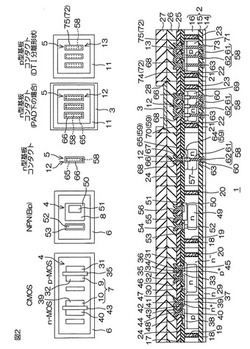

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置の製造方法

【課題】塗布法を用いて形成される酸化膜を溝の内部に充填した溝型の素子分離部を有する半導体装置において、溝の内部におけるボイドの発生を抑制して、埋め込み不良を低減することのできる技術を提供する。

【解決手段】0.2μm以下の溝幅を有する溝4Sの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも高く、かつ1.0μm以上の溝幅を有する溝4Lの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも低くなるように、半導体基板1の主面上にポリシラザン膜を形成し、続いて、300℃以上の熱処理を行うことにより、ポリシラザン膜を酸化シリコン(SiO2)からなる第1埋め込み膜8へ転化すると同時に、溝4Sの上部に局所的に生じたボイドを消滅させる。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置の駆動方法

【課題】新たな構造の半導体装置、及びその駆動方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のpチャネル型トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電荷を保持させることで行う。また、保持期間において、メモリセルを選択状態とし、且つ、読み出し用トランジスタのソース電極およびドレイン電極を同電位とすることで、ノードに蓄積された電荷を保持する。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化金属膜から放出される窒素がゲート絶縁膜に到達することを抑制する。

【解決手段】この半導体装置は、半導体基板100、第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び第1ゲート電極を備えている。第1ゲート絶縁膜110は半導体基板100上に形成されており、酸化シリコン又は酸窒化シリコンよりも比誘電率が高い材料から構成されている。シリコン含有第2ゲート絶縁膜122は、第1ゲート絶縁膜110上に形成されている。第1ゲート電極はシリコン含有第2ゲート絶縁膜122上に形成されており、窒化金属層124を有している。第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び窒化金属層124は、pMOSFETの一部を構成している。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路。特に、短時間の電源停止により消費電力を抑えることができる信号処理回路。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する信号処理回路。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタのLSI製造後にしきい電圧の制御が可能で、かつ、回路面積を増大させず、かつ信頼性に優れるという特徴を有する技術を提供する。

【解決手段】シリコン半導体支持基板1の上面に設けられた積層膜(3nm以上4nm以下の第1のシリコン酸化膜2/0.3nm以上2nm以下のシリコン窒化膜3/5nm以上10nm以下の第2のシリコン酸化膜4/3nm以上20nm以下の膜厚)を有するSOI層5と、上記構造に所定の間隔を介して互いに対向して設けられたソース・ドレイン拡散層6と、当該ソース拡散層とドレイン拡散層の間の上記半導体基板の表面上に形成されたゲート絶縁膜7と、上記ゲート絶縁膜の上に形成されたゲート電極8を具備してなる電界効果型半導体装置において、シリコン支持基板1から電圧を印加することにより、直接トンネル効果によって電荷をシリコン窒化膜3に一定時間保持してしきい電圧を調整する。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

半導体装置の作製方法

【課題】高性能、高信頼性のトランジスタを有する半導体装置を作製する技術を提供する。

【解決手段】配線層を導電層から形成する際に酸化物半導体層を保護するための保護導電膜を酸化物半導体層と導電層との間に形成して、2段階のエッチングを行う。第1のエッチング工程には、保護導電膜は導電層よりエッチングされにくく、導電層と保護導電膜とのエッチング選択比が高い条件で行うエッチング方法を採用し、第2のエッチング工程には、保護導電膜は酸化物半導体層よりエッチングされやすく、保護導電膜と酸化物半導体層とのエッチング選択比が高い条件で行うエッチング方法を採用する。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

101 - 120 / 856

[ Back to top ]