Fターム[5F110EE37]の内容

Fターム[5F110EE37]に分類される特許

1 - 20 / 273

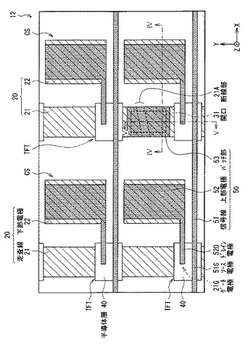

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

液晶表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上を図ることのできる液晶表示装置を提供することを課題の一とする。

【解決手段】画素は、トランジスタと、走査線として機能することができる第1の配線と、信号線として機能することができる第2の配線と、画素電極とを有し、画素は、当該第1の配線と同時に形成された容量線を有さない液晶表示装置である。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

表示装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】映像信号線が絶縁膜を介して走査線を乗り越える構成となっている。走査線10はAlCu合金を下層11とし、MoCr合金を上層12とする2層構造である。上層/下層の膜厚比を、0.4以上、1.0以下とすることによって、走査線10の断面において、電池作用によって上層12のエッチング速度が遅くなって、上層12の庇部が形成されることを防止する。これによって、走査線10に生じた庇部に起因して、映像信号線が走査線10との交差部において断線することを防止する。

(もっと読む)

半導体装置

【課題】チップ面積を増大させずにスナップバック現象を抑制することのできる、IGBTと他の半導体素子とが一体化して配置された半導体装置を提供する。

【解決手段】IGBTとドリフト層を有する他の半導体素子とを備えた半導体装置であって、IGBTのドリフト層と他の半導体素子のドリフト層とが互いに接しており、IGBTのエミッタ層と他の半導体素子のドリフト電界を発生させる電圧が印加される一方の極性層とが互いに導電的に接続されており、IGBTのコレクタ層と他の半導体素子の他方の極性層とが互いに導電的に接続されており、IGBTのドリフト層の他の半導体素子のドリフト層との境界から離れた領域に絶縁層を介して対向する領域をドリフト方向に沿って延伸し、Nチャネル型IGBTではコレクタ側からエミッタ側に向けて電流が流され、Pチャネル型IGBTではエミッタ側からコレクタ側に向けて電流が流される配線部が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

発光装置

【課題】開口率の向上された発光装置である。

【解決手段】薄膜トランジスタと、容量と、発光素子と、発光素子へ電流を供給することができる機能を有する配線とを、プラスチック基板上に有する発光装置であって、配線は、容量の上に設けられ、容量は、配線の少なくとも一部と重なる領域を有する。発光素子は、陰極と、陽極と、陰極と陽極との間に設けられたEL材料とを有し、容量は、第2の領域と、第2の領域上に第1の絶縁膜を介して設けられる第3の領域とを有する。第1の絶縁膜は、薄膜トランジスタのゲート絶縁膜となり、さらに容量の絶縁膜となることができる。

(もっと読む)

電気装置の製造方法、半導体基板の製造方法、電気装置用形成基板、及び電子機器

【課題】静電破壊を防止して歩留まり良く製造できる電気装置の製造方法、半導体基板の製造方法、電気装置用形成基板、及び電子機器を提供する。

【解決手段】支持体上に、樹脂材料からなる基材を複数積層することで第1基板を形成する工程と、素子基板から前記支持体を剥離する工程と、素子基板との間で機能素子を挟持するように第2基板を貼り付ける工程と、を有する電気装置の製造方法に関する。素子基板の形成工程においては、複数の基材間のいずれかに挟持するように電極層を配置するとともに、電極層よりも上層であって複数の前記基材間のいずれかに挟持する或いは基板本体の表面に配置するように機能素子を駆動するための半導体素子を設ける。

(もっと読む)

半導体デバイス及びその製造方法

【課題】グラフェンの特性を生かしつつ、高耐圧デバイスや紫外発光・受光デバイスを実現する。

【解決手段】半導体デバイスを、2次元構造のグラフェン電極2、3と、グラフェン電極のグラフェン端に結合した2次元構造のボロンナイトライド半導体層5とを備えるものとする。

(もっと読む)

半導体装置

【課題】フォトセンサを有する半導体装置において、外光のノイズを軽減し、且つトランジスタのオフ電流によるリークが原因となるノイズも低減する。

【解決手段】マトリクス状に配置された複数のフォトセンサを有する。複数のフォトセンサはそれぞれ、光電変換素子と増幅回路とを有する。バックライトを点灯して被検出物に光を照射して第p行目のフォトセンサでリセット動作及び蓄積動作を行った後、バックライトを非点灯として第(p+1)行目のフォトセンサでリセット動作及び蓄積動作を行い、その後全行のフォトセンサの選択動作を順次行う。隣接する行のフォトセンサで得られた出力信号の差分を取得し、差分を用いて被検出物の撮像画像の生成や被検出物の存在する領域の検出を行う。増幅回路は蓄積された電荷を保持するトランジスタを有し、当該トランジスタはチャネルが酸化物半導体層に形成される。

(もっと読む)

表示装置、液晶表示装置及びプロジェクター

【課題】高開口率な半導体装置を提供する。

【解決手段】絶縁表面上に第1配線と、第1配線上に第1絶縁膜と、第1絶縁膜上に半導体膜と、半導体膜上に第2絶縁膜と、第2絶縁膜上に第2配線と、第1配線と接続するゲート電極と、第2配線及びゲート電極上に第3絶縁膜と、第3絶縁膜上に半導体膜と接続する第3の配線とを有する半導体装置。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

表示装置および電子機器

【課題】配線層を低抵抗に保ち、かつ薄膜トランジスタにおける膜剥がれを防止した表示装置および電子機器を提供する。

【解決手段】基板11上に薄膜トランジスタ10および配線層20を備える。薄膜トランジスタ10は、基板11側からゲート電極12,ゲート絶縁膜13および半導体層14を有し、配線層20は、配線層20aおよび配線層20bにより構成されている。配線層20bとゲート電極12とは同一の膜厚および構成材料からなる。配線層20とゲート電極12との厚みは異なっている。具体的には、ゲート電極12の厚みは配線層20の厚みよりも薄く、ゲート電極12の膜内応力が小さくなっている。

(もっと読む)

液晶表示装置、電子機器

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

表示装置及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を

同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電

極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気

的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成

された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを

介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成

された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的

に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

薄膜トランジスタ液晶ディスプレイのアレイ基板及びその製造方法

【課題】本発明はTFT−LCDアレイ基板及びその製造方法に関する。

【解決手段】本発明はTFT−LCDアレイ基板及びその製造方法に関し、アレイ基板はベース基板と、ベース基板上に形成され画素領域を限定するゲートライン及びデータラインを含み、前記画素領域内には画素電極、薄膜トランジスタと共通電極が形成される。また、導電性薄膜材料により製造されるブラックマトリクスを含み、前記ブラックマトリクスは前記共通電極と接続される。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

1 - 20 / 273

[ Back to top ]