Fターム[5F110EE38]の内容

Fターム[5F110EE38]に分類される特許

521 - 538 / 538

電気光学装置、及び投射型表示装置

【課題】 スイッチング素子の配線平面パターンの簡素化を実現できる電気光学装置、及び投射型表示装置を提供する。

【解決手段】 ソース領域、ドレイン領域、及びチャネル領域を有する半導体層80n、80pと、当該半導体層80n、80pに対向配置されたゲート電極81n、81pと、からなるスイッチング素子70aを備えた電気光学装置であって、ソース領域、ドレイン領域、及びゲート電極のうちの少なくともいずれかは、半導体層80n、80pよりも下層側に設けられた下層配線84に接続されていることを特徴とする。

(もっと読む)

配線基板、薄膜トランジスタ、表示装置及びテレビジョン装置の作製方法

【課題】 本発明は、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置の作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】 本発明の配線基板の作製方法の一は、被処理物を有する第1の領域を形成し、一部の被処理物表面を改質して、第1の領域と境界線を有する第2の領域を形成し、境界線を越えて第1の領域の一部、及び第2の領域に連続的に導電性材料を含む組成物を吐出し、組成物を固化して導電層を形成し、境界線を越えて第1の領域の一部に形成された導電層を除去する。

(もっと読む)

半導体集積回路、及び半導体集積回路の製造方法

【課題】回路面積の小さく、配線長の短い、小型の半導体集積回路を提供する。

【解決手段】多層構造で構成される半導体集積回路であって、第1半導体層と、第1半導体層に形成された第1半導体層トランジスタと、第1半導体層上に堆積され、金属配線が形成された配線層と、配線層上に堆積された第2半導体層と、第2半導体層に形成された第2半導体層トランジスタとを備える。なお、第1半導体層トランジスタのゲート絶縁膜の絶縁性と、第2半導体層トランジスタのゲート絶縁膜の絶縁性とは概ね同等であり、第2半導体層トランジスタのゲート絶縁膜は、ラジカル酸化又はラジカル窒化により形成される。

(もっと読む)

ダブルゲート電界効果トランジスタとして用いられる層構造体、および、その製造方法

【課題】ダブルゲート電界効果トランジスタとして用いられる層構造、および、その製造方法を提供する。

【解決手段】本発明の方法では、補助基板上に、多孔質シリコン層を犠牲層として形成する。この犠牲層の上に第1半導体層、第1電気絶縁層を順次形成する。第1電気絶縁層の上に、導電層を形成し、ラテラルにパターン形成する。ラテラルにパターン形成された導電層を共通のマスクとして用いて、第1電気絶縁層、犠牲層、および、第1半導体層をラテラルにパターン形成する。さらに、パターン形成された犠牲層の側壁とパターン形成された第1半導体層の側壁とに隣接して、半導体部を形成する。基板を、パターン形成された導電層の上方に固定し、補助基板の材料を除去して、犠牲層を露出させる。さらに、犠牲層を選択的に除去することにより、トレンチを形成する。トレンチ中に、第2電気絶縁層を形成し、その上に導電部を形成する。

(もっと読む)

半導体装置

【課題】 高電圧駆動のMISトランジスタを有する半導体装置であって、耐圧の向上と、微細化の向上が図られた半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体層10と、

前記半導体層10の上方に設けられたゲート絶縁層20と、

前記ゲート絶縁層20の上方に設けられたゲート電極22と、

前記半導体層10に設けられたソース領域またはドレイン領域となる不純物領域28a,bと、

前記ゲート電極22と電気的に接続されたフィールドプレート電極44と、

前記フィールドプレート電極44を覆う絶縁層と、を含み、

前記絶縁層は、比誘電率が異なる領域を有し、比誘電率が高い領域は、前記導電層の一の端部に接している。

(もっと読む)

プレーナ型ダブルゲートトランジスタおよびその製造方法

【課題】プレーナ型自己整合ダブルゲートトランジスタを既知の簡単かつコスト効率のよい製造方法で提供する。

【解決手段】SOI基板上に活性領域を規定する工程と、上記SOI基板上に第1ゲート領域206を形成する工程と、上記活性領域の中にシリコンゲルマニウムからなるソース/ドレイン領域を形成する工程と、上記SOI基板のケイ素層からチャネル領域203を形成する工程と、上記SOI基板と、ソース/ドレイン領域と、第1ゲート領域206との上に、平面を有する層311を形成する工程と、上記の平面に酸化ケイ素413が形成されたウェハーを結合する工程と、第1ゲート領域206と向かい合う第2ゲート領域517を形成する工程とを有する。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、半導体装置の製造方法および表示装置

【課題】 トランジスタ特性のバラツキを減少させた薄膜トランジスタの製造方法、薄膜トランジスタ、半導体装置の製造方法および表示装置を得ること。

【解決手段】 基板1上に少なくともソース領域14とチャネル領域16およびドレイン領域15を有する多結晶もしくは結晶化された結晶化半導体薄膜5が設けられ、この結晶化半導体薄膜5上にゲート絶縁膜11を介してゲート電極13が設けられた薄膜トランジスタの製造方法であって、ゲート絶縁膜11は、結晶化半導体薄膜5と略同一平面を形成するように基板1上に樹脂層10を形成したのち、この樹脂層10上および結晶化半導体薄膜5上に形成した膜である。

(もっと読む)

メモリ・ゲイン・セル、メモリ回路、およびゲイン・セルのための構造を形成する方法(水平メモリ・ゲイン・セル)

【課題】メモリ回路用のゲイン・セル、複数のゲイン・セルから形成されたメモリ回路、およびこのようなゲイン・セルおよびメモリ回路を製造する方法を提供する。

【解決手段】メモリ・ゲイン・セル64は、ストレージ・キャパシタ38と、ストレージ・キャパシタに電気的に結合された、ストレージ・キャパシタを充放電するための書込みデバイスと、読取りデバイスとを含む。読取りデバイスは、それぞれがソースおよびドレインの間に電気的に結合された1つまたは複数の半導電性カーボン・ナノチューブ50を含む。読取りゲート60およびストレージ・キャパシタによってそれぞれの半導電性カーボン・ナノチューブの一部がゲートされ、それによって、それぞれの半導電性カーボン・ナノチューブの中をソースからドレインへ流れる電流が調整される。この電流は、ストレージ・キャパシタによって蓄積されている電荷に比例する。

(もっと読む)

電気光学装置及び電子機器、並びに電気光学装置の製造方法

【課題】 電気光学装置において、他の不具合を発生させずに光リーク電流の発生を抑制し、高品位な表示を可能とする。

【解決手段】 基板上に、チャネル領域を有する半導体層を含んで構成された薄膜トランジスタと、薄膜トランジスタにより駆動される表示用電極と、半導体層の上層側及び下層側の少なくとも一方に積層された層間絶縁膜と、該層間絶縁膜の半導体層側とは反対側に積層された、チャネル領域を遮光するための遮光膜とを備えている。層間絶縁膜における半導体層とは反対側の表面には、チャネル領域のうち少なくともチャネル領域の縁部を遮光可能な領域において、半導体層に向かって局所的に窪んだ凹部が形成されている。遮光膜は、少なくとも凹部内に形成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】 高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつ液晶表示装置を提供する。

【解決手段】 ゲート電極106と異なる層に走査線102を形成し、容量配線107が信号線109と平行になるよう配置する。各画素はそれぞれ独立した容量配線107に誘電体を介して接続されているため隣接画素の書き込み電流による容量配線電位の変動を回避でき、良好な表示画像を得る事ができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極の幅方向における実効ゲート長Leffは一定となって、デバイスの性能の向上した半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置は、支持基板11と、前記支持基板上に設けられた絶縁膜12と、前記絶縁膜上に設けられ、第1の方向において互いに対向する第1の側面と、前記第1の方向と直交する第2の方向において互いに対向する第2の側面とを有する直方体状のシリコン島24と、前記シリコン島の上面に設けられた絶縁層14と、互いに対向する前記第1の側面に設けられたゲート絶縁膜17と、前記絶縁膜上に設けられ、前記ゲート絶縁膜を介して前記第1の方向に延在するように設けられたゲート電極21と、前記第1の方向に延在する前記ゲート電極の両側壁に設けられた側壁スペーサ23と、前記第2の側面にそれぞれ設けられたソース・ドレイン領域25、26と、前記第2の側面にそれぞれ設けられ、前記ソース・ドレイン領域とそれぞれ接続されるソース及びドレイン電極とから構成される。

(もっと読む)

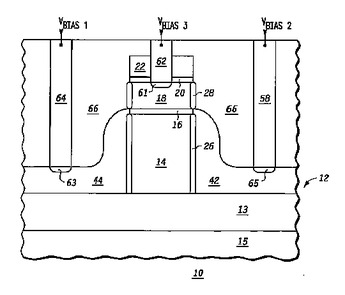

2つの制御領域を有する集積された電界効果トランジスタ、その使用、およびその製造方法

本発明は、特に、SOI技術およびサリサイド技術により、ダブルゲート・トランジスタ(10)として生成される、電界効果トランジスタ(10)に関する。トランジスタ(10)は、5ボルトよりも高いまたは9ボルトよりもさらに高いターンオン電圧に適し、非常に小さなチップ表面のみを必要とする。トランジスタ(10)は基板領域(14)を有する。基板領域(14)は、2つの電極領域(16、18)と、2つの電気的に絶縁性の絶縁層(100、102)であって、基板領域(14)の対向する面に配置され、制御領域(20、22)に隣接する、絶縁層と、少なくとも1つの電気的に絶縁性の領域(12、110)と、導電性の接続領域(28)、または、1つの電極領域(16)と該基板領域(14)との間の導電性の接続領域の部分(230)とに囲まれる。  (もっと読む)

(もっと読む)

複数の狭区画レイアウトを用いたひずみデバイス

大きな引張応力を有する半導体デバイスを提供することを目的とする。半導体デバイスは、ソース領域及びドレイン領域を備える基板を有する。ソース領域及びドレイン領域の各々は、それぞれ、複数の分離されたソース区画及びドレイン区画を含む。シャロートレンチ分離(STI)領域がソース領域の2つの分離されたソース区画間及びドレイン領域の2つの分離されたドレイン区画間に形成される。ゲート積層体が基板に形成される。引張誘起層が基板上に形成される。引張誘起層はSTI領域、ソース領域、ドレイン領域及びゲート積層体を覆っている。引張誘起層は基板に引張応力を生じさせることが可能な絶縁体である。

(もっと読む)

(もっと読む)

垂直型FIN−FETMOSデバイス

【課題】 トランジスタ本体として働く垂直方向のシリコン「フィン」を用いて、低い接触抵抗を持つ高密度の垂直型Fin−FETデバイスを生成すること。

【解決手段】 低い接触抵抗を示す新しいクラスの高密度の垂直型Fin−FETデバイスが説明される。これらの垂直型Fin−FETデバイスは、トランジスタ本体として働く垂直方向のシリコン「フィン」(12A)を有する。ドープされたソース領域及びドレイン領域(26A、28A)が、それぞれフィン(12A)の下部及び上部内に形成される。ゲート(24A、24B)が、フィンの側壁に沿って形成される。適切なバイアスがゲート(24A、24B)に印加されると、電流は、ソース領域(26A)とドレイン領域(28A)との間で、フィン(12A)を通して垂直方向に流れる。pFET、nFET、マルチ・フィン、シングル・フィン、マルチ・ゲート、及びダブルゲートの垂直型Fin−FETを同時に形成するための統合プロセスが説明される。

(もっと読む)

相補的窒化膜トランジスタの垂直およびコモンドレイン

【課題】少ない材料で、電流搬送能力に優れた半導体デバイスを提供する。

【解決手段】 異なる平面に、オーミック接点を含む半導体デバイス、およびそのデバイスを製造するための方法であって、連続したステップで、異なる導電タイプの半導体層の半導体スタックをエッチングし、第1半導体層内に、第1の幅の第1開口部を形成し、別の半導体層を露出させ、次に別の層内に、より狭い幅の第2開口部を形成し、オーミック接点を収容するための別の層の一部を、露出した状態で残すことを含む。

(もっと読む)

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

521 - 538 / 538

[ Back to top ]