Fターム[5F110EE38]の内容

Fターム[5F110EE38]に分類される特許

81 - 100 / 538

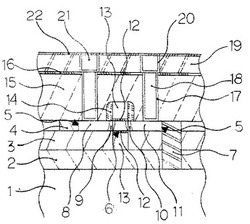

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

薄膜トランジスタ

【課題】寄生容量を小さくでき、応答速度低下を抑制することが可能なTFTを提供する。

【解決手段】基材110上に配設した有機半導体層150と、有機半導体層150と接触し、対向してチャネル領域を形成するソース電極120及びドレイン電極130と、有機半導体層150と絶縁層160を介して設けられるゲート電極140と、ソース電極120と導電接続するソース電極配線部125と、ドレイン電極130と導電接続するドレイン電極配線部135と、ゲート電極140と導電接続するゲート電極配線部145と、からなるTFT100であって、積層方向からみて、有機半導体層150が、ゲート電極140を含み、ゲート電極140が、ソース電極120とドレイン電極130とチャネル領域とからなる領域を含み、有機半導体層150の周縁でソース電極配線部125とドレイン電極配線部135との間にはゲート電極配線部145が配される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワーMISFETを提供する。

【解決手段】半導体層101を挟んでゲート電極102aとソース電極103a、ドレイン電極103bを形成し、半導体層のうちゲート電極102aとドレイン電極103bとの間にこれらが重ならない領域を設ける。この領域の長さを0.5μm乃至5μmとする。このようなパワーMISFETのドレイン電極とソース電極の間に100V以上の電源と負荷を直列に接続し、ゲート電極102aに制御用の信号を入力して使用する。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

半導体装置、パワーダイオード及び整流器

【課題】高耐圧、低逆方向飽和電流、高いオン電流などの電気特性を有する半導体装置を提供することである。なかでも、非線形素子より構成されるパワーダイオード及び整流器を提供することである。

【解決手段】第1の電極と、第1の電極を覆うゲート絶縁層と、ゲート絶縁層と接して且つ第1の電極と重畳する酸化物半導体層と、酸化物半導体層の端部を覆う一対の第2の電極と、一対の第2の電極及び酸化物半導体層を覆う絶縁層と、絶縁層に接して且つ一対の第2の電極の間に設けられる第3の電極と、を有し、一対の第2の電極は酸化物半導体層の端面に接する半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

発光表示装置及び発光表示装置の作製方法

【課題】薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製する方法を提供する。

【解決手段】剥離層を介して基板上に素子領域を形成する際に、半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行う。更に素子領域を基板から剥離して、じん性の高い第1の支持体に設け、第1の支持体及びじん性の高い第2の支持体で液晶素子を挟持することで、薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製できる。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

半導体装置の作製方法

【課題】高性能、高信頼性のトランジスタを有する半導体装置を作製する技術を提供する。

【解決手段】配線層を導電層から形成する際に酸化物半導体層を保護するための保護導電膜を酸化物半導体層と導電層との間に形成して、2段階のエッチングを行う。第1のエッチング工程には、保護導電膜は導電層よりエッチングされにくく、導電層と保護導電膜とのエッチング選択比が高い条件で行うエッチング方法を採用し、第2のエッチング工程には、保護導電膜は酸化物半導体層よりエッチングされやすく、保護導電膜と酸化物半導体層とのエッチング選択比が高い条件で行うエッチング方法を採用する。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

電子機器

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題と

する。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形

成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると

共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導

体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導

電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁

層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体装置及びその作製方法

【課題】電極の表面へのエッチングによるダメージを低減する。

【解決手段】第1の導電層を覆って設けられた第1の絶縁層と、第1の絶縁層上に設けられた第1の半導体層と、第1の半導体層上に、第1の半導体層を露出させて離間して設けられた第2の半導体層と、第2の半導体層上に設けられた不純物半導体層と、不純物半導体層上に、少なくとも一部が接するように設けられた第2の導電層と、第2の導電層上に設けられた第2の絶縁層と、第1の半導体層、第2の半導体層、不純物半導体層、第2の導電層、及び第2の絶縁層を覆って設けられた第3の絶縁層と、少なくとも、第3の絶縁層上に設けられた第3の導電層と、を有し、第1の絶縁層乃至第3の絶縁層に開口部が設けられたデュアルゲート型トランジスタの第1の絶縁層の厚さと第2の絶縁層の厚さを概ね等しいものとする。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

半導体装置及びその作製方法

【課題】デュアルゲート型トランジスタのゲートと、ソースまたはドレインの間の寄生容量を低減する。

【解決手段】第1の導電層を覆って設けられた第1の絶縁層と、第1の絶縁層上に設けられた第1の半導体層と、第1の半導体層上に、第1の半導体層を露出させて離間して設けられた第2の半導体層と、第2の半導体層上に設けられた不純物半導体層と、不純物半導体層上に、少なくとも一部が接するように設けられた第2の導電層と、第2の導電層上に設けられた第2の絶縁層と、第1の半導体層、第2の半導体層、不純物半導体層、第2の導電層、及び第2の絶縁層を覆って設けられた第3の絶縁層と、少なくとも、第3の絶縁層上に設けられた第3の導電層と、を有し、第3の導電層は、第1の半導体層の第2の半導体層と重畳していない部分と重畳し、且つ第2の導電層の一部とも重畳している構造とする。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

多結晶シリコン半導体素子及びその製造方法

【課題】多結晶シリコン半導体素子及びその製造方法を提供する。

【解決手段】ゲート共通化ラインに存在するシリコン物質層による寄生キャパシタンスを減少させるために、製造工程中にゲート以外の他の部分の不要なシリコン物質を除去する。シリコン物質層は、ゲートの下部のみに局地的に存在し、したがって、寄生キャパシタンスの減少によって信号遅延が抑制されて良好な電気的特性を有する薄膜トランジスタの多結晶シリコン半導体素子が得られる。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、基板10と第1絶縁膜11の間に駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、第2絶縁膜12とパッシベーション膜14の間にスイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜6e(5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた半導体装置は、可視光や紫外光を照射することで電気的特性が変化する。このような問題に鑑み、酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】酸化物絶縁層上に膜厚が1nm以上10nm以下の第1の酸化物半導体層を形成し、加熱処理により結晶化させ、第1の結晶性酸化物半導体層を形成し、その上に第1の結晶性酸化物半導体層よりも厚い第2の結晶性酸化物半導体層を形成する。

(もっと読む)

81 - 100 / 538

[ Back to top ]