Fターム[5F110EE38]の内容

Fターム[5F110EE38]に分類される特許

121 - 140 / 538

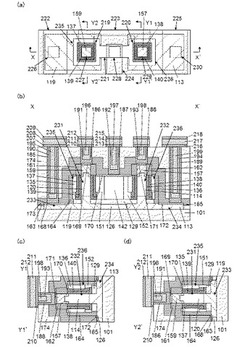

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

垂直型ナノチューブ半導体デバイス構造体の形成方法

【課題】 大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込む垂直型FET構造体を提供する。

【解決手段】 少なくとも1つのナノチューブ14を組み組む垂直型デバイス構造体42を製造する方法である。各々のナノチューブ14は、触媒パッド10によって触媒作用が及ぼされる化学気相成長法によって成長され、誘電体材料22のコーティング内に包み込まれる。包み込まれたナノチューブがゲート電極30の厚さを通って垂直方向に延びるように、該包み込まれたナノチューブの周りにゲート電極を形成することによって、垂直型電界効果トランジスタを作ることができる。包み込まれたナノチューブ、及び該包み込められたナノチューブを支持する対応する触媒パッドが1つのキャパシタ・プレートを形成するように、キャパシタ構造50を作ることができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の長時間にわたる保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第2のトランジスタと、を含む複数のメモリセルと、増幅回路と、スイッチ素子と、を含む読み出し回路と、リフレッシュ制御回路と、を有し、第1のチャネル形成領域と第2のチャネル形成領域は、異なる材料を主成分として構成され、第1のゲート電極と、第2のソース電極および第2のドレイン電極の一方は電気的に接続され、第2のソース電極および第2のドレイン電極の他方と、増幅回路の入力端子の一は電気的に接続され、増幅回路の出力端子は、スイッチ素子を介して第2のソース電極および第2のドレイン電極の他方と接続され、スイッチ素子の導通状態または非導通状態は、リフレッシュ制御回路によって制御される半導体装置である。

(もっと読む)

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

対向電極を有する小型電界効果トランジスタおよび製造方法

【課題】小型化の増進を可能にするとともに、実現が容易な、対向電極を備えた電界効果トランジスタの製造方法を提供する。

【解決手段】ゲート電極9ソースコンタクト12,ドレインコンタクト13、および対向電極コンタクトの輪郭描写パターンを含むエッチングマスクが、セミコンダクタ・オン・インシュレータ型の基板上に形成される。基板は、誘電体5の層およびゲート材料により覆われる。対向電極コンタクトは、ゲート電極9のパターン内に配置される。ゲート材料は、ゲート電極9、ソースコンタクト12およびドレインコンタクト13、ならびに対向電極コンタクトを画定するためにエッチングされる。支持基板2の一部分は、対向電極コンタクト領域のパターンの中を通って解放される。導電性材料22が支持基板2の自由部分上に堆積されて、対向電極コンタクトを形成する。

(もっと読む)

回路基板及び表示装置

【課題】 配線の特性の劣化を生じさせることなく、額縁面積を削減することが可能な回路基板、及び、該回路基板を備える表示装置を提供することを目的とする。

【解決手段】 支持基板上にトランジスタ及び外部接続端子が載置されたトランジスタ基板と、該トランジスタ基板上に取り付けられた外付け部材とを含んで構成される回路基板であって、上記外付け部材は、導電部材を介して外部接続端子と電気的かつ物理的に接続されており、上記トランジスタは、外部接続端子と横並びに配置されている回路基板である。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】低いチャネル抵抗を具現し、電界効果移動度が高くなる効果がある二重ゲートトランジスタを含む半導体装置及びその製造方法を提供する。

【解決手段】本発明による半導体装置は、下部ゲート電極と、前記下部ゲート電極上の上部ゲート電極と、前記下部ゲート電極と前記上部ゲート電極の間に介在され、前記下部ゲート電極と前記上部ゲート電極を連結するコンタクトプラグと、前記上部ゲート電極と同一の高さに前記上部ゲート電極から離隔して形成された機能電極と、を含む。本発明によれば、電界効果移動度が高い二重ゲートトランジスタを半導体装置に適用させることによって、半導体装置の特性を改善することができる。特に、本発明によれば、別途のマスク工程や蒸着工程を追加する必要がないので、工程コストの上昇や収率減少をもたらすことなく、大面積・高画質の半導体装置を大量生産することができる。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置

を提供することを課題の一とする。また、同一基板上に複数種類の薄膜トランジスタの構

造を作製して複数種類の回路を構成し、増加する工程数が少ない半導体装置の作製方法を

提供することを課題の一とする。

【解決手段】絶縁表面上に金属薄膜を成膜した後、酸化物半導体層を積層し、その後、加

熱処理などの酸化処理を行うことで金属薄膜の一部または全部を酸化させる。また、論理

回路などの高速動作を優先する回路と、マトリクス回路とで異なる構造の薄膜トランジス

タを配置する。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置

【課題】フォトセンサにおいて、トランジスタのオフ電流を低減することで、低消費電力化を図ることを目的の一とする。

【解決手段】フォトダイオード、第1のトランジスタ、及び第2のトランジスタを有するフォトセンサと、読み出し制御トランジスタを有する読み出し制御回路と、を有する。フォトダイオードは、入射光に応じた電荷を第1のトランジスタのゲートに供給する機能を有する。第1のトランジスタは、ゲートに供給された電荷を蓄積する機能と、蓄積された電荷を出力信号に変換する機能とを有する。第2のトランジスタは、出力信号の読み出しを制御する機能を有する。読み出し制御トランジスタは、出力信号を電圧値の信号に変換する抵抗素子としての機能を有し、第1のトランジスタ、第2のトランジスタ、及び読み出し制御トランジスタの半導体層は、酸化物半導体を用いて形成されている。

(もっと読む)

半導体装置及びその製造方法、発光装置並びに電子機器

【課題】オン電流特性のばらつきを抑制することができる半導体装置及びその製造方法を提供する。また、良好な画質を有するとともに、製品の歩留まりを向上させることができる発光装置、並びに、該発光装置を実装した電子機器を提供する。

【解決手段】ソース、ドレイン領域となる不純物半導体領域16が、チャネル保護層15を含むマスクを用いたイオンドーピングにより形成され、また、シリサイド領域17が、当該不純物半導体領域16上へのソース、ドレインメタル層の成膜後のアニールにより不純物半導体領域16の活性化と同時に形成される。ソース、ドレイン電極18は、チャネル保護層15からアライメントずれの最大量よりも離間するように配置形成される。また、薄膜トランジスタTFTの形成領域であるデバイスエリアが、上記ソース、ドレイン電極18となるソース、ドレインメタル層18xのパターニング時に同時に画定される。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】成膜中に水素原子を含む不純物と強く結合する物質を成膜室に導入して、成膜室に残留する水素原子を含む不純物と反応せしめ、水素原子を含む安定な物質に変性することで、高純度化された酸化物半導体層を形成する。水素原子を含む安定な物質は酸化物半導体層の金属原子に水素原子を与えることなく排気されるため、水素原子等が酸化物半導体層に取り込まれる現象を防止できる。水素原子を含む不純物と強く結合する物質としては、例えばハロゲン元素を含む物質が好ましい。

(もっと読む)

MEMS及びMEMSの製造方法

【課題】回路構成の設計自由度の高いMEMS及びMEMSの製造方法を提供する。

【解決手段】基板10と、基板10の一方の面側に設けられる第1半導体部21と、基板10の一方の面側に設けられる振動子31と、を備えるMEMSにおいて、第1半導体部21の側面側に設けられ、かつ基板表面に対して略垂直な第1面21aと、振動子31の側面側に設けられ、かつ基板表面に平行な方向において第1面21aと対向する第2面31aが設けられると共に、第2面31a側の表層部分は第1面21a側をゲート電極として電圧が印加された際にチャネルとなることで、第1半導体部21における第1面21aを含む部分と振動子31における第2面31aを含む部分とで電界効果トランジスタが構成されることを特徴とする。

(もっと読む)

121 - 140 / 538

[ Back to top ]