Fターム[5F110EE38]の内容

Fターム[5F110EE38]に分類される特許

141 - 160 / 538

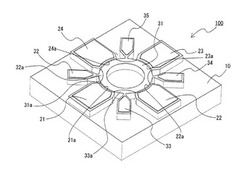

MEMS及びMEMSの製造方法

【課題】回路構成の設計自由度の高いMEMS及びMEMSの製造方法を提供する。

【解決手段】基板10と、基板10の一方の面側に設けられる第1半導体部21と、基板10の一方の面側に設けられる振動子31と、を備えるMEMSにおいて、第1半導体部21の側面側に設けられ、かつ基板表面に対して略垂直な第1面21aと、振動子31の側面側に設けられ、かつ基板表面に平行な方向において第1面21aと対向する第2面31aが設けられると共に、第2面31a側の表層部分は第1面21a側をゲート電極として電圧が印加された際にチャネルとなることで、第1半導体部21における第1面21aを含む部分と振動子31における第2面31aを含む部分とで電界効果トランジスタが構成されることを特徴とする。

(もっと読む)

埋立ビットラインを有する半導体装置及び半導体装置の製造方法

【課題】埋立ビットラインを有する半導体装置及び半導体装置の製造方法を提供すること。

【解決手段】埋立ビットラインを備えて低抵抗を有する垂直ピラートランジスタを含む半導体装置及びその製造方法が開示される。垂直ピラートランジスタは、基板上に形成され、下部と上部を有する本体、本体の上部に配置されるソース/ドレインノード、そして、本体の下部に配置されるドレイン/ソースノードを含む。半導体装置は、少なくとも本体の下部の上部表面に形成され、金属シリサイドを含む前記埋立ビットライン及び前記本体の上部を部分的に包むワードラインを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】リーク電流が低く、電界効果移動度が高いなどの優れた特性を有するTFTを備え、駆動回路を内蔵して部材点数を減らすことが可能な半導体装置において、駆動回路内部における腐食などの発生を防止する。

【解決手段】本発明の半導体装置においては、駆動回路を内蔵したTFTアレイ基板100に、ゲート電極2と、ゲート絶縁膜3と、結晶性半導体部分を含んでチャネル領域4cが形成される半導体層4と、チャネル領域4cを保護するチャネル保護膜5と、半導体層4に接続されたソース電極6及びドレイン電極7を備えたTFT、並びに、ゲート電極2と同層に形成された配線層2aとソース電極6と同層に形成された配線層6aを駆動回路内部においてコンタクトホール13を介し直接接触させて接続させる配線変換部12を備えるものである。

(もっと読む)

半導体装置の製造方法

【課題】絶縁ゲート型電界効果トランジスタのデバイス特性に変動が生じることやゲート絶縁膜が破壊されるのを抑制または防止できる半導体装置の製造方法を提供する。

【解決手段】絶縁層上に半導体層が形成された基板を準備し、半導体層の表面にアルゴンイオン注入を行い、アルゴンイオン注入後の半導体層上にゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成し、半導体層にソース領域およびドレイン領域を形成する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるチャネル保護膜5d、6dは逆テーパ形状を有し、そのチャネル保護膜5d、6dの端部が低誘電層5c、6cと重なった構造を有しているため、チャネル保護膜5d、6dと低誘電層5c、6cとが重なった部分に生じる電界Eを弱めることができる。そして、チャネルに作用する電界Eのバックゲート効果を抑制することによって、各薄膜トランジスタ5、6のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるソース電極6i(5i)と不純物半導体膜6g(5g)の積層体と、ドレイン電極6h(5h)と不純物半導体膜6f(5f)の積層体が、チャネル保護膜6d(5d)に重ならない構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制するとともに、薄膜トランジスタ6(5)のチャネル長を短くすることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体OSを用い、オフ状態でのソースとドレイン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ162、書き込み用トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルを有する半導体装置において、メモリセルへの情報の書き込みは、書き込み用トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードFGに電位を供給し、ノードFGに所定量の電荷を保持させることで行う。書き込みを1×109回行う前後において、メモリセルのメモリウィンドウ幅の変化量は2%以内である。

(もっと読む)

表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】表示装置の形成方法は、基板上に下地絶縁層を設け、その層上に配線パターンに沿った第1の銅拡散防止層を設ける。次に、その第1の銅拡散防止層上面に第1の銅拡散防止層の幅より僅かに狭い銅配線層を積層し、銅配線層の全表面を覆うように、第2の金属拡散防止層を設ける方法である。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

フロント型プロジェクタ

【課題】高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつフロント型プロジェクタである。

【解決手段】チャネル形成領域、ソース領域、及びドレイン領域を有する半導体層と、島状のゲート電極とを備えた薄膜トランジスタを有し、ゲート電極が接続する第1配線と、ソース領域又はドレイン領域が接続する第2配線とは直交し、第2配線や容量配線と平行かつ重なるように配置されている。

(もっと読む)

電界効果型トランジスタの製造方法、表示装置の製造方法、X線撮像装置の製造方法及び光センサの製造方法

【課題】熱処理の温度を低減しつつ、トランジスタ特性の向上を図る。

【解決手段】In,Ga及びZnを含有し、各元素の組成比をIn:Ga:Zn=a:b:cとした場合、a+b=2かつ1.2<b<2かつ1≦c≦2の範囲で規定される非晶質酸化物半導体からなる活性層を形成する工程と、前記活性層を240℃以下で熱処理する工程と、を経て電界効果型トランジスタを製造する。

(もっと読む)

半導体装置の製造方法、半導体装置及び半導体ウエハへの印字方法

【課題】ウエハの表面に対して垂直方向における位置決めを容易に行うことができ、且つ、ウエハの種別を容易に確認することができる半導体ウエハへの印字方法、半導体装置の製造方法、及び半導体装置を提供する。

【解決手段】絶縁性を有する透明基板及び透明基板の表面上に素子形成膜が積層された構造を有する半導体ウエハを準備する工程と、透明基板の裏面上に位置決め用光を反射する光反射膜を形成する工程と、素子形成膜の配置面側からレーザを照射して光反射膜に印字を形成する工程と、素子形成膜に半導体素子を形成する工程と、素子形成膜及び半導体素子を覆う層間絶縁膜を形成する工程と、コンタクト配線を形成する工程と、メタル配線を層間絶縁膜上に形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその作製方法

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物半導体膜を形成した後、酸化物半導体膜が露出した状態で第1の加熱処理を行う。次いで、酸化物半導体膜中の水分、または水素などの不純物をさらに低減するために、イオン注入法またはイオンドーピング法などを用いて、酸化物半導体膜に酸素を添加した後、再び、酸化物半導体膜が露出した状態で第2の加熱処理を行う。

(もっと読む)

表示装置およびそれを用いた電子機器

【課題】本発明の一態様は、酸化物半導体において高い移動度を達成し、信頼性の高い表示装置を提供する。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面から内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化物材料を用いて高移動度のトランジスタを形成し、それを用いて同一基板上にドライバ回路を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物半導体膜を形成した後、酸化物半導体膜が露出した状態で第1の加熱処理を行う。次いで、酸化物半導体膜中の水分、または水素などの不純物をさらに低減するために、イオン注入法またはイオンドーピング法などを用いて、酸化物半導体膜に酸素を添加した後、再び、酸化物半導体膜が露出した状態で第2の加熱処理を行う。

(もっと読む)

積層酸化物材料、半導体装置、および半導体装置の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面から内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化物材料の作製方法である。

(もっと読む)

積層酸化物材料、半導体装置、および半導体装置の作製方法

【課題】トランジスタなどの半導体素子を有する半導体装置を安価に得ることのできる生産性の高い作製工程を提供することを課題の一とする。

【解決手段】下地部材上に、酸化物部材を形成し、加熱処理を行って表面から内部に向かって結晶成長する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化物結晶部材を積層して設ける積層酸化物材料の作製方法である。特に第1の酸化物結晶部材と第2の酸化物結晶部材がc軸を共通している。ホモ結晶成長またはヘテロ結晶成長の同軸(アキシャル)成長をさせていることである。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】半導体膜とソース・ドレイン電極とを好適に電気的接合させる。

【解決手段】駆動トランジスタ6における半導体膜6bの表面凹凸はエッチバックにより緩和されており、その半導体膜6bが一対の不純物半導体膜6f,6gと接する上面側が平坦化されているので、半導体膜6bと不純物半導体膜6f,6gとの界面は乱れることなく好適に接合される。そして、不純物半導体膜6f,6gを介して、ドレイン電極6hとソース電極6iが半導体膜6bに好適に接合されるので、ドレイン電極6hとソース電極6iが半導体膜6bに好適に電気的接合されるようになる。

(もっと読む)

141 - 160 / 538

[ Back to top ]