Fターム[5F110EE38]の内容

Fターム[5F110EE38]に分類される特許

41 - 60 / 538

半導体装置

【課題】パワーデバイスである大電力用途向けの電界効果トランジスタにおいて、特性の良好な電界効果トランジスタを提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆うゲート絶縁層と、第1のゲート電極と重畳して、且つゲート絶縁層と接する酸化物半導体層と、酸化物半導体層の端部を覆うキャリア密度の高い酸化物半導体層と、キャリア密度の高い酸化物半導体層と接するソース電極及びドレイン電極と、ソース電極、ドレイン電極及び酸化物半導体層を覆う絶縁層と、絶縁層と接し、且つ、ソース電極及びドレイン電極の間に設けられる第2のゲート電極と、を有し、キャリア密度の高い酸化物半導体層は、酸化物半導体層を介して対向し、且つ酸化物半導体層の端部の上面、下面、及び側面のそれぞれ一部、並びにゲート絶縁層の上面一部と接する半導体装置である。

(もっと読む)

半導体装置

【課題】特定のトランジスタのゲートの電位に応じて記憶情報の判別が行われる半導体装置において、当該トランジスタのしきい値電圧のばらつきの低減と、長期間に渡る情報の保持とを両立することで情報の保持特性に優れる半導体装置を提供すること。

【解決手段】チャネル領域が酸化物半導体によって形成されるトランジスタのソース又はドレインのみに電気的に接続されるノードにおいて電荷の保持(情報の記憶)を行う。なお、当該ノードにソース又はドレインが電気的に接続されるトランジスタは、複数であってもよい。また、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

記憶装置

【課題】回路面積を小さくする。

【解決手段】記憶データとしてデータを記憶するメモリセルと、出力信号線と、電圧が与えられる配線と、を具備し、メモリセルは、記憶データと検索データの比較演算を行い、演算結果に応じて導通状態又は非導通状態になる比較回路と、記憶データの書き込み及び保持を制御する電界効果トランジスタと、を備え、比較回路が導通状態のときに、出力信号線の電圧値が配線の電圧と同等の値になる記憶装置。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

半導体装置

【課題】動作速度の低下を抑制しつつ、消費電力を低減する。

【解決手段】第1の半導体領域の上に絶縁領域を有し、且つ絶縁領域の上に第2の半導体領域を有する基板に設けられた第1の電界効果トランジスタと、基板の上に設けられた絶縁層と、絶縁層の一平面に設けられ、酸化物半導体層を含む第2の電界効果トランジスタと、第2の電界効果トランジスタのソース及びドレインと同一工程により形成され、第1の電界効果トランジスタの閾値電圧を制御するための電圧が供給される制御端子と、を備える。

(もっと読む)

半導体装置

【課題】フォトセンサを有する半導体装置において、外光のノイズを軽減し、且つトランジスタのオフ電流によるリークが原因となるノイズも低減する。

【解決手段】マトリクス状に配置された複数のフォトセンサを有する。複数のフォトセンサはそれぞれ、光電変換素子と増幅回路とを有する。バックライトを点灯して被検出物に光を照射して第p行目のフォトセンサでリセット動作及び蓄積動作を行った後、バックライトを非点灯として第(p+1)行目のフォトセンサでリセット動作及び蓄積動作を行い、その後全行のフォトセンサの選択動作を順次行う。隣接する行のフォトセンサで得られた出力信号の差分を取得し、差分を用いて被検出物の撮像画像の生成や被検出物の存在する領域の検出を行う。増幅回路は蓄積された電荷を保持するトランジスタを有し、当該トランジスタはチャネルが酸化物半導体層に形成される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】多値書き込みを行う半導体装置、及び半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体である酸化物半導体材料を用いることで、長期間にわたって情報を保持することが可能である。

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

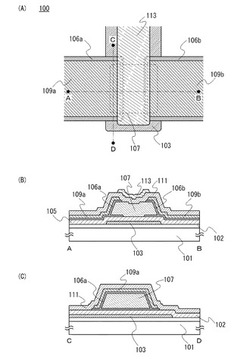

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体素子の作製方法

【課題】閾値電圧が制御され、動作速度が速く、製造工程が比較的簡単であり、十分な信

頼性を有する、酸化物半導体を用いた薄膜トランジスタ、及び薄膜トランジスタの作製方

法を提供することを課題の一つとする。

【解決手段】酸化物半導体層に含まれるキャリア濃度に影響する不純物、例えば、水素原

子や、H2Oなど水素原子を含む化合物を排除すればよい。酸化物半導体層に接して未結

合手に代表される欠陥を多く含む酸化物絶縁層を形成し、当該酸化物絶縁層に不純物を拡

散させ、上記酸化物半導体層中の不純物濃度を低減すればよい。また、酸化物半導体層、

又は酸化物半導体層に接する酸化物絶縁層を、クライオポンプを用いて排気して不純物濃

度が低減された成膜室内で成膜すればよい。

(もっと読む)

半導体装置、表示モジュール及び電子機器

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】酸化物半導体をチャネル形成領域に用いたトランジスタを有する半導体装置の作製において、酸化物半導体膜を形成した後、水分、ヒドロキシ基、または水素などを吸蔵或いは吸着することができる金属、金属化合物または合金を用いた導電膜を、絶縁膜を間に挟んで酸化物半導体膜と重なるように形成する。そして、該導電膜が露出した状態で加熱処理を行うことで、導電膜の表面や内部に吸着されている水分、酸素、水素などを取り除く活性化処理を行う。

(もっと読む)

横型IGBT

【課題】薄い活性層を有する積層基板に形成される横型IGBTの特性を改善する。

【解決手段】横型IGBT1は、p型のコレクタ領域46,48とp型のコレクタウェル領域44を備えている。コレクタウェル領域44は、コレクタ領域46,48を取り囲んでコレクタ領域46,48に接している。コレクタウェル領域44の不純物濃度は、コレクタ領域46,48の不純物濃度よりも薄い。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、ゲート電極を形成後、インライン装置にて、酸化アルミニウム膜と酸化シリコン膜と酸化物半導体膜を大気暴露することなく連続的に形成し、さらに同インライン装置にて加熱および酸素添加処理を行い、他の酸化アルミニウム膜でトランジスタを覆った後、熱処理を行うことで、水素原子を含む不純物が除去され、且つ、化学量論比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT)試験前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置

【課題】信頼性の高い、酸化物半導体を有する半導体装置。

【解決手段】酸化物半導体層は、ソース電極と重なる第1の領域と、ドレイン電極と重なる第2の領域と、ソース電極及びドレイン電極と重ならない第3の領域と、を有し、記第3の領域における酸化物半導体層の膜厚は、第1の領域及び第2の領域における酸化物半導体層の膜厚よりも小さく、第3の領域における酸化物半導体層の一端部は、第1のテーパを有し、記第3の領域における酸化物半導体層の他端部は、第2のテーパを有し、ソース電極の端部は、第3のテーパを有し、ドレイン電極の端部は、第4のテーパを有し、第1のテーパと、第3のテーパとは連続した形状を有し、第2のテーパと、第4のテーパとは連続した形状を有する半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

表示装置、液晶表示装置及びプロジェクター

【課題】高開口率な半導体装置を提供する。

【解決手段】絶縁表面上に第1配線と、第1配線上に第1絶縁膜と、第1絶縁膜上に半導体膜と、半導体膜上に第2絶縁膜と、第2絶縁膜上に第2配線と、第1配線と接続するゲート電極と、第2配線及びゲート電極上に第3絶縁膜と、第3絶縁膜上に半導体膜と接続する第3の配線とを有する半導体装置。

(もっと読む)

41 - 60 / 538

[ Back to top ]