Fターム[5F110EE43]の内容

Fターム[5F110EE43]に分類される特許

201 - 220 / 2,542

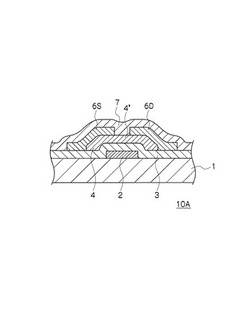

薄膜トランジスタ及びその製造方法

【課題】低温成膜可能な酸化物で半導体膜を形成した逆スタガ型薄膜トランジスタであって、半導体膜上に形成した保護膜の紫外線等に対する耐光性と耐環境安定性を向上させてなる薄膜トランジスタ及びその製造方法を提供する。

【解決手段】基板1上にパターン形成されたゲート電極2と、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上にパターン形成された酸化物半導体膜4と、酸化物半導体膜4上にパターン形成されたソース電極6S及びドレイン電極6Dと、ソース電極6S及びドレイン電極6D間に露出する酸化物半導体膜4を少なくとも覆う保護膜7とを有するボトムゲートトップコンタクト構造の薄膜トランジスタ10であって、保護膜7を、酸化物半導体材料で形成する。このとき、酸化物半導体膜4及び保護膜7が、InMZnO(MはGa,Al,Feのうち少なくとも1種)を含むアモルファス酸化物である酸化物半導体材料からなることが好ましい。

(もっと読む)

コプレナ型の酸化物半導体素子とその製造方法

【課題】折り曲げ耐性が向上したコプレナ型の酸化物半導体を提供し、また、コンタクトホールを精巧に形成するコプレナ型の酸化物半導体の製造方法を提供する。

【解決手段】絶縁性を有する基板と、前記基板上に配置され、チャネル領域及び電極接続領域を有する酸化物半導体層と、前記酸化物半導体層上に配置され、コンタクトホールを有するゲート絶縁層と、前記ゲート絶縁層上に配置されたソース電極、ドレイン電極、及びゲート電極と、を有するコプレナ型の酸化物半導体素子であって、前記ゲート絶縁層は、架橋ポリマーで形成されていることを特徴とするコプレナ型の酸化物半導体素子とその製造方法。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】有機半導体層の移動度を低下させることなく、容易に有機半導体層をパターニングした有機半導体素子を得ることができる有機半導体素子の製造方法を提供する。

【解決手段】液晶性有機半導体材料を配向させる配向層1上にソース電極2およびドレイン電極3を形成するソース電極およびドレイン電極形成工程と、上記ソース電極および上記ドレイン電極を覆うように上記配向層上に、液晶性有機半導体材料を有する有機半導体層4を形成する有機半導体層形成工程と、上記有機半導体層上の少なくとも上記ソース電極および上記ドレイン電極間のチャネル領域C上に、誘電体層5を形成する誘電体層形成工程と、上記誘電体層が形成された上記有機半導体層を上記液晶性有機半導体材料の液晶相温度でアニール処理するアニール処理工程と、を有することを特徴とする有機半導体素子の製造方法。

(もっと読む)

有機半導体素子の製造方法

【課題】高い精度で効率良くパターニングすることができる有機半導体素子の製造方法を提供する。

【解決手段】有機半導体層形成用溶液に対して撥液性がある撥液部2を有する基体1を準備する第1工程、前記基体1の撥液部2上に遮蔽層5を形成する第2工程、前記基体1の撥液部2の一部を前記有機半導体層形成用溶液に対して親液性がある親液部7に変性する第3工程、及び、前記第1工程、前記第2工程、または前記第3工程の後に行い、前記基体1上にソース電極3及びドレイン電極4を形成する第4工程を有する有機半導体素子用基板6の形成工程と、有機半導体層8を親液部7上に形成する有機半導体層8の形成工程と、を有する有機半導体素子の製造方法。

(もっと読む)

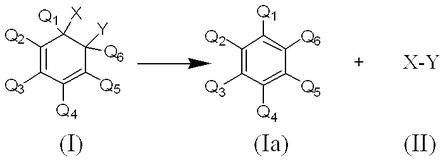

芳香環を有するπ電子共役系化合物を含有する膜状体の製法、及び該π電子共役系化合物の製法

【課題】低いエネルギー付与でπ電子共役化合物を得る製造方法、及びこの技術を利用し、難溶性π電子共役系化合物の連続した薄膜の効率的な製造方法を提供する。更に該薄膜の有機電子デバイスへ応用する。

【解決手段】π電子共役系化合物前駆体(I)を含む溶媒の塗工液を基材に塗布して形成された塗工膜より、式(II)で示される脱離性置換基を脱離させ(Ia)で示されるπ電子共役系化合物を含有する膜状体を生成することを特徴とする膜状体の製造方法。

[式(I)、(Ia)、(II)中、XおよびYは水素原子もしくは脱離性置換基を表す。Q2乃至Q5はそれぞれ独立して水素原子、ハロゲン原子または、1価の有機基であり、Q1とQ6は水素原子、ハロゲン原子または、前記脱離性置換基以外の一価の有機基である。Q1乃至Q6は隣り合った基同士でそれぞれ結合して環を形成していてもよい。]

(もっと読む)

記憶回路、記憶装置、信号処理回路

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶回路の提供、消費電力の低減可能な信号処理回路を提供する。

【解決手段】記憶回路は、トランジスタと、容量素子と、第1の演算回路と、第2の演算回路と、第3の演算回路と、スイッチと、を有し、第1の演算回路の出力端子は、第2の演算回路の入力端子と電気的に接続され、第2の演算回路の入力端子は、スイッチを介して第3の演算回路の出力端子と電気的に接続され、第2の演算回路の出力端子は、第1の演算回路の入力端子と電気的に接続され、第1の演算回路の入力端子は、トランジスタのソース及びドレインの一方と電気的に接続され、トランジスタのソース及びドレインの他方は、容量素子の一対の電極のうちの一方、及び第3の演算回路の入力端子と電気的に接続され、トランジスタのチャネルは酸化物半導体層に形成される。

(もっと読む)

薄膜素子及びその製造方法、並びに、画像表示装置の製造方法

【課題】大掛かりな製造装置を必要とすることなく、簡素、簡易な方法にて薄膜素子能動部を製造することができる薄膜素子の製造方法を提供する。

【解決手段】薄膜素子の製造方法は、支持基板20上に樹脂材料から成る第1基材21を塗布法にて形成した後、第1基材21上に、熱によって又はエネルギー線の照射によって硬化する樹脂から成る第2基材22を形成し、次いで、第2基材上に薄膜素子能動部30を形成し、その後、支持基板20を第1基材21から剥離する各工程を備えており、第1基材21を構成する樹脂材料のガラス転移温度は180゜C以上である。

(もっと読む)

有機半導体素子の製造方法

【課題】高い精度で効率良く有機半導体をパターニングすることができる有機半導体素子の製造方法を提供する。

【解決手段】有機半導体層形成用溶液に対して撥液性がある撥液部2を有する基体1と、前記基体1上に形成されたソース電極3及びドレイン電極4と、前記基体1の撥液部2の一部上に形成された遮蔽層5とを有し、前記ソース電極3及び前記ドレイン電極4に金もしくは/及び白金、又は酸化還元電位が銀以下の金属が含まれている有機半導体素子用基板6上に紫外線又は含酸素プラズマを前記有機半導体素子用基板6に照射して、前記有機半導体層形成用溶液に対して親液性がある親液部7に変性する有機半導体素子用基板6の形成工程と、有機半導体層8の形成工程と、前記ソース電極3及び前記ドレイン電極4に酸化還元電位が銀以下の金属が含まれている場合は還元工程と、を有する有機半導体素子の製造方法。

(もっと読む)

有機半導体素子およびその製造方法

【課題】本発明は、製造時におけるソース電極およびドレイン電極の劣化を好適に防止することができ、優れたスイッチング機能を有する有機半導体素子およびその製造方法を提供することを主目的とする。

【解決手段】基材と、上記基材上に形成されたゲート電極と、上記ゲート電極を覆うように形成されたゲート絶縁層と、上記ゲート絶縁層上に形成され、銀を主成分とする金属材料を含むソース電極およびドレイン電極と、上記ソース電極および上記ドレイン電極上に形成され、酸素に対する遮蔽性を有する電極保護層と、少なくとも上記ソース電極および上記ドレイン電極の間のチャネル領域に形成可能なパターン形状を有し、有機半導体材料を含む有機半導体層と、上記有機半導体層上のみに形成され、真空紫外光に対する遮光性を有する遮光材料を含むVUV遮蔽層とを有することを特徴とする有機半導体素子を提供することにより上記課題を解決する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間にバッファ層が設けられた逆スタガ型(ボト

ムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン

電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設

けることによってオーミック性のコンタクトを形成する。

(もっと読む)

酸化物半導体膜、半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を活性層に用いるトランジスタにおいて、チャネル領域と隣接するソース領域およびドレイン領域に微小な空洞を設ける。酸化物半導体膜に形成されるソース領域およびドレイン領域に微小な空洞を設けることによって、微小な空洞に酸化物半導体膜のチャネル領域に含まれる水素を捕獲させることができる。

(もっと読む)

電子デバイス及びその製造方法

【課題】転写プロセスを用いずに、所期のグラフェンを制御性良く容易且つ確実に安定形成し、信頼性の高い高性能の微細な電子デバイスを実現する。

【解決手段】基板1上に絶縁層2を形成し、絶縁層2に空隙2Aを形成し、空隙2Aに触媒材料4を充填し、絶縁層2における触媒材料4の露出面4aにグラフェン5を形成し、絶縁層2上でグラフェン5の両端部に接続するように一対の電極5,6を形成し、グラフェン5を一部除去してグラフェンリボン8を形成し、グラフェンリボン8の除去された部位である間隙2A1,2A2を通じて触媒材料4を除去する。

(もっと読む)

微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子

【課題】10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供すること。

【解決手段】本発明の微細構造物の製造方法は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

薄膜トランジスタアレイ、表示装置、およびそれらの製造方法

【課題】本発明は、開口率を大きくする必要がなく、印刷に適し、複数画素を用いずに面積階調できる薄膜トランジスタアレイ、表示装置、および薄膜トランジスタアレイの製造方法を提供する。

【解決手段】画素の有効領域の幅をA、画素の有効領域のネガパターンの幅をBとしたとき、幅Bが幅Aよりも大きな薄膜トランジスタとする。あるいは、対向電極と画素電極の距離をCとしたとき、距離Cが幅Bの4分の1以上B以下である表示装置とする。

(もっと読む)

微結晶半導体膜、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製方法を提供することを課題とする。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、種結晶上に、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を形成し、第2の微結晶半導体膜上に、第2の微結晶半導体膜に含まれる混相粒の隙間を埋めつつ、結晶成長を促す第4の条件で、第3の微結晶半導体膜を積層形成する。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

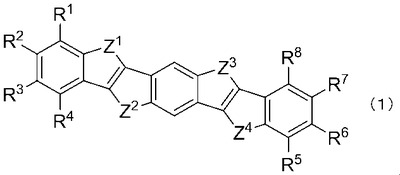

可溶性ヘテロアセン化合物及び該化合物を含有する薄膜および有機トランジスタ

【課題】有機半導体材料として好適な新規化合物の提供。

【解決手段】下記式(1)で示される化合物。

[式中、Z1〜Z4はそれぞれ独立に、硫黄原子又はセレン原子を表す。R1〜R8はそれぞれ独立に、水素原子、フッ素原子で置換されていてもよい炭素数1〜30のアルキル基、フッ素原子で置換されていてもよい炭素数1〜30のアルコキシ基、又は特定な置換シリル基を表す。]

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】樹脂基板上に設けたボトムゲート型薄膜トランジスタにおいて、製造プロセスを簡略化することにより、高品質で低コストの薄膜トランジスタとその製造方法及び画像表示装置を提供することを目的とする。

【解決手段】ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。また、金属は、Alを含む金属であり、ゲート電極の膜厚は、10nm以上100nm以下である。

(もっと読む)

201 - 220 / 2,542

[ Back to top ]