Fターム[5F110EE45]の内容

Fターム[5F110EE45]に分類される特許

341 - 360 / 2,010

マルチゲート電界効果トランジスタのゲート電極およびその製造方法

【課題】マルチゲート電界効果トランジスタにおいて、新規なゲート電極構造と製造方法を提供する。

【解決手段】マルチゲート電界効果トランジスタ102のゲート電極100は、半導体基板104と、前記半導体基板上の誘電体層106と、前記誘電体層上のフィン108と、前記フィンの側面上のゲート絶縁膜であって、前記フィンの側面上に形成されるゲート絶縁膜と接する誘電体層の上面部分を除き、前記誘電体層の上面上には形成されないゲート絶縁膜110と、フィン上のゲート電極層112と、前記フィンを覆うように形成されるポリシリコン層114とを具備する。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

電界効果トランジスタ及び電界効果トランジスタの製造方法

【課題】MgとInとを主成分とする複合酸化物を活性層とし、かつ良好な電界効果移動度を示す電界効果トランジスタを提供すること。

【解決手段】ゲート電極3、ソース電極4及びドレイン電極5と、ドレイン電極5及びソース電極4が接合された活性層2と、活性層2及びゲート電極3の間にゲート絶縁膜6と、備え、活性層2がMgとInとを主成分とする複合酸化物であり、ゲート絶縁膜6がY2O3である電界効果トランジスタ1を使用する。

(もっと読む)

装置

【課題】軽量、薄型、小型であり、かつ読み込んだ画像に明るさのむらが生じないエリアセンサ及びエリアセンサを備えた表示装置を提供する。

【解決手段】エリアセンサが有する画素は、光源としてのEL(エレクトロルミネッセンス)素子と、光電変換素子としてのフォトダイオードと複数のTFTをそれぞれ有しており、EL素子とフォトダイオードの動作をTFTで制御していることを特徴とするエリアセンサ及びエリアセンサを備えた表示装置。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

薄膜トランジスタおよびその製造方法、並びにその薄膜トランジスタを備えた装置

【課題】低温で作製可能であり、高い電界効果移動度を示す薄膜トランジスタを提供する。

【解決手段】酸化物半導体層からなる活性層を備えた薄膜トランジスタにおいて、活性層が、ゲート電極側から膜厚方向に第1の電子親和力χ1を有する第1の領域A1、第1の電子親和力χ1よりも小さい第2の電子親和力χ2を有する第2の領域A2とを含み、第1の領域A1を井戸層、第2の領域A2とゲート絶縁膜とを障壁層とする井戸型ポテンシャルを構成するものとする。ここで、活性層を、a(In2O3)・b(Ga2O3)・c(ZnO)から成る酸化物半導体層からなるものとし、第2の領域A2のb/(a+b)を第1の領域A1のb/(a+b)よりも大きくする。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層に対して良好なコンタクトを形成しうる配線構造体を有する半導体装置及びその製造方法を提供する。

【解決手段】グラフェン層と、グラフェン層の第1の領域に形成され、グラフェン層と、グラフェン層に積層された第1のネットワーク・ナノグラファイト層とを含む第1の配線部と、グラフェン層の第2の領域に形成され、グラフェン層と、グラフェン層に積層された第2のネットワーク・ナノグラファイト層とを含む第2の配線部と、グラフェン層の、第1の領域と第2の領域との間の第3の領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】交流電圧で使用することができる半導体装置を提供する。

【解決手段】半導体基板11に形成された第1トランジスタT1と、半導体基板11上にBOX層12を介して形成された第2トランジスタT2と、を備え、第1トランジスタT1は、半導体基板11の表面に形成された第1ボディ領域11fと、この第1ボディ領域11fを挟むように形成された第1ソース領域11d及び第1ドレイン領域11eと、有し、第1ボディ領域11f上に第2トランジスタT2の第2ドレイン領域13cが配置され、第1ドレイン領域11e上に第2トランジスタT2の第2ボディ領域13aが配置され、第1ドレイン領域11eとBOX層12における第2ボディ領域13aとの間に接続層17が形成され、かつ第2ドレイン領域13cが第1トランジスタT1のゲート電極を兼ねた。

(もっと読む)

表示装置及びその作製方法

【課題】デジタル階調と時間階調とを組み合わせた駆動方法において、アドレス期間よりも短いサステイン期間を有する場合にも正常に画像(映像)の表示が可能であり、EL駆動用トランジスタが、劣化によりノーマリーオンとなった場合にも、信号線の電位を変えて動作を補償することの出来る画素を提供することを課題とする。

【解決手段】消去用TFT105のソース領域とドレイン領域とは、一方は電流供給線108に接続され、残る一方はゲート信号線106に接続されている。この構造により、EL駆動用TFT102のしきい値のシフトにより、ノーマリーオンとなった場合にも、ゲート信号線106の電位を変えることで、EL駆動用TFT102が確実に非導通状態となるように、EL駆動用TFT102のゲート・ソース間電圧を変えることを可能とする。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置

【課題】高集積化を図り、単位面積あたりの記憶容量を増加させた新たな構造の半導体装置を提供することを目的の一とする。高集積化に伴い増加する回路素子数の低減が可能で、かつ、素子数低減による電力削減が可能な、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ビット線と、m(mは3以上の自然数)本のワード線と、ソース線と、m本の信号線と、第1乃至mのメモリセルと、駆動回路と、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成において、駆動回路は、第j(jは3以上の自然数)の信号線に出力される信号を用いて第(j−1)の信号線に出力される信号を生成する。

(もっと読む)

半導体装置の作製方法

【課題】金属元素を用いた結晶化法において、ゲッタリングのために必要な不純物元素の濃度が高く、その後のアニールによる再結晶化の妨げとなり問題となっている。

【解決手段】

本発明は半導体膜に、希ガス元素を添加した不純物領域を形成し、加熱処理およびレーザアニールにより前記不純物領域に半導体膜に含まれる金属元素を偏析させるゲッタリングを行なうことを特徴としている。そして、半導体膜が形成された基板(半導体膜基板)の上方または下方からレーザ光を照射してゲート電極を加熱し、その熱によってゲート電極の一部と重なる不純物領域を加熱する。このようにして、ゲート電極の一部と重なる不純物領域の結晶性の回復および不純物元素の活性化を行なうことを可能とする。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】メタルゲートを用いたCMISまたはCMOS構造の集積回路デバイスにおいて、Nチャネル領域およびPチャネル領域におけるゲート絶縁膜、メタルゲート層等のつくり分けに関しては、種々の方法が提案されているが、プロセスが複雑になる等の問題があった。

【解決手段】本願発明は、CMOS集積回路デバイスの製造方法において、Nチャネル領域およびPチャネル領域において、ゲート電極膜形成前の高誘電率ゲート絶縁膜の電気的特性を調整するためのチタン系窒化物膜を下方のチタンを比較的多く含む膜と、上方の窒素を比較的多く含む膜を含む構成とするものである。

(もっと読む)

酸化物半導体薄膜の製造方法および酸化物半導体薄膜、薄膜トランジスタの製造方法および薄膜トランジスタ、並びに薄膜トランジスタを備えた装置

【課題】300℃以上の高温での熱処理することなく、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適したIGZO系酸化物薄膜を製造する。

【解決手段】In,Ga,Zn,Oを主たる構成元素とし、組成比が11/20≦Ga/(In+Ga+Zn)≦9/10、且つ3/4≦Ga/(In+Ga)≦9/10、且つZn/(In+Ga+Zn)≦1/3を満たす酸化物半導体薄膜をスパッタリング法により、アルアゴンガス雰囲気下で酸素ガスを導入することなく成膜し、成膜された酸化物半導体薄膜に対して、酸化性雰囲気中で100℃以上、300℃未満の熱処理を施す。

(もっと読む)

酸化物半導体薄膜の製造方法および該製造方法により作製された酸化物半導体薄膜、薄膜トランジスタ、並びに薄膜トランジスタを備えた装置

【課題】低温アニールによる低抵抗化が起こらず、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適したIGZO系酸化物薄膜を製造する。

【解決手段】In,Ga,Zn,Oを主たる構成元素とし、組成比が11/20≦Ga/(In+Ga+Zn)≦9/10、且つ3/4≦Ga/(In+Ga)≦1、且つZn/(In+Ga+Zn)≦1/3を満たす酸化物半導体薄膜を成膜する成膜工程と、成膜された酸化物半導体薄膜に対して、酸化性雰囲気中で100℃以上、300℃以下の熱処理を施す熱処理工程とを含み、熱処理工程後の酸化物半導体薄膜の抵抗率が1Ωcm以上、1×106Ωcm以下となるように、成膜工程における成膜条件および熱処理工程における熱処理条件を設定する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、且つ書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば酸化物半導体材料を用いて半導体装置を構成する。また半導体装置の各メモリセルの酸化物半導体材料を用いたトランジスタを直列に接続する。更に、第j(jは2以上m以下の自然数)のメモリセルの容量素子の端子の一方に電気的に接続される配線と、第(j−1)のメモリセルのチャネルが酸化物半導体層に形成されたトランジスタのゲート端子に電気的に接続される配線と、を同じ配線(第jのワード線)とする。これによってメモリセルあたりの配線の数を減らし、メモリセルあたりの占有面積を低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

電子デバイス及びその製造方法、並びに、半導体装置及びその製造方法

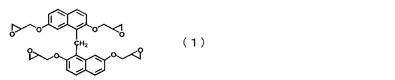

【課題】従来よりも低い温度での形成が可能である絶縁層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、(A)制御電極12、(B)第1電極14及び第2電極14、並びに、(C)第1電極14と第2電極14との間であって、絶縁層13を介して制御電極12と対向して設けられた、有機半導体材料層15から成る能動層16を備えて成り、少なくとも能動層12と接触する絶縁層13の部分は、下記の式(1)にて示される材料を硬化して成る層から構成されている。 (もっと読む)

(もっと読む)

酸化物半導体薄膜およびその製造方法、並びに薄膜トランジスタ、薄膜トランジスタを備えた装置

【課題】生産性、組成均一性を向上させることができ、かつ低温アニール時に低抵抗化が起こらず、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した酸化物半導体薄膜を得る。

【解決手段】In、GaおよびOを主たる構成元素とする酸化物半導体薄膜であって、In,Gaの組成比が3/4≦Ga/(In+Ga)≦9/10であり、かつ、抵抗率が1Ωcm以上、1×106Ωcm以下を満たすものとする。

(もっと読む)

341 - 360 / 2,010

[ Back to top ]