Fターム[5F110EE45]の内容

Fターム[5F110EE45]に分類される特許

261 - 280 / 2,010

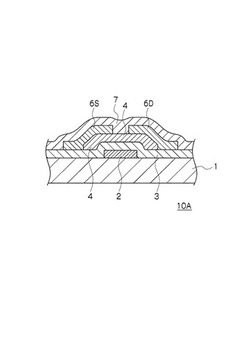

薄膜トランジスタの製造方法

【課題】高温処理プロセスを適用することなく、酸化物半導体膜を効率的に製造できる薄膜トランジスタの製造方法を提供する。

【解決手段】

基板1上にゲート電極2を所定のパターンで形成する工程と、ゲート電極2を覆うゲート絶縁膜3を所定のパターンで形成する工程と、ゲート絶縁膜3上にアモルファス酸化物膜4’を所定のパターンで形成する工程と、アモルファス酸化物膜4’上にソース電極6S及びドレイン電極6Dを所定のパターンで形成する工程と、ソース・ドレイン電極6S,6D間で露出するアモルファス酸化物膜4’を少なくとも覆う保護膜7を形成する工程とを有する。このアモルファス酸化物膜4’の形成工程では、RFスパッタリング法でアモルファス酸化物膜4’を成膜し、保護膜7の形成工程では、RFスパッタリング法で保護膜7を成膜して、アモルファス酸化物膜4’を半導体化する。

(もっと読む)

表示装置及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を

同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電

極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気

的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成

された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを

介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成

された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的

に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

ジチオケトピロロピロール系ポリマー

【課題】高いフィールド効果移動性、空気安定性、及び良好な溶解性を示す半導体ポリマーを提供すること。

【解決手段】ピロロ[3,4−C]ピロールー2,5−ジチオンを必須単位とし、該化合物の3−位及び6−位を結合手として繰り返し単位を構成し、エテニル、エチニル、アリール、置換アリール、ヘテロアリール、置換ヘテロアリール等を共重合成分として含むポリマー。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の作製工程において、フォトリソグラフィ工程数を削減する。

【解決手段】トランジスタの、ゲート電極となる導電膜、ゲート絶縁膜となる絶縁膜、チャネル領域が形成される半導体膜およびチャネル保護膜となる絶縁膜を連続で形成し、多階調マスクであるフォトマスクによって露光し現像したレジストマスクを用いて、(1)レジストマスクのない領域において、チャネル保護膜となる絶縁膜、チャネル領域が形成される半導体膜、ゲート絶縁膜となる絶縁膜およびゲート電極となる導電膜を連続してエッチングし、(2)レジストマスクをアッシングなどによって後退させ、レジストマスクを残膜厚が小さい領域のみを除去することで、チャネル保護膜となる絶縁膜の一部を露出させ、(3)露出したチャネル保護膜となる絶縁膜の一部をエッチングし、一対の開口部を形成する。

(もっと読む)

半導体装置

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置(薄膜トランジスタ)を製造する。

【解決手段】本発明は、(a)基板SUBの上方に、第1金属酸化物を含有する半導体からなる導電層を形成する工程と、(b)導電層上に第2金属酸化物を含有する半導体からなる犠牲層SLを形成する工程と、(c)導電層と犠牲層SLとの積層膜を加工する工程と、(d)上記(c)工程の後、犠牲層SL上に、金属膜を形成する工程と、(e)上記(d)工程の後、上記金属膜の第1領域をドライエッチングにより除去する工程と、(f)上記(e)工程の後、上記第1領域の上記犠牲層SLをウェットエッチングにより除去する工程と、を有し、上記(c)工程と、上記(f)工程との間に、(g)導電層に熱処理を施し、導電層を結晶化し、導電層CLcとする工程を有する。かかる工程によれば、ドライエッチングにより生じた犠牲層SLのダメージ領域DRを除去できる。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

薄膜トランジスタおよびその製造方法、並びに表示装置

【課題】良好な伝達特性を有する薄膜トランジスタおよびその製造方法を提供する。

【解決手段】ゲート電極11およびゲート絶縁膜12上に酸化物半導体よりなるチャネル層13および導電性のチャネル保護膜をこの順に形成する。チャネル保護膜上にソース・ドレイン電極15A,15Bを形成したのち、チャネル保護膜をソース・ドレイン電極15A,15B間において電気的に分離(間隙14Cを形成)し、チャネル保護膜14A,14Bとする。チャネル保護膜を電気的に分離する工程において、チャネル層13を結晶酸化物半導体により形成するようにしたため、容易にチャネル層13とチャネル保護膜との選択的なエッチングを行うことができる。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体化合物

【課題】空気安定性、良好な溶解度、および高い移動度を持つ有機薄膜トランジスタ用半導体を提供する。

【解決手段】特定構造のチアキサンテノチアキサンテン化合物を活性層として用いる。チアキサンテノチアキサンテン化合物は主に結晶性または液晶である。この化合物は、空気安定性、良好な溶解度、および高い移動度を確実にするように設計される。有機薄膜トランジスタは一般に、基板20上に、ゲート電極30、ソース電極50およびドレイン電極60、ゲート電極をソースおよびドレイン電極と分離する電気絶縁ゲート誘電体層40、およびゲート誘電体層と接触し、ソースおよびドレイン電極を架橋する半導体層70を含む。

(もっと読む)

電子素子及びその製造方法

【課題】素子性能の低下が抑制される電子素子を提供する。

【解決手段】基板12と、前記基板上の動作領域に配置された第1導電層14Gと、前記第1導電層上に該第1導電層と接して配置された絶縁層16と、前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂30の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部22と、を有する電子素子10。

(もっと読む)

半導体装置の製造方法

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの活性層に好適に用いられる非晶質酸化物の製造方法を提供する。

【解決手段】基板1上に、非晶質酸化物層2を形成する前に、基板1表面にオゾン雰囲気中で紫外線を照射したり、基板1表面にプラズマを照射したり、あるいは基板1表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物層2を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板1上に、非晶質酸化物層2を形成する後に、非晶質酸化物層2の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの活性層に好適に用いられる非晶質酸化物の製造方法を提供する。

【解決手段】基板1上に、非晶質酸化物層2を形成する前に、基板1表面にオゾン雰囲気中で紫外線を照射したり、基板1表面にプラズマを照射したり、あるいは基板1表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物層2を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板1上に、非晶質酸化物層2を形成する後に、非晶質酸化物層2の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

261 - 280 / 2,010

[ Back to top ]