Fターム[5F110EE45]の内容

Fターム[5F110EE45]に分類される特許

181 - 200 / 2,010

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】多値書き込みを行う半導体装置、及び半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体である酸化物半導体材料を用いることで、長期間にわたって情報を保持することが可能である。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

表示装置

【課題】酸化物半導体を用いたトランジスタを有する表示装置において、寄生容量を軽減する。表示装置において、解像度の向上や、高精細化といった高性能化及び高品質化を達成する。

【解決手段】ボトムゲート型のトランジスタにおいて、酸化物半導体膜と重畳して設けられるゲート電極が第1のゲート電極と第2のゲート電極とに間隔を有して分割して設けられる。第1のゲート電極はソース電極又はドレイン電極の一方と重畳して設けられ、第2のゲート電極はソース電極又はドレイン電極の他方と重畳して設けられる。

(もっと読む)

記憶素子、信号処理回路

【課題】新たな構成の不揮発性の記憶素子、それを用いた信号処理回路を提供する。

【解決手段】第1の回路と第2の回路とを有し、第1の回路は第1のトランジスタと第2のトランジスタとを有し、第2の回路は第3のトランジスタと第4のトランジスタとを有する。第1の信号に対応する信号電位は、オン状態とした第1のトランジスタを介して第2のトランジスタのゲートに入力され、第2の信号に対応する信号電位は、オン状態とした第3のトランジスタを介して第4のトランジスタのゲートに入力される。その後、第1のトランジスタ及び第3のトランジスタをオフ状態とする。第2のトランジスタの状態と第4のトランジスタの状態との両方を用いて、第1の信号を読み出す。第1のトランジスタ及び第3のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタとする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、更にソース線を削減することにより単位面積あたりの記憶容量を増加させる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体記憶装置

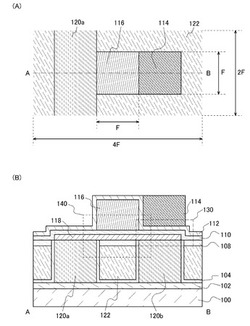

【課題】データ保持のためのリフレッシュ動作の頻度を低減し、消費電力の小さいDRAMを提供する。また、DRAMに占めるキャパシタの面積を縮小し、集積度の高い半導体記憶装置を提供する。

【解決手段】ビット線、ワード線、トランジスタおよびキャパシタからなる半導体記憶装置であり、トランジスタは、ソース電極およびドレイン電極と、少なくともソース電極およびドレイン電極の上面と接する酸化物半導体膜と、少なくとも酸化物半導体膜の上面と接するゲート絶縁膜とを有し、上面から見て網状の導電膜の網の目の部分に設けられる。ここで、キャパシタは、一対の電極の一方と、網状の導電膜と、一対の電極の一方および網状の導電膜の間に設けられた第2の絶縁膜と、を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置及びその駆動方法

【課題】消費電力を低減することが可能な新たな構造の半導体装置及びその駆動方法を提供する。

【解決手段】メモリセルは、容量素子と、第1のトランジスタと、第1のトランジスタよりオフ電流の小さな第2のトランジスタとを有する。第1のトランジスタは、第2のトランジスタよりもスイッチング速度が速い。第1のトランジスタと第2のトランジスタと容量素子とは直列に電気的に接続されている。容量素子への電荷の蓄積、及び容量素子からの電荷の放出は、第1のトランジスタと第2のトランジスタの両方を介して行われる。こうして、半導体装置の消費電力を少なく、且つ情報の書き込み及び読み出し速度を高速化することができる。

(もっと読む)

半導体装置

【課題】トランジスタの損傷、破壊の発生を抑制することができる半導体装置を提供する。

【解決手段】第1の基板11上の第1の絶縁層12と、第1の絶縁層上のトランジスタ13と、トランジスタ上の第2の絶縁層14と、第2の絶縁層14に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に接続された第1の導電層15〜18と、第1の導電層上の第3の絶縁層38と、第3の絶縁層38上の第2の基板19と、を有し、トランジスタは、半導体層20と、第2の導電層22と、半導体層20と第2の導電層22の間に設けられた第4の絶縁層21とを有し、第1の絶縁層12、第2の絶縁層14、第3の絶縁層38及び第4の絶縁層21から選択された一つ又は複数は、トランジスタと重ならないように設けられた段差部を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程におい

て、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。酸素ドープ処

理されたゲート絶縁膜、熱処理による脱水化または脱水素化処理された酸化物半導体膜を

有するトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジ

スタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることが

できる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

表示装置

【課題】TFTの閾値電圧がシフトしても、駆動回路の高い信頼性を確保することができ

る表示装置を提供する。

【解決手段】出力回路が有するトランジスタのゲートに、順方向バイアスの電圧または逆

方向バイアスの電圧を与えることができる電源制御回路と、出力回路が有するトランジス

タの閾値電圧の変化量をモニターするためのモニター用トランジスタと、出力回路が有す

るトランジスタの閾値電圧を補正するべく、該トランジスタのゲートに逆方向バイアスの

電圧を与えるように電源制御回路を制御する閾値制御回路と、を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供す

ることを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導

体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードであ

る。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれ

る電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度

化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導

体よりもバンドギャップが大きい。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】化学量論的組成比を超える酸素を含む領域を有する非晶質酸化物半導体層と、該非晶質酸化物半導体層上に設けられた酸化アルミニウム膜とを含んで構成される半導体装置を提供する。該非晶質酸化物半導体層は、脱水又は脱水素化処理を行った結晶性又は非晶質酸化物半導体層に対して、酸素注入処理を行い、その後、酸化アルミニウム膜を設けた状態で450℃以下の熱処理を行うことで形成される。

(もっと読む)

半導体装置およびその駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のチャネル形成領域と、第1のゲート電極と、第1のソース領域およびドレイン領域と、を有する第1のトランジスタと、少なくとも第1のソース領域またはドレイン領域の一部と重畳するように設けられた、酸化物半導体材料からなる第2のチャネル形成領域と、第2のソース電極と、第1のゲート電極に電気的に接続される第2のドレイン電極と、第2のゲート電極と、を有する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間の絶縁層と、を含むメモリセルを有し、第2のトランジスタをオフ状態とすべき期間において、少なくとも第1のソース領域またはドレイン領域に正の電位が与えられるときに第2のゲート電極に負の電位が与えられる半導体装置。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、特性の改善された酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを課題の一つとする。

【解決手段】絶縁表面を有する基板上にゲート電極層を形成し、ゲート電極層上にゲート絶縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層上にソース電極層及びドレイン電極層を形成し、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸素を含む絶縁層を形成し、酸素を含む絶縁層上に水素を含む絶縁層を形成した後、熱処理を行うことにより、水素を含む絶縁層中の水素を少なくとも酸化物半導体層に供給することを特徴とする半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程において、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。熱処理による脱水化または脱水素化処理を行った酸化物半導体膜を含み、且つ、作製工程において酸素ドープ処理されたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることができる。

(もっと読む)

181 - 200 / 2,010

[ Back to top ]