Fターム[5F110EE45]の内容

Fターム[5F110EE45]に分類される特許

241 - 260 / 2,010

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、酸化物半導体膜に酸素ドープ処理を行い、その後、酸化物半導体膜及び酸化物半導体膜上に設けられた酸化アルミニウム膜に対して熱処理を行うことで、化学量論的組成比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

電界効果トランジスタの製造方法及びそれに用いる製造装置

【課題】生産性が高く微細な電界効果トランジスタとその製造方法ならびに製造装置を提供すること。

【解決手段】以下の工程(1)から(3)よりなる印刷工程により前記基板上へラインもしくはスペース最小幅が1から50μmであり、印刷位置精度が100ppm以下の機能性膜の形成を行うことを特徴とする電界効果トランジスタの製造方法としたもの。

工程(1) 版の画線部に相当する溝構造部にドクターブレードを用いたインキング法で、機能性材料が溶媒へ溶解もしくは分散した薬液を充填する工程。

工程(2) 転写シリンダーと前記版を接触させ、前記溝構造部の薬液を前記転写シリンダーへ転移させる工程。

工程(3) 前記転写シリンダー上の薬液を前記基板の所定の位置へ転写し、機能性膜の形成を行う工程。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

微結晶半導体膜、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製方法を提供することを課題とする。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、種結晶上に、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を形成し、第2の微結晶半導体膜上に、第2の微結晶半導体膜に含まれる混相粒の隙間を埋めつつ、結晶成長を促す第4の条件で、第3の微結晶半導体膜を積層形成する。

(もっと読む)

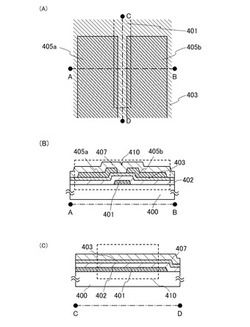

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに画像表示装置

【課題】薄膜トランジスタにおいて、ゲート絶縁膜に直接ストライプ状に凹部を形成することで隔壁形成プロセスを省き、前記凹部をガイドとして塗布法により精度よく半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタの構造を提供する。また、その構造を用いた薄膜トランジスタの製造方法、及びそれを用いたが画像表示装置を提供すること。

【解決手段】基板と、前記基板上に形成されたゲート電極と、前記基板上及び前記ゲート電極上のゲート絶縁体層と、前記ゲート絶縁体層に形成された凹部と、前記絶縁体層の凹部内に形成される半導体層と、前記半導体層上の中央部に設けられる保護膜と、前記半導体層の両端部で接続されるソース電極とドレイン電極と、を有する薄膜トランジスタにおいて、前記ゲート絶縁体層の凹部がストライプ状に形成されていることを特徴とする薄膜トランジスタとする。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

電界効果型トランジスタ、表示装置、センサ及び電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの移動度を向上させる。

【解決手段】ゲート絶縁膜22と、活性層としてSn,Zn及びO、又はSn,Ga,Zn及びOを主たる構成元素とする酸化物半導体層14と、ゲート絶縁膜22と酸化物半導体層14との間に配置され、酸化物半導体層14よりも抵抗率が高い酸化物中間層16と、を有する。

(もっと読む)

電界効果型トランジスタ、電界効果型トランジスタの製造方法、固体撮像装置、及び電子機器

【課題】 ゲート電極の微細化が可能な電界効果型トランジスタを提供する。

【解決手段】 本開示に係る電界効果型トランジスタは、基板10と、基板10上に形成され、フィン領域13と該フィン領域13の両端にそれぞれ形成されるソース領域14とドレイン領域15とを有する半導体層と、フィン領域13の少なくとも2面の一部と接する凸部171を有するゲート電極17と、を備える。

(もっと読む)

半導体装置

【課題】縦型PN接合において確実にオン/オフの制御をすることができる半導体装置を提供する。

【解決手段】半導体装置は、半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極とを備える。第1導電型の第1のチャネル領域が、ゲート絶縁膜の下にある半導体層の表面の一部に設けられている。第1導電型とは異なる導電型である第2導電型の拡散層が、第1のチャネル領域のさらに下の半導体層に設けられ、半導体層の表面に対してほぼ垂直方向に第1のチャネル領域の底部と接し、該第1のチャネル領域の底部とPN接合を形成する。第1導電型のドレインおよび第2導電型のソースが、第1のチャネル領域の両側にある半導体層内にそれぞれ設けられている。側壁絶縁膜は、第1のチャネル領域の拡散層側の側面を被覆する。

(もっと読む)

酸化物半導体薄膜の製造方法、電界効果型トランジスタ、表示装置及びセンサ

【課題】SGZO系酸化物半導体薄膜において、低温アニールによる低抵抗化が起こらず、成膜時の抵抗値と低温アニール後の抵抗値が同等となる組成を明らかとし、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した製造方法を提供する。

【解決手段】構成元素の組成比をSn:Ga:Zn=a:b:cとした場合、組成比が、a+b=2、且つ1≦a≦2、且つ1≦c≦11/2、且つc≧−7b/4+11/4を満たす酸化物半導体薄膜を基板上に成膜する成膜工程と、成膜工程後、酸化性雰囲気中で100℃以上300℃未満の熱処理を施す熱処理工程と、を有する。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、表示装置、センサ及びX線デジタル撮影装置

【課題】基板の選択性を広げつつ、電界効果移動度が高くノーマリーオフ駆動する薄膜トランジスタ等を得る。

【解決手段】活性層の成膜工程での成膜室中の雰囲気の全圧に対する酸素分圧をPo2depo(%)とし、熱処理工程中の雰囲気の全圧に対する酸素分圧をPo2anneal(%)としたときに、熱処理工程時の酸素分圧Po2anneal(%)が、−20/3Po2depo+40/3≦Po2anneal≦−800/43Po2depo+5900/43の関係を満たすように成膜工程と熱処理工程とを行う。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

半導体装置

【課題】半導体基板上へのVFETと他の種類の素子との混載が可能でありながら、半導体基板上に積層される半導体層の表面に大きな段差を有しない半導体装置を提供する。

【解決手段】P型シリコン基板2上には、酸化シリコンからなるボックス層3、N+型横方向導電層4およびN−型表面層5が積層されている。ボックス層3上には、N−型表面層5の表面からボックス層3に至る深さを有する、平面視環状のディープトレンチ6が形成されている。ディープトレンチ6およびボックス層3に取り囲まれるトランジスタ形成領域8は、その周囲から分離されている。このトランジスタ形成領域8において、N−型表面層5の表層部には、ソース領域14およびドレイン領域16が形成されている。またディープトレンチ6の側面に沿って、ドレイン領域16とN+型横方向導電層4とに接続されたN+型縦方向導電層17が形成されている。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

241 - 260 / 2,010

[ Back to top ]