Fターム[5F110FF04]の内容

Fターム[5F110FF04]に分類される特許

121 - 140 / 2,805

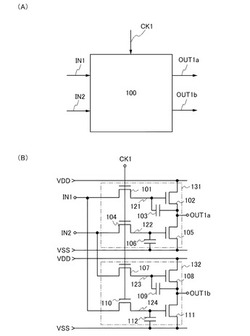

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

半導体装置

【課題】液晶等の電気光学素子若しくは発光素子等を表示媒体として用いる表示装置及びその駆動方法を提供する。

【解決手段】劣化しやすいトランジスタのゲート電極に、オンしたトランジスタを介して信号を入力することで、劣化しやすいトランジスタのしきい値電圧のシフト及びオンしたトランジスタのしきい値電圧のシフトを抑制する。すなわち、高電位(VDD)がゲート電極に印加されているトランジスタを介して(若しくは抵抗成分を持つ素子を介して)、交流パルスを劣化しやすいトランジスタのゲート電極に加える構成を含んでいる。

(もっと読む)

非線形素子

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供

する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有するトランジ

スタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体に接

するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、χはφms以上

かつφmd未満の関係になるように構成し、酸化物半導体とソース電極の接触面積よりも

酸化物半導体とドレイン電極の接触面積を大きくし、トランジスタのゲート電極とドレイ

ン電極を電気的に接続することで、整流特性の良い非線形素子を実現することができる。

(もっと読む)

酸化物半導体層、半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

表示装置

【課題】熱処理による特性変動を抑制した酸化物半導体を用いた表示装置を提供する。

【解決手段】実施形態によれば、絶縁層と、絶縁層上のゲート電極と、ゲート電極上にゲート絶縁膜を介して設けられ酸化物層より形成された半導体層と、半導体層の上において、ゲート電極を挟むように離間して設けられたソース電極及びドレイン電極と、を含む薄膜トランジスタと、ソース電極及びドレイン電極のいずれかに接続され、前記酸化物層より形成され前記半導体層よりも電気抵抗が低い画素電極と、画素電極に与えられる電気信号によって光学特性の変化と発光との少なくともいずれかを生ずる光学素子と、画素電極の下に設けられゲート絶縁膜と同じ材料で形成された膜と、を備え、ゲート電極の上のゲート絶縁膜の半導体層の側の表面は、画素電極の下に設けられた膜の画素電極の側の表面よりも平滑性が高い表示装置が提供される。

(もっと読む)

半導体装置、及びダイオード

【課題】酸化亜鉛を含む半導体膜を用いたダイオードを提供する。

【解決手段】基板上の、酸化亜鉛を含み、チャネル形成領域を有する半導体膜と、前記半

導体膜とゲート電極との間のゲート絶縁膜と、前記半導体膜と電気的に接続されるソース

電極及びドレイン電極と、を有し、前記ゲート電極は、前記ソース電極及び前記ドレイン

電極の一方と電気的に接続される。前記ゲート電極は前記チャネル形成領域の上又は下に

あり、前記ゲート電極は前記ソース電極及び前記ドレイン電極の上にあってもよい。

(もっと読む)

半導体装置

【課題】導電性が高い酸化物半導体層を有する酸化物半導体トランジスタを提供する。

【解決手段】インジウム、ガリウム、亜鉛を含む酸化物(IGZO)及び酸化インジウムの粒子を有する酸化物半導体層と、当該酸化物半導体層中のチャネル形成領域と、ゲート絶縁膜を挟んで重畳するゲート電極と、当該酸化物半導体層中のソース領域及びドレイン領域に重畳するソース電極及びドレイン電極とを有する半導体装置に関する。当該半導体装置は、トップゲート型酸化物半導体トランジスタ又はボトムゲート型酸化物半導体トランジスタであってもよい。また当該酸化物半導体層は、ソース電極及びドレイン電極の上に形成されていてもよいし、ソース電極及びドレイン電極の下に形成されていてもよい。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を

含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成

領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領

域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成

された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、

を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜

厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳

する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

表示装置およびその製造方法

【課題】微結晶シリコンを用いたボトムゲート型の薄膜トランジスタのオン電流に対するオフ電流の割合を減少させること。

【解決手段】表示装置に含まれる薄膜トランジスタは、ゲート電極が設けられた導電層と、前記導電層の上に設けられたゲート絶縁層と、前記ゲート絶縁層の上面に接するとともに前記ゲート電極の上方に設けられ、微結晶シリコンを含む第1の半導体膜と、前記第1の半導体膜の上面に接する第2の半導体膜と、前記第2の半導体膜に電気的に接続される第1の電極と、前記第2の半導体膜に電気的に接続される第2の電極と、を含む。前記第1の半導体膜における水素濃度は、前記ゲート絶縁層との界面と前記第2の半導体膜との界面との中間で最小となり、前記第1の半導体膜と前記第2の半導体膜との境界における酸素濃度は、前記第1の半導体膜の中央および前記第2の半導体膜の中央のうち少なくとも一方の酸素濃度以下である。

(もっと読む)

表示装置

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素

子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査

線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソー

スまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第

2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソース

またはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジ

スタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、

前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供

給される信号の出力が停止される期間を有する。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を提供することを課題の一とする。

【解決手段】半導体層を酸化物半導体層とする逆スタガ型薄膜トランジスタを含む半導体

装置において、酸化物半導体層上にバッファ層を有する。バッファ層は、半導体層のチャ

ネル形成領域と、ソース電極層及びドレイン電極層とに接する。バッファ層は膜内に抵抗

分布を有し、半導体層のチャネル形成領域上に設けられる領域の電気伝導度は半導体層の

チャネル形成領域の電気伝導度より低く、ソース電極層及びドレイン電極層と接する領域

の電気伝導度は半導体層のチャネル形成領域の電気伝導度より高い。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用ボトムコンタクト型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。多階調マスクを用いたフォトリソグラフィ工程を用いることで、作製工程を簡略化できる。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

アクティブマトリックス型表示素子およびその製造方法

【課題】少ない工程数でアクティブマトリクス表示素子を形成する。

【解決手段】実施形態にかかるアクティブマトリックス型表示素子の製造方法は、絶縁基板上にゲート電極層、第1の絶縁膜、酸化物半導体層、第2の絶縁膜、酸化物半導体層と電気的に接続したソース・ドレイン電極を順に形成する工程を含む。酸化物半導体層は、ソース・ドレイン電極が形成される領域から画素領域にわたって形成され、第2の絶縁膜を形成する前に、酸化物半導体の画素領域に相当する部分を低抵抗処理して第1の画素電極を形成する。

(もっと読む)

半導体装置の製造方法及びプラズマドーピング装置

【課題】フィン型半導体領域の側面に不純物を導入して低抵抗の不純物領域を形成できるようにし、それによって、所望の特性を持つフィン型半導体装置を実現する。

【解決手段】基板11上にフィン型半導体領域13を形成した後、不純物含有ガスと酸素含有ガスとを用いて、フィン型半導体領域13に対してプラズマドーピングを行うことによって、フィン型半導体領域13の少なくとも側部に不純物導入領域27Bを形成する。

(もっと読む)

酸化物半導体膜の処理方法および半導体装置の作製方法

【課題】トランジスタに用いることが可能な、低抵抗領域を有する酸化物半導体膜を提供する。また、高速動作が可能な、酸化物半導体膜を用いたトランジスタを生産性高く提供する。また、高速動作が可能な、酸化物半導体膜を用いたトランジスタを有する高性能の半導体装置を生産性高く提供する。

【解決手段】酸化物半導体膜上に還元性を有する膜を成膜し、次に酸化物半導体膜から還元性を有する膜へ酸素の一部を移動させ、次に還元性を有する膜を介して酸化物半導体膜に不純物を注入した後、還元性を有する膜を除去することで、酸化物半導体膜に低抵抗領域を形成する。

(もっと読む)

121 - 140 / 2,805

[ Back to top ]