Fターム[5F110FF13]の内容

Fターム[5F110FF13]に分類される特許

1 - 20 / 39

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

メモリ装置、及びメモリ装置の作製方法

【課題】可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いる。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

(もっと読む)

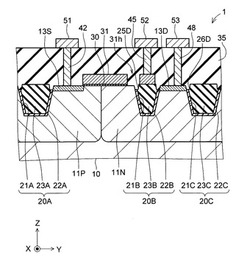

半導体装置

【課題】長期に亘って信頼性の高い横型MISFETを有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、半導体基板11上に形成された半導体層13と、半導体層13に溝状に形成され、その内壁が絶縁膜31で被覆され、絶縁膜31の内部にゲート電極32が埋設されたトレンチ溝30と、半導体層13上に、トレンチ溝30と少なくとも一部が対向配置する位置に形成されたゲート配線51と、ゲート配線51を挟むように半導体層13上に形成されたソース電極52、及びドレイン電極53とを具備する。半導体層13におけるオン動作時の電流経路は、ソース電極52とドレイン電極53の間の半導体層13の表面領域を実質的に経由せず、上記トレンチ溝30の側面近傍を経由する。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】特性が良好であって、かつ大電力用途向けの半導体装置を提供することを課題とする。

【解決手段】半導体装置、具体的には縦型トランジスタのゲート電極層の一部を、ソース電極層、ドレイン電極層およびチャネル領域となる半導体層の一部と重畳する構造にすることである。つまり、ソース電極層と、ソース電極層に接した酸化物半導体層と、酸化物半導体層に接したドレイン電極層と、一部がソース電極層、ドレイン電極層および酸化物半導体層と重畳したゲート電極層と、ゲート電極層の全ての面に接するゲート絶縁層と、を有する半導体装置を提供することである。

(もっと読む)

半導体装置

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲む第1のゲート電極と、第1のゲート電極の周囲を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲を取り囲む第1の筒状半導体層と、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第1の筒状半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第1の筒状半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有するインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供する。

【解決手段】第1の島状半導体層137の周囲上に少なくとも一部に接して第1のゲート絶縁膜187が存在し、第1のゲート絶縁膜187に第1のゲート電極178の一面が接し、第1のゲート電極178の他面に第2のゲート絶縁膜187が接し、第2のゲート絶縁膜187に少なくとも第2の半導体層141が接して、第1の島状半導体層137の上部に配置された第1の第1導電型高濃度半導体層161と、第1の島状半導体層137の下部に配置された第2の第1導電型高濃度半導体層162と、第2の半導体層141の上部に配置された第1の第2導電型高濃度半導体層154と、第2の半導体層141の下部に配置された第2の第2導電型高濃度半導体層156と、を有するインバータを用いてSRAMを形成する。

(もっと読む)

半導体素子、半導体装置および半導体素子の製造方法

【課題】ESD保護素子が集積された回路全体の製造コストを低減する。

【解決手段】ESD保護素子100は、nチャネルGGFET構造を有している。ESD保護素子100において、第1p+低抵抗領域41は、第1pウエル領域4の一部に、第1p++コンタクト領域5とその下の領域、n++ソース領域8とその下の領域、第1LDD領域6とその下の領域、第1ゲート絶縁膜12の下の領域、第2LDD領域7とその下の領域、およびn++ドレイン領域9の一部とその下の領域に設けられている。第1p+低抵抗領域41のn++ドレイン領域9側の端部から、第1ゲート電極13のn++ドレイン領域9側の端部までの第1エクステンション距離(LBP1)は、0〜0.3μmの範囲内にある。ESD保護素子100の第1p+低抵抗領域41は、高耐圧デバイスの低抵抗領域と同時に形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】簡単なエッチングレートの管理により所望の形状のコンタクトホールを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板10上にソース電極11s及びドレイン電極dを形成する工程と、ソース電極11sとドレイン電極11dとの間の領域を含む領域に半導体層12を形成する工程と、半導体層12上にゲート絶縁膜13を形成する工程と、ゲート絶縁膜13上にゲート電極14を形成する工程と、ゲート電極14をマスクとして用い、ゲート電極14と重ならない領域のゲート絶縁膜13及び半導体層12をエッチングによって除去する工程と、基板10上に感光性材料15を形成する工程と、感光性材料15をフォトリソグラフィ法によりパターニングしてドレイン電極11dの表面の一部を露出させる孔16を形成する工程と、孔16及び感光性材料15上に画素電極18を形成する工程とを有する。

(もっと読む)

MIS積層構造体の作製方法およびMIS積層構造体

【課題】コスト低減の図れるスイッチング素子の基本構造であるMIS積層構造体およびそれらの作製方法を提供する。

【解決手段】支持基板上に、少なくとも半導体材料層〔S〕、絶縁材料層〔I〕、および導電性酸化物材料層〔M〕(照射するレーザ光を吸収し、薄膜の少なくとも一部がアモルファス相である導電性酸化物材料層)を順次成膜してMIS積層構成体を形成する成膜工程(a)と、集光した状態のレーザ光を前記導電性酸化物材料層側から照射して該導電性酸化物材料層の一部を熱変化させると共に、MIS積層構成体内部に伝播した熱により前記半導体材料層の一部を熱変化させる熱処理工程(b)と、前記MIS積層構成体の熱変化していない部分をエッチング処理で除去するエッチング処理工程(c)とによりMIS積層構造体を作製し、これに電極を設けてスイッチング素子とする。

(もっと読む)

有機トランジスタ及びこのようなトランジスタの誘電層の製造方法

【課題】チャネル上における高い容量、低下した供給電圧及び低下した浮遊容量を可能にする有機薄膜トランジスタを提案する。

【解決手段】本発明は、ドレイン(54)を形成する導電要素と、前記ドレイン(54)と離れて位置するソース(56)を形成する導電要素と、前記ドレイン(54)に面する表面と前記ソース(56)に面する表面とを有するゲート(62)を形成する導電要素と、前記ドレイン(54)及び前記ソース(56)と接触する半導体層(58)と、第1に前記ゲート(62)と前記ソース(56)との間に、第2に前記ゲート(62)と前記ドレイン(54)との間に位置する誘電層(60)であって、その厚さに依存して変化する誘電率を有する誘電層(60)と、を備える有機トランジスタ(50)に関連する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート長が膜厚で規定された縦型の半導体装置であって、良好な信頼性のゲート絶縁膜を備え、微細化が容易な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置10の基板11上の、チャネル領域32に対応する領域を

除いた領域を種結晶領域として用い、チャネル領域32を迂回する形で、

基板11上に選択エピタキシャル成長又は固相エピタキシャル成長によってゲートとなる単結晶膜を結晶成長させる。この単結晶膜をCMPで窒化膜19の膜厚に規定し、この単結晶膜と絶縁膜からなる積層膜に、チャネルとなる任意の大きさの開口を形成する。この開口形成時にできた、単結晶膜の端面を酸化させることによりゲート酸化膜を形成する。

(もっと読む)

有機半導体材料及びその製造方法、並びに有機電子デバイス

【課題】高いキャリア移動度と安定性を有し、容易なプロセスで作製可能な有機半導体材料及び有機デバイスを提供する。

【解決手段】下記一般式で表されるポルフィリン2量体を含む有機半導体材料、及び、ビシクロ構造を有する前駆体としてのポルフィリン2量体を溶媒に溶解した溶液を基板上に塗布し、加熱することにより、上記ポルフィリン2量体に変換する有機半導体材料の製造方法、並びに、半導体層と2以上の電極とを有する有機電子デバイスにおいて、該半導体層が上記有機半導体材料を含む有機電子デバイス。 (もっと読む)

(もっと読む)

薄膜トランジスタ、その製造方法、並びに、それを含む有機電界発光表示装置

【課題】薄膜トランジスタ、その製造方法、並びに、それを含む有機電界発光表示装置を提供する。

【解決手段】基板と、前記基板上に位置し、チャネル領域、ソース/ドレイン領域及びボディコンタクト領域を含む半導体層と、前記半導体層上に位置し、前記ボディコンタクト領域を露出させたゲート絶縁膜と、前記ゲート絶縁膜上に位置し、前記ゲート絶縁膜により露出された前記ボディコンタクト領域と接しているシリコン膜と、前記シリコン膜上に位置しているゲート電極と、前記ゲート電極上に位置している層間絶縁膜と、前記層間絶縁膜上に位置し、前記ソース/ドレイン領域と電気的に接続されたソース/ドレイン電極とを含み、前記ボディコンタクト領域は前記半導体層のエッジ領域内に形成されたことを特徴とする薄膜トランジスタ、その製造方法、並びに、それを含む有機電界発光表示装置に関する。

(もっと読む)

半導体装置、電気光学装置および電子機器

【課題】樹脂層などのフレキシブルな層上に形成された場合であっても信頼性に優れる半導体装置の構成を提供する。

【解決手段】本発明に係る樹脂層(S)上に形成された半導体装置は、複数の下ゲート型薄膜トランジスタを含み、該半導体装置は該下ゲート型薄膜トランジスタを構成する半導体層(17)と、第一の配線(GL1、GL2)と、第二の配線(SL)と、第一絶縁層(15)と、ゲート絶縁膜(19)とを少なくとも有し、該半導体層と該第一の配線と第二の配線の下部には該第一絶縁層と該ゲート絶縁膜が存在し、該半導体層と該第一の配線と第二の配線とが形成されていない箇所では、該第一絶縁層と該ゲート絶縁膜の一部が取り除かれている。該第一絶縁層と該ゲート絶縁膜の一部を取り除いたので、半導体装置に、機械的、または熱的な応力が加えられた場合であっても、当該応力が緩和され、第一絶縁層等におけるクラックの発生を低減できる。

(もっと読む)

薄膜トランジスタ及び表示装置

【課題】薄膜トランジスタのオン電流及びオフ電流に係る問題点を解決する。また、高速動作が可能な薄膜トランジスタを提供する。

【解決手段】ゲート絶縁層を介してゲート電極と重畳するアクセプターとなる不純物元素を添加した半導体層と、アクセプターとなる不純物元素を添加した半導体層上に重ねて設けられたバッファ層と、バッファ層の上面と、バッファ層及びアクセプターとなる不純物元素を添加した半導体層の側面を被覆する非晶質半導体層と、一端部がバッファ層と重なり、非晶質半導体層上に設けられ、ソース領域及びドレイン領域を形成する一導電型を付与する不純物元素を添加した一対の不純物半導体層とを有し、バッファ層の膜厚が、非晶質半導体層の膜厚よりも厚い薄膜トランジスタである。

(もっと読む)

薄膜トランジスタ及び表示装置

【課題】薄膜トランジスタのオン電流及びオフ電流に係る問題点を解決する。また、高速動作が可能な薄膜トランジスタを提供する。

【解決手段】ゲート絶縁層を介してゲート電極と重畳するドナーとなる不純物元素を添加した半導体層と、ドナーとなる不純物元素を添加した半導体層上に重ねて設けられたバッファ層と、バッファ層の上面と、バッファ層及びドナーとなる不純物元素を添加した半導体層の側面を被覆する非晶質半導体層と、一端部がバッファ層と重なり、非晶質半導体層上に設けられ、ソース領域及びドレイン領域を形成する一導電型を付与する不純物元素を添加した一対の不純物半導体層とを有し、バッファ層の膜厚が、非晶質半導体層の膜厚よりも厚い薄膜トランジスタである。

(もっと読む)

ナノチューブ縦型電界効果トランジスタの形成方法

ナノチューブ電界効果トランジスタおよび製造方法を開示する。本方法は、開口部によって画定される導電層の領域と接触するようにするナノチューブの電気泳動堆積を含む。  (もっと読む)

(もっと読む)

1 - 20 / 39

[ Back to top ]