Fターム[5F110GG07]の内容

Fターム[5F110GG07]に分類される特許

61 - 80 / 557

駆動回路、当該駆動回路の作製方法および当該駆動回路を用いた表示装置

【課題】作製中にESDにより半導体素子が破壊されることを抑制する駆動回路および当該駆動回路の作製方法を提供する。また、リーク電流の小さい保護回路が設けられた駆動回路および当該駆動回路の作製方法を提供する。

【解決手段】駆動回路中の半導体素子と電気的に接続して、駆動回路中に保護回路を設け、駆動回路中の半導体素子となるトランジスタと駆動回路中の保護回路を形成するトランジスタを同時に形成することにより、駆動回路の作製中にESDにより半導体素子が破壊されることを抑制する。さらに、駆動回路中の保護回路を形成するトランジスタに酸化物半導体膜を用いることにより、保護回路のリーク電流を低減する。

(もっと読む)

表示装置

【課題】被検出物が表示パネルに非接触の場合でも、被検出物の位置及び動きの検出を行うことを可能とする表示装置を提供する。

【解決手段】表示装置は、フォトセンサ及び酸化物半導体層を含む薄膜トランジスタが配置された表示パネルを有し、被対象物が表示パネルに接近する際に、被検出物が外光を遮ることで表示パネルに投影される被検出物の影がフォトセンサによって検出される。影の位置又は動きを検出することで、被検出物の位置又は動きが検出され、被検出物が表示パネルに非接触の場合でも検出可能となる。

(もっと読む)

半導体装置

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

電界効果型トランジスタの製造方法、並びに、電界効果型トランジスタ、表示装置、イメージセンサ及びX線センサ

【課題】光照射時のTFT特性を安定化する。

【解決手段】ゲート電極14上に配置されたゲート絶縁層16上に、第一の酸化物半導体膜24を成膜する第一工程と、第一の酸化物半導体膜24とカチオン組成が異なり、且つ第一の酸化物半導体膜24より低い電気伝導度を有する第二の酸化物半導体膜26を成膜する第二工程と、酸化性雰囲気の下300℃超で熱処理する第三工程と、第一の酸化物半導体膜24とカチオン組成が異なり、且つ第一の酸化物半導体膜24より低い電気伝導度を有する第三の酸化物半導体膜28を成膜する第四工程と、酸化性雰囲気の下300℃超で熱処理する第五工程と、第三の酸化物半導体膜28上に、ソース電極20及びドレイン電極22を形成する電極形成工程と、を有している。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置

を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびド

レイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、

ゲート絶縁層上のゲート電極と、を有し、酸化物半導体層の厚さは1nm以上10nm以

下であり、ゲート絶縁層は、ゲート絶縁層に用いられる材料の比誘電率をεr、ゲート絶

縁層の厚さをdとして、εr/dが、0.08(nm−1)以上7.9(nm−1)以下

の関係を満たし、ソース電極とドレイン電極との間隔は10nm以上1μm以下である半

導体装置である。

(もっと読む)

半導体素子の製造方法及び電界効果型トランジスタの製造方法

【課題】光照射時の素子特性を安定化する。

【解決手段】酸化物半導体を主体とする半導体膜を成膜する第一工程と、第一工程後に、半導体膜の面上に第一の絶縁膜を成膜する第二工程と、第二工程後に、酸化性雰囲気中で熱処理する第三工程と、第三工程後に、第一の絶縁膜の面上に第二の絶縁膜を成膜する第四工程と、を有し、第二工程と前記第三工程の際に、第一の絶縁膜の厚みをZ(nm)とし、第三工程での熱処理温度をT(℃)とし、前記第一の絶縁膜及び前記半導体膜中への酸素の拡散距離をL(nm)としたとき、0<Z<L=8×10−6×T3−0.0092×T2+3.6×T−468±0.1の関係式を満たすように第一の絶縁膜の厚みと熱処理温度を調整する。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】良好な特性を有する複数の有機トランジスタを備えた有機半導体素子の製造方法を提供する。

【解決手段】有機半導体素子10は、基板11と、基板11上に設けられ、各々が有機半導体材料を含む有機半導体領域4を有する複数の有機トランジスタ20と、を備えている。このうち有機半導体領域4は、少なくとも基板11を含む支持部材17によって支持されている。そして、有機半導体素子10の製造方法は、支持部材17を準備する工程と、支持部材17上に有機半導体材料を含む連続的な有機半導体層30を設ける工程と、有機半導体層30をパターニングして複数の有機半導体領域4を形成するパターニング工程と、を備えている。ここで、パターニング工程は、凹部42および凸部41を有する凹凸版40を準備する工程と、凹凸版40の凸部41を支持部材17上の有機半導体層30に当接させることにより有機半導体層30をパターニングする当接工程と、を有している。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

金属酸化物薄膜形成用塗布液、金属酸化物薄膜、電界効果型トランジスタ、及び電界効果型トランジスタの製造方法

【課題】所望の体積抵抗率を有する金属酸化物薄膜を、簡便かつ大面積に作製でき、更に所望の形状の金属酸化物を形成する精度が高い金属酸化物薄膜形成用塗布液などの提供。

【解決手段】無機インジウム化合物と、無機マグネシウム化合物及び無機亜鉛化合物の少なくともいずれかと、グリコールエーテル類とを含有する金属酸化物薄膜形成用塗布液である。

(もっと読む)

非晶質酸化物薄膜の製造方法及び薄膜トランジスタ

【課題】非晶質酸化物薄膜の膜質を向上する。

【解決手段】有機成分とInとを含有する第1酸化物前駆体膜4に対して有機成分の熱分解温度未満で有機成分の結合状態を選択的に変化させ、フーリエ変換型赤外分光で測定したときに得られる赤外線吸収スペクトルにおいて、赤外線の波数1380cm−1以上1520cm−1以下の範囲を赤外線の波数1380cm−1以上1450cm−1以下の範囲と赤外線の波数1450cm−1超1520cm−1以下の範囲とに分割したときに、赤外線の波数1380cm−1以上1450cm-1以下の範囲に位置するピークが、赤外線の波数1350cm−1以上1750cm−1以下の範囲における赤外線吸収スペクトルの中で最大値を示す第2酸化物前駆体膜6を得る前処理工程と、第2酸化物前駆体膜中に残存する有機成分を除去して、第2酸化物前駆体膜6を非晶質酸化物薄膜8へ変化させる後処理工程とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインが、第1半導体結晶層を構成する原子とニッケル原子との化合物、第1半導体結晶層を構成する原子とコバルト原子との化合物または第1半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、第2半導体結晶層を構成する原子とニッケル原子との化合物、第2半導体結晶層を構成する原子とコバルト原子との化合物、または、第2半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提

供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのス

イッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置

の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電

極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体

膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と

半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極

と、を有する。

(もっと読む)

半導体装置

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜に、金属元素を含む膜と接した状態で加熱処理することにより導入された金属元素と、注入法により該金属元素を含む膜を通過して導入されたドーパントとを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

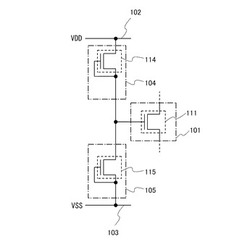

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく

、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトラ

ンジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジ

スタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の

端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導

体記憶装置である。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

61 - 80 / 557

[ Back to top ]