Fターム[5F110GG15]の内容

Fターム[5F110GG15]に分類される特許

121 - 140 / 2,884

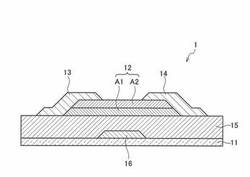

薄膜トランジスタ及びその製造方法、表示装置、イメージセンサー、X線センサー並びにX線デジタル撮影装置

【課題】400℃以下で作製可能であり、30cm2/Vs以上の高い電界効果移動度と、ノーマリーオフとなる低いオフ電流を両立する薄膜トランジスタを提供する。

【解決手段】ゲート電極16と、ゲート電極と接するゲート絶縁膜15と、In(x)Zn(1−x)O(y)(0.4≦x≦0.5,y>0)で表される第1の領域A1及びIn(a)Ga(b)Zn(c)O(d)(b/(a+b)>0.250,c>0,d>0)で表され、ゲート電極に対して第1の領域よりも遠くに位置する第2の領域A2を含み、ゲート絶縁膜を介してゲート電極に対向配置されている酸化物半導体層12と、互いに離間して配置されており、酸化物半導体層を介して導通可能なソース電極13及びドレイン電極14と、を有する薄膜トランジスタ1。

(もっと読む)

表示装置

【課題】フリンジフィールドスイッチングモードで駆動する液晶表示装置の作製方法において、フォトマスク数を削減することで製造工程の簡略化及び製造コストの削減をする。

【解決手段】透光性を有する絶縁基板上に第1の透明導電膜及び第1の金属膜を順に成膜し積層し、第1のフォトマスクである多階調マスクを用いて第1の透明導電膜及び第1の金属膜を形状加工し、絶縁膜、第1の半導体膜、第2の半導体膜、第2の金属膜を順に成膜し積層し、第2のフォトマスクである多階調マスクを用いて第2の金属膜、第2の半導体膜を形状加工し、保護膜を成膜し、第3のフォトマスクを用いて保護膜を形状加工し、第2の透明導電膜を成膜し、第4のフォトマスクを用いて第2の透明導電膜を形状加工する。

(もっと読む)

半導体装置

【課題】特性の良い半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】基板上に、ゲート電極として機能する第1の導電層を形成する工程と、第1

の導電層を覆うように第1の絶縁層を形成する工程と、第1の導電層と一部が重畳するよ

うに、第1の絶縁層上に半導体層を形成する工程と、半導体層と電気的に接続されるよう

に第2の導電層を形成する工程と、半導体層および第2の導電層を覆う第2の絶縁層を形

成する工程と、第2の導電層と電気的に接続される第3の導電層を形成する工程と、半導

体層を形成する工程の後、第2の絶縁層を形成する工程の前の第1の熱処理工程と、第2

の絶縁層を形成する工程の後の第2の熱処理工程と、を有する。

(もっと読む)

薄膜トランジスタ及びその製造方法、表示装置、イメージセンサー、X線センサー並びにX線デジタル撮影装置

【課題】400℃以下で作製可能であり、20cm2/Vs以上の高い電界効果移動度と、ノーマリーオフとなる低いオフ電流を両立する薄膜トランジスタを提供する。

【解決手段】ゲート電極16と、ゲート絶縁膜15と、In(a)Ga(b)Zn(c)O(d)(a>0,b>0,c>0,a+b+c=1,d>0)で表され、a≦37/60、b≦91a/74−17/40、b≧3a/7−3/14、c≦3/5を満たす第1の領域A1及びIn(p)Ga(q)Zn(r)O(s)(q/(p+q)>0.250,p>0,q>0,r>0,s>0)で表され、ゲート電極に対して第1の領域よりも遠くに位置する第2の領域A2を含み、ゲート絶縁膜を介してゲート電極に対向配置されている酸化物半導体層と、酸化物半導体層を介して導通可能なソース電極13及びドレイン電極14と、を有する薄膜トランジスタ1。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

半導体装置およびその作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】加熱処理により酸素を放出する絶縁体基板と、該絶縁体基板上に設けられた酸化物半導体膜と、を有し、該酸化物半導体膜にチャネルが形成されるトランジスタを有する半導体装置である。加熱処理により酸素を放出する絶縁体基板は、絶縁体基板の少なくとも酸化物半導体膜が設けられる側に、酸素イオン注入を行うことで作製することができる。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタにおいて、酸化物半導体層の上面部及び下面部に、酸化物半導体層と同種の成分でなるバッファ層が接して設けられたトランジスタ、及び該トランジスタを含む半導体装置を提供する。酸化物半導体層に接するバッファ層としては、アルミニウム、ガリウム、ジルコニウム、ハフニウム、又は希土類元素から選択された一以上の元素の酸化物を含む膜を適用することができる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

半導体装置の作製方法

【課題】薄膜トランジスタのしきい値電圧を制御するため、薄膜トランジスタのチャネル形成領域の上下にゲート絶縁膜を介してゲート電極を設けた際に、プロセス数の増加を招くことなく、電気特性の優れた薄膜トランジスタを備えた半導体装置を得る。

【解決手段】酸化物半導体層131の上方に設ける第2のゲート電極133を形成するとき、酸化物半導体層131のパターニングと同時に形成することで、第2のゲート電極133の作製に要するプロセス数の増加を削減する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】ソース電極層又はドレイン電極層に接する第1の酸化物半導体層と、第1の酸化物半導体層上に設けられ第1の酸化物半導体層とは異なるエネルギーギャップを有する第2の酸化物半導体層と、を少なくとも含む酸化物半導体積層を用いてトランジスタを構成する。第1の酸化物半導体層と第2の酸化物半導体層とは互いに異なるエネルギーギャップを有すればよく、その積層順は問わない。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】少なくともゲート電極層、ゲート絶縁膜、及び半導体層が順に積層されたボトムゲート型のトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

駆動回路、当該駆動回路の作製方法および当該駆動回路を用いた表示装置

【課題】作製中にESDにより半導体素子が破壊されることを抑制する駆動回路および当該駆動回路の作製方法を提供する。また、リーク電流の小さい保護回路が設けられた駆動回路および当該駆動回路の作製方法を提供する。

【解決手段】駆動回路中の半導体素子と電気的に接続して、駆動回路中に保護回路を設け、駆動回路中の半導体素子となるトランジスタと駆動回路中の保護回路を形成するトランジスタを同時に形成することにより、駆動回路の作製中にESDにより半導体素子が破壊されることを抑制する。さらに、駆動回路中の保護回路を形成するトランジスタに酸化物半導体膜を用いることにより、保護回路のリーク電流を低減する。

(もっと読む)

発光装置

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複数種の薄膜トランジスタを備えた発光装置を提供することを課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャネルエッチ型を用い、画素用薄膜トランジスタと電気的に接続する発光素子と重なる位置にカラーフィルタ層を薄膜トランジスタと発光素子の間に設ける。

(もっと読む)

半導体装置及びその作製方法

【課題】チャネル長の短い酸化物半導体トランジスタにおいて、十分なオン/オフ比が取れないことを抑制する。

【解決手段】酸化物半導体層と、当該酸化物半導体層のチャネル形成領域と重畳するゲート電極と、当該酸化物半導体層の第1の領域と重畳するソース電極又はドレイン電極と、当該チャネル形成領域と当該第1の領域との間に第2の領域を有し、当該第2の領域の上層は微小な空洞を含んでいる半導体装置に関する。酸化物半導体層と、当該酸化物半導体層のチャネル形成領域と重畳するゲート電極と、当該酸化物半導体層の第1の領域と重畳するソース電極又はドレイン電極と、当該チャネル形成領域と当該第1の領域との間に第2の領域を有し、当該第2の領域の上層は窒素を含んでいる半導体装置に関する。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置

を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびド

レイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、

ゲート絶縁層上のゲート電極と、を有し、酸化物半導体層の厚さは1nm以上10nm以

下であり、ゲート絶縁層は、ゲート絶縁層に用いられる材料の比誘電率をεr、ゲート絶

縁層の厚さをdとして、εr/dが、0.08(nm−1)以上7.9(nm−1)以下

の関係を満たし、ソース電極とドレイン電極との間隔は10nm以上1μm以下である半

導体装置である。

(もっと読む)

121 - 140 / 2,884

[ Back to top ]