Fターム[5F110GG15]の内容

Fターム[5F110GG15]に分類される特許

41 - 60 / 2,884

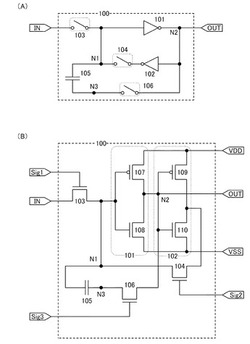

記憶素子および信号処理回路

【課題】消費電力を抑えることができる記憶素子、当該記憶素子を用いた信号処理回路を提供する。

【解決手段】一対のインバータ(クロックドインバータを含む)を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を一対のインバータのいずれかの入力あるいは出力である第1のノードに接続し、他方の電極をスイッチング素子の一方の電極に接続する。スイッチング素子の他方の電極は前記インバータの出力あるいは入力である第2のノードに接続する。ここで、第1のノードの電位と第2のノードの電位は互いに逆の位相である。このような接続により、データ回復時における第1のノードと第2のノードの電位差の絶対値を十分に大きくすることができ、データ回復時のエラーを減らせる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、インジウムを含む酸化物半導体膜、ゲート電極層と重畳する酸化物半導体膜上に接する絶縁層が順に積層され、酸化物半導体膜及び絶縁層に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、絶縁層表面における塩素濃度を1×1019/cm3以下とし、かつインジウム濃度を2×1019/cm3以下とする。

(もっと読む)

装置の作製方法

【課題】剥離前の形状及び特性を保った良好な状態で転置工程を行えるような、剥離工程

を用いて半導体装置及び表示装置を作製できる技術を提供する。よって、より高信頼性の

半導体装置及び表示装置を装置や工程を複雑化することなく、歩留まりよく作製できる技

術を提供することも目的とする。

【解決手段】透光性を有する第1の基板上に光触媒物質を有する有機化合物層を形成し、

光触媒物質を有する有機化合物層上に素子層を形成し、光を第1の基板を通過させて、光

触媒物質を有する有機化合物層に照射し、素子層を前記第1の基板より剥離する。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置

【課題】アライメント精度良く半導体層を形成し、かつ、プロセス数を増やすことなくトランジスタの素子分離を行うことのできる薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置を提供する。

【解決手段】薄膜トランジスタ50は、基板1と、基板1上に形成されたゲート電極2と、基板1とゲート電極2とにわたって、これらの上に形成されたゲート絶縁体層4と、ゲート絶縁体層4上に形成された半導体層5と、半導体層5上に形成された保護層6と、ゲート絶縁体層4と半導体層5と保護層6とにわたって、これらの上に形成された、ソース電極7及びドレイン電極8と、を有し、半導体層5における、ソース電極7とドレイン電極8との間のチャネル部を流れる電流の方向の一端5aは、ソース電極7の一端7aと一致し、半導体層5における他端5bは、ドレイン電極8の一端8aと一致している。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

半導体装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制すること。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜において、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域は、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さくする。

(もっと読む)

薄膜トランジスタアレイ基板の製造方法

【課題】 有機樹脂膜を有するTFTアレイ基板の製造工程において、ブラシ洗浄の際に異物が有機平坦化膜表面にキズを生じさせることがある。このようにキズが生じた有機平坦化膜上に、画素電極となる透明電極膜を成膜した場合、キズ上の透明電極膜も断線してしまい、画素電極に信号が伝わらず表示不良を引き起こすことがある。

【解決手段】 有機平坦化膜を塗布する工程と、中間調露光を用いて有機平坦化膜に凹凸を形成する工程と、凹凸が形成された有機平坦化膜表面をロールブラシを用いて洗浄する工程と、洗浄工程後に、有機平坦化膜上に画素電極を構成する透明導電膜を成膜する工程とを備えた薄膜トランジスタアレイ基板の製造方法を提供する。

(もっと読む)

半導体装置、および半導体装置の作製方法

【課題】水分による電気特性劣化が抑制された半導体装置および半導体装置の作製方法を提供する。

【解決手段】トランジスタを覆う層間絶縁層に接して金属酸化物層が位置する構造とし、金属酸化物層を、アモルファス構造を有する第1の金属酸化物層と、多結晶構造を有する第2の金属酸化物層を含む積層構造とする。アモルファス構造を有する第1の金属酸化物層は結晶粒界が存在せず、また、結晶状態の金属酸化物層と比較して格子間隔が広いため格子間に水分をトラップしやすい。多結晶構造を有する第2の金属酸化物層は、結晶粒界部分を除く結晶部分については緻密な構造を有しており、水分の透過性が非常に低い。このため、第1の金属酸化物層および第2の金属酸化物層を含む金属酸化物層が層間絶縁層に接する構造とすることにより、トランジスタ中への水分の侵入を効果的に防止できる。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

シフトレジスタ回路

【課題】トランジスタのしきい値電圧の制御を行いながら、ゲート電極の電位は変動させず、バックゲート電極の電位のみを変動させることで、入力信号に応じた信号を出力することが可能な論理回路を有するシフトレジスタ回路を提供する。

【解決手段】同じ導電型の第1のトランジスタ及び第2のトランジスタを有する論理回路、を含むシフトレジスタ回路において、第1のトランジスタの第1のゲート電極を、第1のトランジスタのソース電極またはドレイン電極に接続し、第1のトランジスタの第2のゲート電極に入力信号を供給し、第2のトランジスタのゲート電極にクロック信号を供給し、第1のゲート電極と、ゲート電極とは、同じ層とする。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

表示装置およびその製造方法、並びに電子機器

【課題】互いに電気的に接続された薄膜トランジスタの第2電極と配線層との間の電食の発生を防止して、安定した電気特性を得ることできる表示装置およびその製造方法、並びに電子機器を提供する。

【解決手段】薄膜トランジスタおよび配線層を備え、前記薄膜トランジスタは、制御電極

と、前記制御電極と対向する半導体層と、前記半導体層に電気的に接続され、光透過性材

料からなる第1電極と、前記光透過性材料よりも低抵抗の金属膜を含むと共に、前記半導

体層および前記配線層にそれぞれ電気的に接続された第2電極とを備え、前記金属膜の構

成材料と前記配線層の少なくとも一部を構成する導電材料とのイオン化傾向の差は、前記

光透過性材料と前記導電材料とのイオン化傾向の差よりも小さい表示装置。

(もっと読む)

酸化物半導体電界効果型トランジスタ及びその製造方法

【課題】移動度が高く、S値の低い電界効果型トランジスタの提供を目的とする。また、低温又は短時間の熱履歴でも高い特性の得られる電界効果型トランジスタの製造方法の提供を目的とする。

【解決手段】In元素及びZn元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

(もっと読む)

半導体装置

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

液晶表示装置

【課題】製造コストを削減するとともに歩留まりを向上し、かつプロセス設計が容易である液晶表示装置を提供すること。

【解決手段】液晶表示装置1において、半導体層ASIと半導体層ASIの液晶材側の面に形成された金属層Mとの積層部分であり、かつ画素電極MITの液晶材側の面に重なる部分である重なり部50を含むソース電極SD2を有し、第2の絶縁層PAS2は、ソース電極SD2の液晶材側の面から重なり部の50端部、及び画素電極MITの一部を開口するように形成されており、ソース電極SD2の液晶材側の面から重なり部50の端部上、及び画素電極MIT上に、ソース電極SD2の液晶材側の面から重なり部50の端部、及び画素電極MITを導通させる導体膜70が形成されている。

(もっと読む)

表示装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】映像信号線が絶縁膜を介して走査線を乗り越える構成となっている。走査線10はAlCu合金を下層11とし、MoCr合金を上層12とする2層構造である。上層/下層の膜厚比を、0.4以上、1.0以下とすることによって、走査線10の断面において、電池作用によって上層12のエッチング速度が遅くなって、上層12の庇部が形成されることを防止する。これによって、走査線10に生じた庇部に起因して、映像信号線が走査線10との交差部において断線することを防止する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

41 - 60 / 2,884

[ Back to top ]