Fターム[5F110GG16]の内容

Fターム[5F110GG16]に分類される特許

101 - 120 / 747

半導体装置及びその作製方法、ならびに電子機器

【課題】リーク電流が低減された半導体装置を提供すること。また、高い電界効果移動度と低いリーク電流が両立された半導体装置を提供すること。また、低消費電力化された電子機器を提供すること。また、マスク枚数を増やすことなくリーク電流を低減可能な、半導体装置の作製方法を提供すること。

【解決手段】高いキャリア移動度を有する半導体膜からなる半導体層の側面が、ソース電極及びドレイン電極と接しない構造とすればよい。また、フォトマスク数を増やすことなく、このような構成を有するトランジスタ構造を形成し、電子機器に適用すればよい。

(もっと読む)

半導体装置

【課題】半導体装置におけるドレイン電極端での電界集中を緩和する。

【解決手段】第1の領域および第2の領域を有する酸化物半導体膜と、該酸化物半導体膜と一部が接する一対の電極と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介し、一対の電極の一方の一部および第1の領域と重畳するゲート電極と、を有し、第1の領域の少なくとも一部および第2の領域の少なくとも一部は一対の電極間にあり、ゲート電極は、一対の電極の他方と重畳しない構成とする。

(もっと読む)

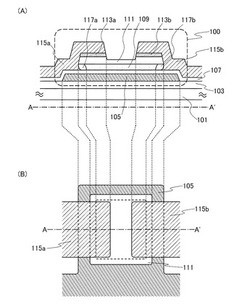

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜を生産性高く作製する方法を提供する。また、該微結晶半導体膜を用いて、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】反応室内に第1の電極及び第2の電極が備えられたプラズマCVD装置を用いて、堆積性気体及び水素を第1の電極及び第2の電極の間に配置された基板を含む反応室内に供給した後、第1の電極に高周波電力を供給することにより反応室内にプラズマを発生させて、基板に微結晶半導体膜を形成する。なお、プラズマが発生している領域において、基板端部と重畳する領域のプラズマ密度を、基板端部と重畳する領域より内側の領域のプラズマ密度より高くし、基板端部より内側の領域に微結晶半導体膜を形成する。また、上記微結晶半導体膜の作製方法を用いて、半導体装置を作製する。

(もっと読む)

レーザ照射装置

【課題】小型のレーザ照射装置で光干渉がなく、連続した結晶成長を実現することである。

【解決手段】メガヘルツレーザビームを用い、分割したレーザビームを半導体膜に照射して、半導体膜を結晶化する。その際に分割ビームに光路差を設けて光干渉を抑える。光路差はメガヘルツレーザビームのパルス幅に相当する長さ以上、パルス発振間隔に相当する長さ未満に設定され、非常に短い光路差で光干渉を抑えることができる。そのためレーザのエネルギー劣化がなく効率的に且つ連続的にレーザビームを照射することができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置(薄膜トランジスタ)を製造する。

【解決手段】本発明は、(a)基板SUBの上方に、第1金属酸化物を含有する半導体からなる導電層を形成する工程と、(b)導電層上に第2金属酸化物を含有する半導体からなる犠牲層SLを形成する工程と、(c)導電層と犠牲層SLとの積層膜を加工する工程と、(d)上記(c)工程の後、犠牲層SL上に、金属膜を形成する工程と、(e)上記(d)工程の後、上記金属膜の第1領域をドライエッチングにより除去する工程と、(f)上記(e)工程の後、上記第1領域の上記犠牲層SLをウェットエッチングにより除去する工程と、を有し、上記(c)工程と、上記(f)工程との間に、(g)導電層に熱処理を施し、導電層を結晶化し、導電層CLcとする工程を有する。かかる工程によれば、ドライエッチングにより生じた犠牲層SLのダメージ領域DRを除去できる。

(もっと読む)

微結晶半導体膜及びその作製方法、並びに半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜及びその作製方法を提供する。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】厚さが70nm以上100nm以下の微結晶半導体膜であり、微結晶半導体膜の表面から一部が突出する結晶粒を有し、当該結晶粒は配向面を有し、且つ13nm以上の大きさの結晶子を有する微結晶半導体膜である。また、微結晶半導体膜の膜密度が2.25g/cm3以上2.35g/cm3以下、好ましくは2.30g/cm3以上2.33g/cm3以下である。

(もっと読む)

半導体装置

【課題】酸化物半導体膜を用いたトランジスタに安定した電気特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】n型酸化物半導体膜中にp型酸化物半導体材料を含ませることで酸化物半導体膜中に意図せずに生じるキャリアを低減することができる。これは、n型酸化物半導体膜中の意図せずに生じた電子が、p型酸化物半導体材料中に生じたホールと再結合することにより、消滅するためである。従って、酸化物半導体膜中に意図せずに生じるキャリアを低減することができる。

(もっと読む)

薄膜トランジスタならびに表示装置および電子機器

【課題】多結晶酸化物半導体をチャネルとして用い、キャリアの移動度を保ちつつ、素子特性のばらつきを低減することが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ1は、ボトムゲート型のTFTであり、基板11上に、ゲート電極12、ゲート絶縁膜13、多結晶酸化物半導体を主成分とするチャネル層14およびソース・ドレイン電極15A,15Bをこの順に備えている。チャネル層14の膜厚は、チャネル層を構成する多結晶酸化物半導体の平均結晶粒の直径よりも薄くなるように形成することにより、キャリアの走行方向が制御され素子特性が安定化する。

(もっと読む)

酸化物半導体素子及び半導体装置

【課題】半導体層に結晶性を有する酸化物半導体を用いた、移動度の高い酸化物半導体素子を提供する。

【解決手段】第1の酸化物半導体膜及び、第1の酸化物半導体膜に接して第1の酸化物半導体膜よりバンドギャップが大きい第2の酸化物半導体膜の積層構造を有する層を酸化物半導体層として用いた。これにより、チャネル領域は、第2の酸化物半導体膜と接する第1の酸化物半導体膜の界面近傍(つまり、バンドギャップが小さい酸化物半導体膜の界面近傍)に形成される。また、第1の酸化物半導体膜と第2の酸化物半導体膜の界面は、お互いの未結合手が結合し合っている。このため、第2の酸化物半導体膜と接する第1の酸化物半導体膜の界面近傍に形成されるチャネル領域では、未結合手による電子トラップなどに起因した移動度の低下を低減できる。

(もっと読む)

半導体装置の作製方法

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

薄膜半導体デバイスおよび薄膜半導体デバイスの製法

【課題】安価に、デバイスの効率および長期間安定性が改善された薄膜半導体デバイスを提供する。

【解決手段】薄膜半導体デバイスは、セルロースを含む材料、より具体的には、紙シート材料の基材および基材上の層に蒸着された無機材料の多数の薄膜層を含み、無機材料の多数の薄膜層のうち少なくとも一つは、該基材または基礎をなす無機材料の薄膜層の一方に印刷され、無機材料の多数の薄膜層のうちの少なくとも一つはナノ結晶シリコン粉末を含む活性半導体層およびポリマーを含む担体を含む。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

半導体素子のための緩衝化基板

【課題】製造時間と製造価格を増加することなく多結晶シリコン粒径の微小化と均一化を

行なうための技術を提供する。

【解決手段】基板100上に形成したシリコン層104をレーザビーム106の照射によ

って結晶化して多結晶シリコン層108を得る半導体装置などに用いられ、基板100と

シリコン層104との間にバッファ層102が形成されている。バッファ層102を有す

るこのようなバッファ化基板において、該バッファ層102は、基板100の限界温度よ

りも高い融点を有し、さらに、シリコン層104の結晶化に際し、バッファ層102上に

均一なシリコン結晶粒子を形成するためシリコン層104の核生成密度を規定し、かつシ

リコン層104の結晶化過程における等方粒成長の基礎として機能する。

(もっと読む)

光電変換素子、光電変換回路及び表示装置

【課題】赤外光及び可視光に対する感度の高い光電変換素子を提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆う第1のゲート絶縁層と、第1のゲート絶縁層上の結晶性半導体層と、結晶性半導体層上の非晶質半導体層と、非晶質半導体層上の不純物半導体層と、不純物半導体層に接するソース電極及びドレイン電極と、少なくともソース電極及びドレイン電極の間を覆う第2のゲート絶縁層と、第2のゲート絶縁層上の第2のゲート電極と、を有し、少なくともソース電極とドレイン電極の間に受光部が設けられ、第1のゲート電極は遮光性材料により結晶性半導体層及び非晶質半導体層のすべてと重畳し、第2のゲート電極は透光性材料により受光部と重畳し、第1のゲート電極は、ソース電極またはドレイン電極に電気的に接続されている光電変換素子を提供する。

(もっと読む)

表示装置

【課題】光電変換素子を含む表示装置において、生産性および利便性に優れた表示装置を提供する。

【解決手段】複数の画素がマトリクス状に配列された表示部と、表示部に画像情報を伝送する駆動部と表示部に設けられ、且つレーザ光を検出する受光部と、受光部で検出するレーザ光の位置を解析し、位置に基づいて画像情報を操作し、操作に基づいた画像情報とは異なる画像情報を駆動部に伝送する情報処理部を有し、表示部の複数の画素はそれぞれ薄膜トランジスタを有し、受光部は複数の光電変換素子、走査回路、リセット回路および読み出し回路を有し、薄膜トランジスタおよび複数の光電変換素子は、同一の基板に設けられている表示装置である。

(もっと読む)

エッチング方法及び薄膜トランジスタの作製方法

【課題】アモルファスシリコン膜と微結晶シリコン膜とのエッチングレートの差を大きくしたエッチング方法を提供する。

【解決手段】絶縁膜上に微結晶シリコン膜を形成し、前記微結晶シリコン膜上にアモルファスシリコン膜を形成し、前記アモルファスシリコン膜に1000Paより高圧力のH2とArの混合ガス雰囲気中でプラズマ処理を行うことにより前記微結晶シリコン膜を露出させてエッチングを行う。該エッチングは、アモルファスシリコン膜と微結晶シリコン膜とのエッチングレートの差が大きい。

(もっと読む)

開口部の形成方法及び半導体装置の作製方法

【課題】少なくともフォトマスクの枚数を増加させることなく、積層構造の下部の導電層が露出するように該導電層上の絶縁膜に対する開口部の形成方法を提供する。

【解決手段】開口部が設けられる部分の積層構造の下部の導電層を、該開口部を形成するフォトマスクと同一のフォトマスクを用いて形成されたエッチングマスクにより予め露出させ、その後保護絶縁膜を形成し、前記積層構造の上部の導電層が開口部において露出されないように、保護絶縁膜に開口部を形成する。このような開口部の形成方法は、半導体装置の作製方法に適用することができる。

(もっと読む)

表示装置及びその作製方法

【課題】ドレイン電極(またはソース電極)と画素電極との間の接触抵抗が生じない表示装置を提供する。

【解決手段】ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に設けられた半導体層と、前記半導体層上の一部に接して離間して設けられたソース電極及びドレイン電極と、を有し、前記ソース電極及びドレイン電極の一方は画素電極を兼ねる表示装置とする。前記ソース電極及びドレイン電極の他方は信号線を兼ねる電極であり、該信号線を兼ねる電極上には低抵抗な導電層が設けられていることが好ましい。低抵抗な導電層は、電気メッキ法などにより形成することができる。

(もっと読む)

101 - 120 / 747

[ Back to top ]