Fターム[5F110GG16]の内容

Fターム[5F110GG16]に分類される特許

121 - 140 / 747

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

結晶性半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性半導体の核生成を均一にする。

【解決手段】ガス管から導入された成膜ガスを拡散する第2のガス拡散室と、前記第2のガス拡散室と分散板を隔てて設けられ、該分散板のガス孔から成膜ガスが導入される第1のガス拡散室と、を介して、前記第1のガス拡散室とシャワー板を隔てて設けられた処理室内に該シャワー板のガス孔から成膜ガスを供給し、前記成膜ガスを導入することによって前記処理室内の圧力を2000Pa以上100000Pa以下とし、前記処理室内に電界を生じさせる一対の電極のうち、一方の電極面から電界強度が均一な高周波電力を供給することでグロー放電プラズマを生成させ、前記対向する電極の他方に配された基板上に結晶核を生じさせ、その後、該結晶核を成長させて結晶性半導体膜を作製する。

(もっと読む)

金属酸化物半導体粒子分散組成物

【課題】電気的特性に優れる金属酸化物半導体薄膜を低温でも形成することが可能な金属酸化物半導体粒子分散組成物を提供する。更に、本発明は、該金属酸化物半導体粒子分散組成物を用いた金属酸化物半導体薄膜、透明導電膜及び薄膜トランジスタを提供する。

【解決手段】金属酸化物半導体粒子と分散媒を含有する金属酸化物半導体粒子分散組成物であって、前記金属酸化物半導体粒子は、平均粒子径が1〜50nmであり、かつ、平均粒子径/平均結晶子径が1〜3である金属酸化物半導体粒子分散組成物。

(もっと読む)

半導体装置の作製方法

【課題】半導体層となる部分が水分などに曝されず、マスク枚数を削減する半導体装置の作製方法を提供する。

【解決手段】例えば、第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜及びマスク膜を形成し、マスク膜を加工して第1のマスク層を形成し、第1のマスク層を用いて第1の絶縁膜、半導体膜及び第2の導電膜にドライエッチングを行って薄膜積層体を形成しつつ、第1の導電膜の少なくとも表面を露出させ、薄膜積層体の側面を覆うサイドウォール絶縁層を形成し、第1の導電膜をサイドエッチングして第1の電極層を形成し、第2のマスク層を形成し、第2のマスク層を用いて第2の電極層を形成する。第1のマスク層及び第2のマスク層の形成はレジストマスクを用いて行う。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】電気的特性が良好な半導体装置の作製方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、HBrガスと、CF4ガスと、酸素ガスの混合ガスを含むガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを薄膜トランジスタのバックチャネル部を形成するエッチングに適用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。

(もっと読む)

レーザ照射方法及びレーザ照射装置

【課題】光学調整に困難を伴うことなく、3以上のレーザビームを照射面にて合成し、高出力で生産性を向上させることができるレーザを照射する技術の提供。

【解決手段】その技術は、波長の互いに異なるレーザ発振器とダイクロイックミラー、又はそれに加えて偏光子を用いてレーザビームを合成し、高出力で生産性を向上させレーザを照射するものであり、例えばレーザ発振器から射出されたレーザ光1をダイクロイックミラー1を通過させ、レーザ光1とは波長の異なるレーザ発振器から射出されたレーザ光2をダイクロイックミラー1で反射させてレーザ光を合成し、合成されたレーザ光を照射レーザ光とし、照射レーザ光を照射面上に投影するものである。

(もっと読む)

薄膜素子の作製方法及び半導体装置の作製方法

【課題】所定の層が水分などに一切曝されることない半導体装置の作製方法を提供することを課題とする。

【解決手段】第1の膜、第2の膜及び第3の膜をこの順に積層して形成し、第3の膜上にレジストマスクを形成し、レジストマスクを用いて第3の膜をエッチングすることでマスク層を形成し、レジストマスクを薬液により除去し、マスク層を用いて第2の膜と第1の膜をドライエッチングすることで、第2の層と第1の層を形成し、少なくとも第2の層と第1の層を覆って第4の膜を形成し、第4の膜をエッチバックすることで、少なくとも第1の層の側面のすべてを覆ってサイドウォール層を形成することで薄膜素子を作製する。

(もっと読む)

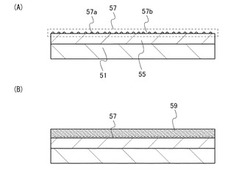

微結晶シリコン膜の作製方法、半導体装置の作製方法

【課題】高い膜密度を保ちつつ結晶性を高くした微結晶シリコン膜の作製方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により混相粒57aを有する第1の微結晶シリコン膜57をプラズマCVD法で形成し、その上に、第2の条件により第2の微結晶シリコン膜59をプラズマCVD法で形成する。第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第1の条件における原料ガスの供給は、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈したガスの供給と、当該ガスの堆積性気体の流量より低く、且つ絶縁膜上へのシリコンの堆積より絶縁膜上に堆積したシリコンのエッチングが優位となる堆積性気体の流量にしたガスの供給を交互に行うものである。

(もっと読む)

半導体装置の作製方法

【課題】マスク数が少なく、工程が簡略な半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜と、半導体膜と、不純物半導体膜と、導電膜と、をこの順に積層して形成し、導電膜を加工してソース電極及びドレイン電極を形成し、不純物半導体膜を離間させつつ半導体膜の上部を加工してソース領域及びドレイン領域と、ソース領域及びドレイン領域と重畳しない部分の上部が除去された半導体層と、を形成し、ゲート絶縁膜、半導体層、ソース領域及びドレイン領域、ソース電極及びドレイン電極上にパッシベーション膜を形成し、パッシベーション膜上にエッチングマスクを形成し、エッチングマスクにより、ソース電極またはドレイン電極に達する開口部を形成しつつ、少なくともパッシベーション膜と半導体層を島状に加工し、エッチングマスクを除去し、ゲート絶縁膜及びパッシベーション膜上に画素電極を形成する。

(もっと読む)

表示装置、及び、その製造方法

【課題】薄膜トランジスタにおいて生じるリーク電流を抑えつつ、表示装置の生産性を向上させることを目的とする。

【解決手段】基板301と、基板301に形成されている複数の薄膜トランジスタTFTと、を有する表示装置であって、薄膜トランジスタTFTは、ゲート電極303と、ゲート電極303の上側に配置される微結晶半導体層305と、微結晶半導体層305上に配置される非晶質半導体層306と、を有し、非晶質半導体層306の水素濃度が、12atom%以下である、ことを特徴とする表示装置。

(もっと読む)

半導体装置

【課題】本発明は、移動度が向上し、コンタクト抵抗が低減された半導体装置を提供する。

【解決手段】基板11上にゲート電極12、ゲート絶縁膜13、ソース・ドレイン電極14および有機半導体15がこの順に積層された半導体装置において、有機半導体層15は、第1の層15aと第1の層15aよりもグレインサイズの小さい第2の層15bとを備えており、第1の層15aがゲート絶縁膜13側に配置されていることを特徴とする半導体装置である。

(もっと読む)

薄膜トランジスタ、表示装置、及び液晶表示装置

【課題】正孔電子対と、ソース電極(ドレイン電極)付近に発生する強電界とがともに抑制されることにより、リーク電流が抑制される薄膜トランジスタ、及びそれを備える表示装置又は液晶表示装置の提供。

【解決手段】光源から光が照射されるゲート電極膜と、前記ゲート電極膜の、前記光源側との反対側に、絶縁膜を介して形成される半導体膜と、前記半導体膜に電気的に接続して形成される第1及び第2の電極膜と、前記ゲート電極膜と同一層に形成されるとともに、前記ゲート電極膜と電気的に遮断される第1の遮光膜と、を備える薄膜トランジスタであって、前記第1の遮光膜は、前記半導体膜の一部と前記光の照射方向から見て重なり合うとともに、前記第1の電極膜の少なくとも一部と、前記光の照射方向から見て重なり合う、ことを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

トランジスタ、発光装置、及び、電子機器

【課題】トランジスタ外部からの光による悪影響を軽減又は防止したトランジスタ、発光装置、及び、電子機器を提供する。

【解決手段】トランジスタTrは、ゲート電極12と、透光性を有する絶縁層を介してゲート電極12と対向配置される、ゲート電極12側の面に光の反射面を有する導電体層22と、ゲート電極12と導電体層22との間に位置し、チャネルが形成される半導体層14と、を備える。光を吸収する光吸収層21は、導電体層22と半導体層14との間、並びにゲート電極12と半導体層14との間の少なくともいずれか一方に位置する。

(もっと読む)

半導体装置及びその駆動方法

【課題】半導体装置における電界の集中を緩和する。

【解決手段】ゲート電極とドレイン電極を重畳させずに設け、且つ上面において、ゲート電極とドレイン電極の間には電界制御電極が設けられている。そして、ゲート電極と半導体層の間、及び電界制御電極と半導体層の間には、それぞれ絶縁層が設けられており、電界制御電極と半導体層の間に設けられた絶縁層は、ゲート電極と半導体層の間に設けられた絶縁層よりも厚い。さらには、この半導体装置を駆動させるに際して、電界制御電極の電位は、ソース電位以上であってゲート電位より低ければよく、例えば、電界制御電極とソース電位を接続させることでこのような構成を実現することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】デュアルゲート型トランジスタのゲートと、ソースまたはドレインの間の寄生容量を低減する。

【解決手段】第1の導電層を覆って設けられた第1の絶縁層と、第1の絶縁層上に設けられた第1の半導体層と、第1の半導体層上に、第1の半導体層を露出させて離間して設けられた第2の半導体層と、第2の半導体層上に設けられた不純物半導体層と、不純物半導体層上に、少なくとも一部が接するように設けられた第2の導電層と、第2の導電層上に設けられた第2の絶縁層と、第1の半導体層、第2の半導体層、不純物半導体層、第2の導電層、及び第2の絶縁層を覆って設けられた第3の絶縁層と、少なくとも、第3の絶縁層上に設けられた第3の導電層と、を有し、第3の導電層は、第1の半導体層の第2の半導体層と重畳していない部分と重畳し、且つ第2の導電層の一部とも重畳している構造とする。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を積層形成する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】結晶性半導体膜に対する非晶質半導体膜のエッチング選択比が高いエッチング方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、Br系ガスと、F系ガスと、酸素ガスの混合ガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを行うことで、露出された部分の膜減りを抑えることができる。更には、当該エッチング方法を薄膜トランジスタのバックチャネル部を形成するエッチングに採用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。該薄膜トランジスタ上には絶縁層が設けられていることが好ましい。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

121 - 140 / 747

[ Back to top ]