Fターム[5F110GG16]の内容

Fターム[5F110GG16]に分類される特許

61 - 80 / 747

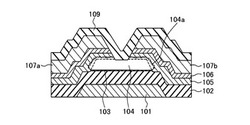

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

電子デバイス

【課題】薄膜トランジスタおよび/または電子デバイスの電荷キャリア移動度を増大させ、高い移動度および優れた安定性を達成する。

【解決手段】薄膜トランジスタの半導体層は、半導体組成物として、ポリマー結合剤および小分子半導体を含む。また、半導体層は、ソース電極およびドレイン電極の間の方向に配列したアライメント層上に堆積されている。アライメント層は、電子デバイスの電界効果移動度を増大させるために使用される。

(もっと読む)

半導体装置

【課題】動作特性および信頼性の向上した、新規なマルチゲート構造のトランジスタを提

供することを課題とする。

【解決手段】2つ以上のゲート電極と、直列に接続した2つ以上のチャネル形成領域、ソ

ース領域、ドレイン領域、及び高濃度不純物領域を有する半導体層と、を有するマルチゲ

ート構造のトランジスタにおいて、ソース領域側に近接するチャネル形成領域のチャネル

長が、ドレイン領域側に近接するチャネル形成領域のチャネル長よりも大きくする。

(もっと読む)

半導体装置

【課題】占有面積が小さく、冗長性があり、かつリーク電流の小さい保護回路を提供する。

【解決手段】保護回路は、複数の非線形素子が重畳するように積層され、かつ該非線形素子が電気的に直列接続されている構成であり、該保護回路に含まれる少なくとも一つの非線形素子は、チャネル形成領域に酸化物半導体を用いたトランジスタをダイオード接続した素子であり、他の非線形素子は、チャネル形成領域にシリコンを用いたトランジスタをダイオード接続した素子、または、接合領域にシリコンを用いたダイオードとする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

半導体装置

【課題】電源をオフしてもデータを保持することができ、退避動作と復帰動作が不要なレジスタ回路を提供する。

【解決手段】複数のレジスタ構成回路と、オフ電流が小さい第1のトランジスタと、オフ電流が小さい第2のトランジスタと、を有するレジスタ回路において、データ保持部を前記第1のトランジスタのソース及びドレインの一方に接続し、前記第2のトランジスタのソース及びドレインの一方に接続する。前記第1のトランジスタ及び前記第2のトランジスタはオフ電流が小さいので、データ保持部の電荷がリークせず、レジスタ回路の電源をオフしてもデータ保持部にデータが保持される。そのため、退避動作と復帰動作を行わなくてよい。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

半導体装置

【課題】不揮発性メモリを提供する。

【解決手段】一般的なSRAMと同様の回路構成を有し、該SRAMの記憶保持部と電源電位線の間にオフ電流の小さいトランジスタを配することで、記憶保持部からの電荷の漏れが防止された半導体装置(不揮発性メモリ)とする。ここで、記憶保持部からの電荷の漏れを防止するためのオフ電流の小さいトランジスタとしては、酸化物半導体膜により設けられたトランジスタを用いることが好ましい。このような構成はシフトレジスタにも適用することができ、消費電力の小さいシフトレジスタを得ることができる。

(もっと読む)

半導体装置

【課題】処理実行中に電源をオフしてもデータが保持され、且つ従来よりも占有面積が小さいDフリップフロップ回路を有する半導体装置を提供する。

【解決手段】入力端子が、第1のトランスミッションゲートの第1の端子に電気的に接続され、第1のトランスミッションゲートの第2の端子が、第1のインバータの第1の端子及び機能回路の第2の端子に電気的に接続され、第1のインバータの第2の端子及び機能回路の第1の端子が、第2のトランスミッションゲートの第1の端子に電気的に接続され、第2のトランスミッションゲートの第2の端子が第2のインバータの第1の端子及びクロックドインバータの第2の端子に電気的に接続され、第2のインバータの第2の端子及びクロックドインバータの第1の端子は出力端子に電気的に接続されており、機能回路にはオフ電流が小さいトランジスタと容量素子との間にデータ保持部を有する半導体装置とする。

(もっと読む)

酸化物半導体層

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供す

ることを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導

体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードであ

る。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれ

る電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度

化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導

体よりもバンドギャップが大きい。

(もっと読む)

酸化物半導体薄膜層を有する積層構造及び薄膜トランジスタ

【課題】酸化物薄膜の結晶配置の方向を制御し、良質な酸化物薄膜を提供する。

【解決手段】酸化物層と絶縁層からなる積層構造であって、前記酸化物層のキャリア濃度が1018/cm3以下、平均結晶粒径が1μm以上であり、前記酸化物層の結晶が、前記絶縁層の表面に柱状に配置していることを特徴とする積層構造。

(もっと読む)

半導体装置

【課題】周辺の回路構成を複雑にすることなく、繰り返しのデータの書き込みの際の劣化を低減することが可能な、不揮発性スイッチとして用いる半導体装置を提供する。

【解決手段】電源電圧が停止しても導通状態に関するデータの保持を、チャネル形成領域に酸化物半導体層を有する薄膜トランジスタに接続されたデータ保持部で行う構成とする。そしてデータ保持部は、ダーリントン接続された電界効果トランジスタ及びバイポーラトランジスタを有する電流増幅回路における、電界効果トランジスタのゲートに接続することでデータ保持部の電荷をリークすることなく、導通状態を制御する。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置をより少ない工程で作製する。

【解決手段】トランジスタと、画素電極とを有し、トランジスタは、第1のゲート電極と、第1のゲート電極上の第1の絶縁層と、第1の絶縁層上の半導体層と、半導体層上の第2の絶縁層と、第2の絶縁層上の第2のゲート電極とを有し、第1のゲート電極は、第1の絶縁層を介して、半導体層と重なる領域を有し、第2のゲート電極は、第2の絶縁層を介して、半導体層と重なる領域を有し、画素電極は、第2の絶縁層上に設けられ、第1の領域は、第2のゲート電極の少なくとも一部が、半導体層の少なくとも一部と重なる領域のうちの、少なくとも一部の領域であり、第2の領域は、画素電極が設けられた領域のうちの、少なくとも一部の領域であり、第1の領域における第2の絶縁層は、第2の領域における第2の絶縁層よりも薄い。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、特性の改善された酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを課題の一つとする。

【解決手段】絶縁表面を有する基板上にゲート電極層を形成し、ゲート電極層上にゲート絶縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層上にソース電極層及びドレイン電極層を形成し、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸素を含む絶縁層を形成し、酸素を含む絶縁層上に水素を含む絶縁層を形成した後、熱処理を行うことにより、水素を含む絶縁層中の水素を少なくとも酸化物半導体層に供給することを特徴とする半導体装置の作製方法である。

(もっと読む)

61 - 80 / 747

[ Back to top ]