Fターム[5F110GG30]の内容

Fターム[5F110GG30]に分類される特許

21 - 40 / 331

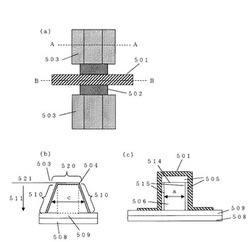

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

マルチゲート電界効果トランジスタのゲート電極およびその製造方法

【課題】マルチゲート電界効果トランジスタにおいて、新規なゲート電極構造と製造方法を提供する。

【解決手段】マルチゲート電界効果トランジスタ102のゲート電極100は、半導体基板104と、前記半導体基板上の誘電体層106と、前記誘電体層上のフィン108と、前記フィンの側面上のゲート絶縁膜であって、前記フィンの側面上に形成されるゲート絶縁膜と接する誘電体層の上面部分を除き、前記誘電体層の上面上には形成されないゲート絶縁膜110と、フィン上のゲート電極層112と、前記フィンを覆うように形成されるポリシリコン層114とを具備する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

半導体装置

【課題】良好な電気特性を有する半導体装置を提供する。

【解決手段】基板上に形成される第1の電極と、第1の電極に接して形成される一対の酸化物半導体膜と、一対の酸化物半導体膜に接する第2の電極と、少なくとも第1の電極および一対の酸化物半導体膜を覆うゲート絶縁膜と、ゲート絶縁膜に接して、少なくとも一対の酸化物半導体膜の間に形成される第3の電極とを有する半導体装置であり、酸化物半導体膜のドナー密度が1.0×1013/cm3以下である場合、酸化物半導体膜の膜厚は、酸化物半導体膜の膜厚横方向の長さに対して厚くすることである。

(もっと読む)

半導体装置、並びに、半導体装置の製造方法及び駆動方法

【課題】絶縁層上に形成された部分空乏型のトランジスターにおいて、ヒストリー効果を低減し、なおかつ高いON/OFF比、及び急峻なサブスレッショルド特性を実現する。

【解決手段】絶縁層上の半導体層に形成された第1導電型のソース領域、第1導電型のドレイン領域、及び、第2導電型のボディ領域と、第1ゲート絶縁膜と、第1ゲート電極と、を含む部分空乏型の第1トランジスターと、絶縁層上の半導体層に形成された第1ダイオードと、を具備し、第1ダイオードは、第1導電型の第1不純物領域と、第1不純物領域上に形成された第2導電型の第2不純物領域と、を含み、第1トランジスターのボディ領域は、第1ダイオードの第1不純物領域及び第2不純物領域に接続されている。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

半導体装置

【課題】生産性の高い半導体材料を用い、且つ耐圧性を向上させたトランジスタを提供することを課題の一とする。または、高耐圧のトランジスタを用いた大電力向けの半導体装置を提供することを課題の一とする。

【解決手段】トランジスタにおいて、高電界の印加されるドレイン電極を平坦な面上に形成し、且つ、ゲート電極の、チャネル幅方向のドレイン電極側の端部、およびチャネル長方向の端部を、ゲート絶縁層を介して酸化物半導体層で覆うことによって、トランジスタの耐圧を向上させる。また、該トランジスタを用いた大電力向けの半導体装置を提供することができる。

(もっと読む)

面エピ形状とソース/ドレインの部分的に覆われるシリサイド周辺とに関するフィンフェット

【課題】低い寄生抵抗(例えば、Rpara)および/または高い駆動電流の改善された特性を有するフィンフェットを提供する。

【解決手段】フィンフェット100およびフィンフェットの製造方法が提供される。フィンフェットは、半導体基板106上に、2つまたは複数のフィン102,104と、前記フィンの側面に設けられるエピタキシャル層108,110と、前記エピタキシャル層の表面上を覆うように設けられる金属−半導体化合物112,114とを備える。フィンは、前記半導体基板の表面上に対して実質的に垂直な側面を有する。前記エピタキシャル層は、前記フィンの側面に対して斜角を有して延設される表面を有する。フィンフェットは、前記金属−半導体化合物上に設けられるコンタクト116を含み得る。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を低減し、特性ばらつきが抑制された多結晶半導体層をチャネル領域とする半導体装置の製造方法を提供する。

【解決手段】半導体基板の上に絶縁体層を形成する工程と、絶縁体層上に狭窄部を有する非晶質または多結晶質の半導体層を形成する工程と、半導体層上に半導体層よりも熱膨張係数の大きい絶縁体層を形成する工程と、熱処理を行う工程と、絶縁体層を除去する工程と、狭窄部の側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体層中にソース・ドレイン領域を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及び発光装置並びに電子機器

【課題】ソース、ドレイン電極のアライメントずれに起因する薄膜トランジスタのオン電流のばらつきを抑制することができる半導体装置を提供する。また、良好な表示画質を有するとともに、製品の歩留まりを向上させることができる発光装置、並びに、該発光装置を実装した電子機器を提供する。

【解決手段】トランジスタTFTは、基板11上に隣接して設定されたトランジスタ形成領域Rta、Rtbの各々に、単一のゲート電極Trgを兼用した薄膜トランジスタTrA、TrBが設けられている。また、薄膜トランジスタTrAのソース電極Trasと薄膜トランジスタTrBのソース電極Trbsが接続配線LNsを介して接続され、薄膜トランジスタTrAのドレイン電極Tradと薄膜トランジスタTrBのドレイン電極Trbdは、接続配線LNdを介して接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明の半導体装置は、良好なカットオフ特性と高速動作とを両立して改善できる。

【解決手段】 本発明の半導体装置は、基板と、基板上に形成され、バンドギャップが生成されたグラフェンを有するチャネル領域と、チャネル領域の両側に形成され、チャネル領域のグラフェンに比して小さいバンドギャップが生成されたグラフェンを有するソース/ドレイン領域と、ソース/ドレイン領域のチャネルに接する部分の上に、夫々形成された第1および第2のゲート電極と、を備えることを特徴とする。

(もっと読む)

電界効果トランジスタ(FET)およびそれを形成する方法

Uゲートトランジスタ製造方法

【課題】短チャネル性能を改善した非プレーナ半導体トランジスタ構造及びその製造方法を提供する。

【解決手段】基板360上にある絶縁層301上にU字形フィン305が形成され、その一部の上にゲート誘電体層362及びゲート電極363が形成され、ソース領域403及びドレイン領域404が、U字形フィン305の両側に形成される。ゲート電極363は、ゲート誘電体層362とともに、U字形フィン305の一部の上側表面306及び反対の位置にある2つの側壁307、並びにU字形フィン305の中にある凹部319の一部の底面320及び向かい合って位置する2つの側壁364を覆い、電流を流すチャネル領域の幅を実効的に増やす。U字形トランジスタ構造の電流−電圧特性は、ゲート電圧範囲全体にわたって、デバイスの角部分の性能によって支配され、短チャネル効果が最小限に抑えられ、閾値下の電流及び駆動電流が最適化される。

(もっと読む)

Uゲートトランジスタ製造方法

【課題】MOSトランジスタを小型化する場合に主な制約要因となる短チャネル効果を抑制できるUゲートトランジスタを提供する。

【解決手段】非プレーナ多角トランジスタ構造を製造するための工程が以下のように構成される。フィンの上側表面上にマスクを有する半導体材料のフィンが、第1の絶縁層上に形成される。マスクの上側表面を露出させたまま、フィン上に第2の絶縁層が形成され、フィンと第2の絶縁層との間に保護層が堆積される。次に、マスクが除去され、保護層に隣接するフィン内にスペーサが形成される。フィン内に、底面及び向かい合っている側壁を有する凹部が形成される。フィン305の上側表面及び反対の位置にある側壁上、並びにフィン内の凹部の底面及び向かい合っている側壁上に、ゲート誘電体層362及びゲート電極363が形成される。ゲート電極363の両側においてフィン内にソース領域403及びドレイン領域404が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の特性が得られるフィン型半導体領域を有する半導体装置を実現する。

【解決手段】上面及び側面を有する第1の半導体領域61の上部に第1導電型の第1の不純物領域61aが形成されていると共に、第1の半導体領域61の側部に第1導電型の第2の不純物領域61bが形成されている。第1の半導体領域61の所定の部分における少なくとも側面及び上部コーナーを覆うようにゲート絶縁膜62が形成されている。ゲート絶縁膜62の外側に位置する部分の第1の半導体領域61における上部コーナーの曲率半径r’は、ゲート絶縁膜62の下側に位置する部分の第1の半導体領域61における上部コーナーの曲率半径rよりも大きく且つ2r以下である。

(もっと読む)

半導体装置およびその製造方法

本発明の方法(20)は、端部の第1の組を有する分離された要素を含むパターンで導電材料層を基板上に提供する段階(21)を含む、半導体装置の製造に関する。本方法は、段階(22)において、基板上にそれらの間に一つ以上のキャビティを形成するための一連の壁構造体を提供する段階をさらに含む。壁構造体は端部の第1の組と協働する端部の第2の組を有する。端部の第2の組は所定の距離で端部の第1の組から後退する。さらに、本方法は段階(24)において、キャビティ内に液体材料を堆積する段階を含む。上述の特徴を有するディスプレイおよび電子装置も開示される。  (もっと読む)

(もっと読む)

マルチゲートIII−V量子井戸構造

マイクロ電子構造を形成する方法を記載する。方法の実施形態は、基板上にIII−Vトライゲートフィンを形成する段階と、III−Vトライゲートフィンの周囲にクラッド材を形成する段階と、クラッド材の周りに高誘電率ゲート誘電体を形成する段階とを備える。 (もっと読む)

半導体装置及びその製造方法

【課題】フィン型半導体領域の側面にN型不純物を導入して低抵抗の不純物領域を形成できるようにし、それによって、所望の特性を持つN型のフィン型半導体装置を実現する。

【解決手段】基板11上にフィン型半導体領域13を形成した後、フィン型半導体領域13の少なくとも側部にN型不純物をプラズマドーピングによって導入することにより、フィン型半導体領域13の側部にN型不純物領域27bを形成する。プラズマドーピング時のソースパワーをY[W]としたときに、N型不純物を含むガスの単位時間・単位体積当たりの供給量を5.1×10-8/((1.72.51/24.51)×(Y/500))[mol/(min・L・秒)]以上に設定すると共に、希釈ガスの単位時間・単位体積当たりの供給量を1.7×10-4/((202.51/24.51)×(Y/500))[mol/(min・L・秒)]以上に設定する。

(もっと読む)

半導体装置

【課題】良質な半導体装置を提供することを目的としている。

【解決手段】素子分離領域間の凸部108を含むシリコン基板106と、凸部108上の絶縁部112と、絶縁部112上のシリコンフィン114と、上面が凸部108の上面よりも低く位置する素子分離領域内の素子分離層116と、シリコンフィン114に設けられたソース/ドレイン領域と、ソース/ドレイン領域104のシリコンフィン114の側面から外側に突き出た横方向エピ成長シリコン部118と、ゲート電極領域102内のゲート絶縁層122を介してシリコンフィン114上に設けられるゲート電極124と、ゲート電極124の側面に隣接する第1のスペーサ128と、ソース/ドレイン領域104内の凸部108の側面を覆う第2のスペーサ130とを備える。

(もっと読む)

21 - 40 / 331

[ Back to top ]