Fターム[5F110GG30]の内容

Fターム[5F110GG30]に分類される特許

61 - 80 / 331

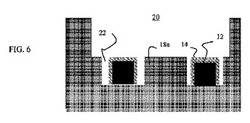

置換ゲート構造体を有するFET及びその製造方法

【課題】 マルチゲート型FETの置換ゲート構造体及びマルチゲート型FETの置換ゲート構造体の製造方法を提供する。

【解決手段】 MUGFET及びMUGFETを製造する方法が示される。MUGFETを製造する方法は、複数の活性領域の周りに一時的スペーサ・ゲート(図3の16)を形成することと、複数の活性領域の間を含む、一時的スペーサ・ゲートの上に誘電体材料(18a及び空間20内)を堆積させることとを含む。この方法は、誘電体材料(空間20内)の部分をエッチングして一時的スペーサ・ゲート(16)を露出させることと、一時的スペーサ・ゲートを除去して、活性領域と誘電体材料の残りの部分(18a)との間に空間を残すこととをさらに含む。この方法はさらに、活性領域と誘電体材料の残りの部分(18a)との間の空間(22)及び誘電体材料の残りの部分の上方をゲート材料で充填することを含む。

(もっと読む)

シフトレジスタ回路、シフトレジスタ回路の設計方法及び半導体装置

【課題】オーバーラップ容量を小さくすることが可能なトランジスタを提供し、電源電圧マージン低下を防止したシフトレジスタ回路を得る。

【解決手段】第2電源端子S2,ノードN1間に介挿されるNMOSトランジスタQ3を4つのNMOSトランジスタQ3a〜Q3dによる並列接続で構成し、トランジスタ端部のドレイン電極(NMOSトランジスタQ3a,Q3dのドレイン電極3)以外のソース・ドレイン電極(NMOSトランジスタQ3a〜Q3dのソース電極4、及びNMOSトランジスタQ3b,Q3cのドレイン電極3)を、ゲート電極1上に形成されたa−Si半導体領域2上に確実に形成可能にする。そして、ノードN1に接続されたソース電極4の形成幅Lをトランジスタ端部の領域Bでのゲート・ソース電極重なり幅a1及びa2の和よりも小さくしている。

(もっと読む)

電界効果トランジスタ(FET)インバータとその製造方法(単一ゲート・インバータのナノワイヤ・メッシュ)

【課題】単一ゲート・インバータのナノワイヤ・メッシュ及びその製造方法を提供する。

【解決手段】電界効果トランジスタ(FET)インバータは、スタック内で垂直方向に配置された複数のデバイス層を含み、各デバイス層は、ソース領域、ドレイン領域、及びソース領域とドレイン領域を接続する複数のナノワイヤ・チャネル110を有し、ここで1つ又は複数のデバイス層のソース及びドレイン領域はn型ドーパント、又はp型ドーパントでドープされる。FETインバータはさらに、複数のナノワイヤ・チャネルを取り囲む共通のゲート150と、n型ドーパントでドープされた1つ又は複数のデバイス層のソース領域への第1のコンタクト156と、p型ドーパントでドープされた1つ又は複数のデバイス層のソース領域への第2のコンタクト158と、デバイス層の各々のドレイン領域への共通の第3のコンタクト152とを含む。

(もっと読む)

半導体装置の作製方法

【課題】nチャネル型トランジスタ及びpチャネル型トランジスタを有する半導体装置の集積化を図ることを目的の一とする。または、半導体装置の性能向上を図ることを目的の一とする。または、大面積な半導体装置を低コストに提供することを目的の一とする。

【解決手段】{211}面から±15°以内の面を表面とする単結晶シリコン基板に加速されたイオンを照射して、単結晶シリコン基板中に脆化領域を形成する工程と、絶縁層を介して単結晶シリコン基板とベース基板とを貼り合わせる工程と、脆化領域において、単結晶シリコン基板を分離し、ベース基板上に{211}面から±15°以内の面を表面とする単結晶シリコン層を形成する工程と、単結晶シリコン層を用いて、チャネル長方向が<111>軸から±15°以内のnチャネル型トランジスタ及びpチャネル型トランジスタを形成する工程と、を有する半導体装置の作製方法である。

(もっと読む)

複数の閾値電圧を有するナノワイヤ・メッシュFET及びその製造方法

【課題】 調整可能な複数の閾値電圧(Vt)を有する、ナノワイヤ・ベースのFET、及びこれを製造する方法を提供する。

【解決手段】 ナノワイヤ・ベースの電界効果トランジスタ(FET)及びその製造のための技術が提供される。一態様において、各々がソース領域、ドレイン領域、及びソース領域とドレイン領域を接続する複数のナノワイヤ・チャネルを有する、スタック状に垂直方向に配向された複数のデバイス層であって、デバイス層の1つ又は複数は、デバイス層の他の1つ又は複数とは異なる閾値電圧を有するように構成される、複数のデバイス層と、ナノワイヤ・チャネルを取り囲むデバイス層の各々に共通のゲートとを有するFETが提供される。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

半導体装置

【課題】FD型トランジスタで構成された電気回路において、電気回路に電力を供給する電源のスイッチングトランジスタを基板電圧で制御することができる半導体装置を提供する。

【解決手段】半導体装置は、基板上の第1のFinに形成された第1のトランジスタを含む電気回路と、半導体基板上の第2のFinに形成され、電気回路と電源供給線との間に接続された第2のトランジスタを含む電源回路と、基板に基板電圧を印加するための基板コンタクトとを備え、第1のFinの幅は、第1のトランジスタのチャネル部に形成される最大空乏層幅の2倍以下であり、第2のFinの幅は、第2のトランジスタのチャネル部に形成される最大空乏層幅の2倍よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス工程数を増加させることなく、レイアウト面積が小さく且つ駆動能力が高いMulti−Fin型トランジスタを実現できるようにする。

【解決手段】半導体装置は、シリコンからなる基板100の上に形成され、それぞれ互いに間隔をおき且つ並列に配置された直方体状の複数のソース拡散層110及び複数のドレイン拡散層111(Fin部)と、複数のFin部の上に、各Fin部と交差すると共にそれぞれゲート絶縁膜105を介在させて形成されたゲート電極106とを有している。複数のFin部における少なくとも一方の端部には、少なくとも2つのFin部と電気的に接続されたソース拡散層部コンタクトプラグ120が形成されている。

(もっと読む)

電気光学装置及びその製造方法

【課題】例えば、液晶装置等の電気光学装置の製造に要するコスト削減と、表示性能の向上とを同時に実現する。

【解決手段】TFT(30)は、TFTアレイ基板(10)上において下側容量電極(80a)及び(80b)と同層に形成された半導体層(30a)と、その上に形成されたゲート絶縁膜(30b)と、ゲート電極(30c)とを備えて構成されている。半導体層(30a)は、TFTアレイ基板(10)の厚み方向に沿った厚みよりTFTアレイ基板(10)の基板面に沿った幅が大きくなるように形成されている。したがって、TFT(30)及び保持容量(70)によれば、液晶装置(1)の製造時に、ポリシリコン等の半導体からなる下側容量電極(80a)及び(80b)と共通の工程によってTFT(30)を形成可能であり、液晶装置(1)の製造プロセスを簡略化でき、且つ製造コストの低減できる。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうる単結晶半導体層を備えた半導体基板の製造方法を提供する。

【解決手段】単結晶半導体基板上に酸化膜を形成し、酸化膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板中に脆化領域を形成し、酸化膜を間に挟んで単結晶半導体基板と向かい合うように支持基板を貼り合わせ、単結晶半導体基板を加熱することにより、脆化領域において、単結晶半導体層が貼り合わされた支持基板と単結晶半導体基板の一部とに分離し、支持基板に貼り合わされた単結晶半導体層の表面に対して、基板バイアスを印加して第1のエッチングを行い、単結晶半導体層に対してレーザビームを照射して、単結晶半導体層の少なくとも表面の一部を溶融した後、凝固させ、単結晶半導体層の表面に対して、基板バイアスを印加することなく第2のエッチングを行う。

(もっと読む)

半導体装置、その製造方法及びプラズマドーピングシステム

【課題】フィン型半導体領域を有する半導体装置においてプラズマドーピング法を用いて短時間で所望の特性が得られるようにする。

【解決手段】基板11上にフィン型半導体領域13が形成されている。フィン型半導体領域13の上部及び側部には、半導体にドナー準位又はアクセプタ準位を生成する第1の不純物が導入されていると共に、フィン型半導体領域13の上部には、半導体を絶縁物化する第2の不純物がさらに導入されている。

(もっと読む)

ナノワイヤ・メッシュ・デバイス及びその製造方法

【課題】 デバイスの電流密度を増大させながら、デバイスの接触スキーム及びスケーラビリティを改善する、ナノワイヤFET構造体及びその製造方法を提供する。

【解決手段】 基板の表面上に配置された、垂直方向に積層され垂直方向に離間配置された複数の半導体ナノワイヤ(例えば、半導体ナノワイヤ・メッシュ)を含む半導体構造体が提供される。垂直方向に積層され垂直方向に離間配置された各々の半導体ナノワイヤの一方の端部セグメントは、ソース領域に接続され、垂直方向に積層され垂直方向に離間配置された各々の半導体ナノワイヤの他方の端部セグメントは、ドレイン領域に接続される。ゲート誘電体及びゲート導体を含むゲート領域は、垂直方向に積層され垂直方向に離間配置された複数の半導体ナノワイヤに当接し、ソース領域及びドレイン領域は、ゲート領域と自己整合される。

(もっと読む)

半導体装置およびその製造方法

【課題】NMISFETにおいて、最も高移動度化可能である(111)面をチャネル面に持ち、同時に、<110>方向を電流方向に持つ半導体装置およびその製造方法を提供すること。

【解決手段】チャネル電流が流れる方向に対して垂直方向の断面が三角形状をしており、その2面が(111)面で、残りの1面が(100)面であるGOI層6またはGe層8と、前記(100)面上に形成されたSi層7と、を備えたNMISFET領域3を備えたこと、を特徴とする半導体装置1。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】優れた電気伝導特性を安定して示すカーボンナノチューブ電界効果トランジスタを再現性よく製造することができる方法を提供すること。

【解決手段】まず、LOCOS法によりシリコン基板のコンタクト領域に酸化シリコン膜を形成する。次いで、シリコン基板のチャネル領域に、コンタクト領域の酸化シリコン膜よりも薄い絶縁膜を形成する。次いで、シリコン基板上にチャネルとなるカーボンナノチューブを配置した後、カーボンナノチューブを保護膜で被覆する。最後に、ソース電極およびドレイン電極をそれぞれ形成して、ソース電極およびドレイン電極をそれぞれカーボンナノチューブに電気的に接続させる。このようにして製造された電界効果トランジスタは、チャネルとなるカーボンナノチューブが汚染されていないため、優れた電気伝導特性を安定して示す。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】

新規なフィン形電界効果トランジスタの製造方法を提供する。

【解決手段】

支持基板上方に頂部水平面と垂直側面を有し、第1の方向に延在するフィン型シリコン領域を形成し、フィン型シリコン領域上に、第1の方向とは異なる第2の方向に延在するダミーゲート電極を形成し、ダミーゲート電極、フィン型シリコン領域を埋め込む第1の絶縁膜を形成し、ダミーゲート電極が露出するまで第1の絶縁膜を研磨し、ダミーゲート電極の頂部と垂直部の少なくとも一部とを除去してフィン型シリコン領域表面を露出するトレンチを形成し、トレンチ内でフィン型シリコン領域表面上にゲート電極構造を形成する。

(もっと読む)

半導体構造体および半導体構造体を形成する方法

【課題】セミコンダクタ・オン・インシュレータ(SOI)基板上に形成されたボディ接触ハイブリッド・サーフェス・セミコンダクタ・オン・インシュレータ(HSSOI)デバイスおよびこれを製造する方法を提供する。

【解決手段】SOI基板の最上部半導体層の一部分にパターン形成して、実質的に垂直な側壁を有する半導体フィン18が作成される。半導体フィンのボディ領域20とは反対の導電型のドーピングを有する2つのソース領域62間の半導体フィンの上面で半導体フィンのボディ領域の一部分が露出される。2つのソース領域と、2つのソース領域間の露出されたボディ領域の上面のすぐ上に、金属半導体合金部分82が形成される。ボディ領域への低抵抗接触を可能にするために、イオン注入によってボディ領域の露出された最上部部分のドーピング濃度を高めることができるか、または高密度の結晶欠陥を有する再結合領域を形成することができる。

(もっと読む)

カーボンナノチューブの製造装置及びカーボンナノチューブを分別する方法

【課題】カーボンナノチューブを特性毎に分別する。

【解決手段】本発明の例に関わるカーボンナノチューブの分別装置は、第1の磁気特性を有する第1のカーボンナノチューブSCNTと第2の磁気特性を有する第2のカーボンナノチューブMCNTとが共通に導入される導入部2と、第1及び第2のカーボンナノチューブSCNT,MCNTをそれぞれ回収する第1及び第2の回収部4A,4Bと、第1及び第2のカーボンナノチューブSCNT,MCNTを導入部2から回収部4A,4Bまで搬送する搬送部3と、搬送部3に隣接して配置され、カーボンナノチューブSCNT,MCNTに対して磁場Hを印加する磁場発生部5とを具備し、第1の磁気特性と磁場Hとの相互作用によって、第1のカーボンナノチューブSCNTと第2のカーボンナノチューブMCNTとを分別する。

(もっと読む)

相補型半導体装置とその製造方法

【課題】 マルチゲートMISFETからなる高移動度のnFET及びpFETの双方の移動度を向上させる相補型半導体装置とその製造方法を提供する。

【解決手段】

基板10上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された相補型半導体装置であって、nチャネルMISトランジスタ及びpチャネルMISトランジスタが、基板10の主面に平行な面内に引っ張り歪みを有する第一の半導体層と圧縮歪みを有する第二の半導体層とが交互に積層され、基板10の主面に対して突出した積層構造と、積層構造の対向する両側面を覆うように形成されたゲート絶縁膜80と、ゲート絶縁膜80を介して前記積層構造を覆って形成されたゲート電極30と、ゲート絶縁膜80とゲート電極30をはさんで対向し、積層構造の両端に形成されたソース/ドレイン領域20と、を有することを特徴とする相補型半導体装置。

(もっと読む)

SOI基板の作製方法

【課題】単結晶半導体層にレーザー光を照射する場合において、レーザー光の照射時に単結晶半導体層中に不純物元素が取り込まれるのを抑制することを目的の一とする。

【解決手段】SOI基板の作製方法において、単結晶半導体基板と、ベース基板とを用意し、単結晶半導体基板に加速されたイオンを照射することにより、単結晶半導体基板の表面から所定の深さの領域に脆化領域を形成し、単結晶半導体基板とベース基板とを絶縁層を介して貼り合わせ、単結晶半導体基板を加熱し、脆化領域を境として分離することにより、ベース基板上に絶縁層を介して単結晶半導体層を形成し、単結晶半導体層上に形成された酸化膜を除去し、酸化膜を除去した後に単結晶半導体層の表面にレーザー光を照射して単結晶半導体層の少なくとも表面を溶融させ、レーザー光の照射による単結晶半導体層の溶融回数は1回とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられる金属半導体化合物電極の界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板と、半導体基板上に形成され、Sを1×1020atoms/cm3以上含有する界面層と、界面層上に形成され、略全域にSを1×1020atoms/cm3以上含有する金属半導体化合物層と、金属半導体化合物層上の金属電極を有することを特徴とする半導体装置。半導体基板上に金属膜を堆積し、第1の熱処理により、金属膜を半導体基板と反応させて、金属半導体化合物層を形成し、金属半導体化合物層に、飛程が金属半導体化合物層の膜厚未満となる条件でSをイオン注入し、第2の熱処理により、Sを再配置することを特徴とする半導体装置の製造方法。

(もっと読む)

61 - 80 / 331

[ Back to top ]