Fターム[5F110GG44]の内容

Fターム[5F110GG44]の下位に属するFターム

Fターム[5F110GG44]に分類される特許

101 - 120 / 1,993

有機半導体素子の製造方法および有機半導体素子

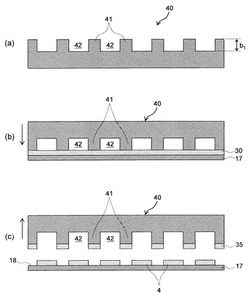

【課題】良好な特性を有する複数の有機トランジスタを備えた有機半導体素子の製造方法を提供する。

【解決手段】有機半導体素子10は、基板11と、基板11上に設けられ、各々が液晶性有機半導体材料を含む有機半導体領域4を有する複数の有機トランジスタ20と、を備えている。このうち有機半導体領域4は、少なくとも基板11を含む支持部材17によって支持されている。そして、有機半導体素子10の製造方法は、支持部材17を準備する工程と、支持部材17上に液晶性有機半導体材料を含む連続的な有機半導体層30を設ける工程と、有機半導体層30をパターニングして複数の有機半導体領域4を形成するパターニング工程と、を備えている。ここで、パターニング工程は、凹部42および凸部41を有する凹凸版40を準備する工程と、凹凸版40の凸部41を支持部材17上の有機半導体層30に当接させることにより有機半導体層30をパターニングする当接工程と、を有している。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインが、第1半導体結晶層を構成する原子とニッケル原子との化合物、第1半導体結晶層を構成する原子とコバルト原子との化合物または第1半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、第2半導体結晶層を構成する原子とニッケル原子との化合物、第2半導体結晶層を構成する原子とコバルト原子との化合物、または、第2半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜上に金属元素を含む絶縁膜を形成し、注入法により該金属元素を含む絶縁膜を通過して導入されたドーパントを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

放射線撮像装置、放射線撮像表示システムおよびトランジスタ

【課題】放射線に起因する特性劣化を抑制して信頼性を向上させることが可能なトランジスタを提供する。

【解決手段】放射線撮像装置は、フォトダイオードとトランジスタとを含む画素回路を有する。トランジスタは、基板上の選択的な領域に配設されたゲート電極と、ゲート電極上に第2ゲート絶縁膜を介して設けられた半導体層と、半導体層上に第1ゲート絶縁膜を介して設けられると共にゲート電極に対向するゲート電極と、ゲート電極上に設けられた第1層間絶縁膜と、半導体層に電気的に接続されて設けられたソース電極およびドレイン電極と、一部がゲート電極の端部に対向して設けられたシールド電極層とを備える。第2ゲート絶縁膜、第1ゲート絶縁膜および第1層間絶縁膜のうちの少なくとも1つはシリコン酸化膜を含む。シールド電極層により、放射線の入射によって生じる正電荷の影響による閾値電圧のシフトが抑制される。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタ及びその作製方法を提供する。または、該トランジスタを含む信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】チャネル形成領域と、該チャネル形成領域を挟むように設けられ、チャネル形成領域よりも低抵抗な領域であるソース領域及びドレイン領域と、を含み、チャネル形成領域、ソース領域及びドレイン領域はそれぞれ結晶性領域を含む酸化物半導体層を有する半導体装置を提供する。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜に、金属元素を含む膜と接した状態で加熱処理することにより導入された金属元素と、注入法により該金属元素を含む膜を通過して導入されたドーパントとを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

電子デバイス及び半導体装置の製造方法

【課題】簡素な装置で、短時間にて形成することができ、しかも、電極と能動層との間のコンタクト抵抗の低減を確実に図ることができる電荷注入層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、第1電極15、第1電極と離間して設けられた第2電極15、及び、第1電極15の上から第2電極15の上に亙り設けられた、有機半導体材料から成る能動層14を少なくとも備えており、第1電極15と能動層14との間、及び、第2電極15と能動層14との間には、電荷注入層16が形成されており、電荷注入層16は、酸化されることで電気伝導度の値が増加した有機材料から成る。

(もっと読む)

グラフェン構造体及びその製造方法、並びにグラフェン素子及びその製造方法

【課題】 グラフェン構造体及びその製造方法、並びにグラフェン素子及びその製造方法を提供する。

【解決手段】 基板上に形成される側面が露出された成長層と、成長層の側面に成長されたグラフェンと、を備えるグラフェン構造体である。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼

性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジ

カルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中

の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の

変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層をチャネルに用いたグラフェントランジスタにおいて、オフリークの低減により低消費電力化をはかる。

【解決手段】グラフェン層をチャネルに用いた電界効果型の半導体装置であって、基板10上に形成され、所定のバンドギャップを有するグラフェン層40から成るチャネル領域45と、チャネル領域45の両側にそれぞれ形成され、バンドギャップがチャネル領域45よりも小さいグラフェン層40から成るソース/ドレイン領域と、ソース/ドレイン領域のチャネル領域45に接する部分の上にそれぞれ形成され、チャネルを横切るように相互に平行配置された2つのゲート電極61,62と、ソース/ドレイン領域のコンタクト部にそれぞれ形成された金属触媒層21,22とを備えた。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】高性能なIII−V族MISFETの実現を可能にする、より効果的なIII−V族化合物半導体表面のパッシベーション技術を提供する。

【解決手段】エピタキシャル成長により化合物半導体層をベース基板上に形成するステップと、前記化合物半導体層の表面をセレン化合物を含む洗浄液で洗浄するステップと、前記化合物半導体層の上に絶縁層を形成するステップと、を有する半導体基板の製造方法を提供する。前記セレン化合物として、セレン酸化物が挙げられる。前記セレン酸化物として、H2SeO3が挙げられる。前記洗浄液が、水、アンモニアおよびエタノールからなる群から選択された1以上の物質をさらに含んでもよい。前記化合物半導体層の表面がInxGa1−xAs(0≦x≦1)からなる場合、前記絶縁層がAl2O3からなるものであることが好ましく、Al2O3は、ALD法により形成されることが好ましい。

(もっと読む)

複層のゲート絶縁層を備えたグラフェン電子素子

【課題】複層のゲート絶縁層を備えたグラフェン電子素子を提供する。

【解決手段】グラフェンチャネル層とゲート電極との間に、有機物絶縁層と無機物絶縁層とからなる複層のゲート絶縁層を備えるグラフェン電子素子である。有機物絶縁層は、グラフェンチャネル層に不純物が吸着することを抑制して、グラフェンチャネル層の本来の特性を維持する。前記有機物絶縁層は、前記無機物絶縁層と前記グラフェンチャネル層との間に配置される。前記有機物絶縁層は、フッ素系高分子を含む。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

101 - 120 / 1,993

[ Back to top ]