Fターム[5F110GG44]の内容

Fターム[5F110GG44]の下位に属するFターム

Fターム[5F110GG44]に分類される特許

81 - 100 / 1,993

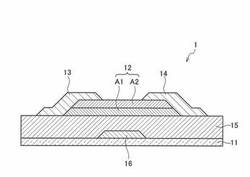

薄膜トランジスタ及びその製造方法、表示装置、イメージセンサー、X線センサー並びにX線デジタル撮影装置

【課題】400℃以下で作製可能であり、30cm2/Vs以上の高い電界効果移動度と、ノーマリーオフとなる低いオフ電流を両立する薄膜トランジスタを提供する。

【解決手段】ゲート電極16と、ゲート電極と接するゲート絶縁膜15と、In(x)Zn(1−x)O(y)(0.4≦x≦0.5,y>0)で表される第1の領域A1及びIn(a)Ga(b)Zn(c)O(d)(b/(a+b)>0.250,c>0,d>0)で表され、ゲート電極に対して第1の領域よりも遠くに位置する第2の領域A2を含み、ゲート絶縁膜を介してゲート電極に対向配置されている酸化物半導体層12と、互いに離間して配置されており、酸化物半導体層を介して導通可能なソース電極13及びドレイン電極14と、を有する薄膜トランジスタ1。

(もっと読む)

窒化物系半導体装置

【課題】ゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、ノーマリオフの双方向動作が可能な窒化物系半導体装置を提供する。

【解決手段】窒化物系半導体素子10は、第1MOSFET部30及び第2MOSFET部31を備えており、第1ゲート電極26と第2ゲート電極27との間に設けられた第1SBD金属電極28及び第2SBD金属電極29がAlGaN層20とショットキー接合されている。第1SBD金属電極28と第1電極24とが接続されており、電気的に短絡していると共に、第2SBD金属電極29と第2電極25とが接続されており、電気的に短絡している。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】ソース電極層又はドレイン電極層に接する第1の酸化物半導体層と、第1の酸化物半導体層上に設けられ第1の酸化物半導体層とは異なるエネルギーギャップを有する第2の酸化物半導体層と、を少なくとも含む酸化物半導体積層を用いてトランジスタを構成する。第1の酸化物半導体層と第2の酸化物半導体層とは互いに異なるエネルギーギャップを有すればよく、その積層順は問わない。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタにおいて、酸化物半導体層の上面部及び下面部に、酸化物半導体層と同種の成分でなるバッファ層が接して設けられたトランジスタ、及び該トランジスタを含む半導体装置を提供する。酸化物半導体層に接するバッファ層としては、アルミニウム、ガリウム、ジルコニウム、ハフニウム、又は希土類元素から選択された一以上の元素の酸化物を含む膜を適用することができる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】少なくともゲート電極層、ゲート絶縁膜、及び半導体層が順に積層されたボトムゲート型のトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

駆動回路、当該駆動回路の作製方法および当該駆動回路を用いた表示装置

【課題】作製中にESDにより半導体素子が破壊されることを抑制する駆動回路および当該駆動回路の作製方法を提供する。また、リーク電流の小さい保護回路が設けられた駆動回路および当該駆動回路の作製方法を提供する。

【解決手段】駆動回路中の半導体素子と電気的に接続して、駆動回路中に保護回路を設け、駆動回路中の半導体素子となるトランジスタと駆動回路中の保護回路を形成するトランジスタを同時に形成することにより、駆動回路の作製中にESDにより半導体素子が破壊されることを抑制する。さらに、駆動回路中の保護回路を形成するトランジスタに酸化物半導体膜を用いることにより、保護回路のリーク電流を低減する。

(もっと読む)

薄膜トランジスタおよびその製造方法、電子機器

【課題】コンパクトでありながら、より安定した動作を行う薄膜トランジスタを提供する。

【解決手段】この薄膜トランジスタは、ゲート電極と、絶縁膜を介してゲート電極と対向して配置された有機半導体層と、この有機半導体層の上に設けられた絶縁性構造体と、互いに離間して配置され、かつ、有機半導体層の上面の一部とそれぞれ接するソース電極およびドレイン電極と、絶縁性構造体を覆い、ソース電極と接続されると共にドレイン電極と分離された導電性材料層とを有する。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体素子の製造方法及び電界効果型トランジスタの製造方法

【課題】光照射時の素子特性を安定化する。

【解決手段】酸化物半導体を主体とする半導体膜を成膜する第一工程と、第一工程後に、半導体膜の面上に第一の絶縁膜を成膜する第二工程と、第二工程後に、酸化性雰囲気中で熱処理する第三工程と、第三工程後に、第一の絶縁膜の面上に第二の絶縁膜を成膜する第四工程と、を有し、第二工程と前記第三工程の際に、第一の絶縁膜の厚みをZ(nm)とし、第三工程での熱処理温度をT(℃)とし、前記第一の絶縁膜及び前記半導体膜中への酸素の拡散距離をL(nm)としたとき、0<Z<L=8×10−6×T3−0.0092×T2+3.6×T−468±0.1の関係式を満たすように第一の絶縁膜の厚みと熱処理温度を調整する。

(もっと読む)

電界効果型トランジスタの製造方法、並びに、電界効果型トランジスタ、表示装置、イメージセンサ及びX線センサ

【課題】光照射時のTFT特性を安定化する。

【解決手段】ゲート電極14上に配置されたゲート絶縁層16上に、第一の酸化物半導体膜24を成膜する第一工程と、第一の酸化物半導体膜24とカチオン組成が異なり、且つ第一の酸化物半導体膜24より低い電気伝導度を有する第二の酸化物半導体膜26を成膜する第二工程と、酸化性雰囲気の下300℃超で熱処理する第三工程と、第一の酸化物半導体膜24とカチオン組成が異なり、且つ第一の酸化物半導体膜24より低い電気伝導度を有する第三の酸化物半導体膜28を成膜する第四工程と、酸化性雰囲気の下300℃超で熱処理する第五工程と、第三の酸化物半導体膜28上に、ソース電極20及びドレイン電極22を形成する電極形成工程と、を有している。

(もっと読む)

非晶質半導体膜の評価方法、及び半導体装置の製造方法

【課題】フラットパネルディスプレイの高性能化に伴い、その製造工程でのアモルファスシリコン(a−Si)膜の評価・管理の必要性が高まってきた。

【解決手段】ガラス基板上にa−Si膜を成膜した試料32に対してレーザ光照射手段36からレーザ光を照射する。試料32におけるレーザ光を照射した各サンプリング点に、マイクロ波照射手段38からマイクロ波を照射し、反射波検出手段40でその反射強度を測定する。各サンプリング点での反射強度の測定結果に基づいて、基板面内でのa−Si膜の物性の均一性を評価する。

(もっと読む)

表示装置

【課題】ゲート絶縁層として要求される耐圧や容量を確保しつつ、外光反射率によるコントラストの劣化を抑えやすくした表示装置を提供する。

【解決手段】透明基板GAと、透明基板GAの上側に形成されるゲート電極GTと、ゲート電極GTの上側に形成される微結晶半導体層MSと、ゲート電極GTと微結晶半導体層MSの間に形成されて、微結晶半導体層MSの外方に延在するゲート絶縁層GIと、ゲート絶縁層GIの微結晶半導体層MSの外方に延在する部分の上面に接して、窒化ケイ素で形成される第2の窒化ケイ素層NI2と、を有し、ゲート絶縁層GIは、第1の窒化ケイ素層NI1と、第1の窒化ケイ素層NI1の上側に形成されて微結晶半導体層MSに接する酸化ケイ素層OIと、を含み、ゲート絶縁層GIは、微結晶半導体層MSの下側の部分よりも第2の窒化ケイ素層NI2の下面に接する部分で薄く形成される、ことを特徴とする表示装置。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】良好な特性を有する複数の有機トランジスタを備えた有機半導体素子の製造方法を提供する。

【解決手段】有機半導体素子10は、基板11と、基板11上に設けられ、各々が液晶性有機半導体材料を含む有機半導体領域4を有する複数の有機トランジスタ20と、を備えている。このうち有機半導体領域4は、少なくとも基板11を含む支持部材17によって支持されている。そして、有機半導体素子10の製造方法は、支持部材17を準備する工程と、支持部材17上に液晶性有機半導体材料を含む連続的な有機半導体層30を設ける工程と、有機半導体層30をパターニングして複数の有機半導体領域4を形成するパターニング工程と、を備えている。ここで、パターニング工程は、凹部42および凸部41を有する凹凸版40を準備する工程と、凹凸版40の凸部41を支持部材17上の有機半導体層30に当接させることにより有機半導体層30をパターニングする当接工程と、を有している。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】酸化物半導体をチャネル形成領域に用いたトランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現するトランジスタ構造を提供する。

【解決手段】異なるエネルギーギャップを有する、少なくとも第1の酸化物半導体層及び第2の酸化物半導体層を積層させた酸化物半導体積層であって、化学量論的組成比よりも過剰に酸素を含む領域を有する酸化物半導体積層を用いてトランジスタを形成する。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】良好な特性を有する複数の有機トランジスタを備えた有機半導体素子の製造方法を提供する。

【解決手段】有機半導体素子10は、基板11と、基板11上に設けられ、各々が有機半導体材料を含む有機半導体領域4を有する複数の有機トランジスタ20と、を備えている。このうち有機半導体領域4は、少なくとも基板11を含む支持部材17によって支持されている。そして、有機半導体素子10の製造方法は、支持部材17を準備する工程と、支持部材17上に有機半導体材料を含む連続的な有機半導体層30を設ける工程と、有機半導体層30をパターニングして複数の有機半導体領域4を形成するパターニング工程と、を備えている。ここで、パターニング工程は、凹部42および凸部41を有する凹凸版40を準備する工程と、凹凸版40の凸部41を支持部材17上の有機半導体層30に当接させることにより有機半導体層30をパターニングする当接工程と、を有している。

(もっと読む)

81 - 100 / 1,993

[ Back to top ]