Fターム[5F110GG44]の内容

Fターム[5F110GG44]の下位に属するFターム

Fターム[5F110GG44]に分類される特許

141 - 160 / 1,993

機能性基体及びその製造方法

【課題】薄膜電子回路を転写するに際し、接着と剥離の作業による薄膜電子回路へのダメージを最小限にして、十分な接着強度と適度な硬さを有した接着剤を用いる。

【解決手段】薄膜電子回路の作製に必要な単層または複数の層からなる膜構造と転写先の基体とをガラス転移温度が100℃以上、150℃以下、吸水率が0.1%以下、引っ張りせん断強さ10N/mm2以上、T型剥離接着強さ1N/mm2以上、線膨張率1.0×10−4以下であることを特徴とするエポキシ系あるいはアクリル系接着層の単層のみか、または当該エポキシ系あるいはアクリル系接着層の上にシリコーン樹脂、アクリル変成シリコーン樹脂あるいはエポキシ変成シリコーン樹脂材料からなる弾性層を伴った機能性基体でもって転写プロセスを行う。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

薄膜トランジスタ基板の製造方法およびトップゲート構造薄膜トランジスタ基板

【課題】本発明は、簡便な工程で製造可能な、電荷注入効率に優れた薄膜トランジスタ基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に金属電極層を形成する金属電極層形成工程と、上記金属電極層の上面に、電子吸引性または電子供与性の官能基を有する表面処理剤で表面処理を行うことにより、表面処理層積層体を形成する表面処理工程と、上記表面処理層積層体をパターニングし、ソース電極およびドレイン電極を形成するパターニング工程と、上記ソース電極および上記ドレイン電極上に有機半導体層を形成する有機半導体層形成工程と、上記有機半導体層上にゲート絶縁層を形成するゲート絶縁層形成工程と、上記ゲート絶縁層上にゲート電極を形成するゲート電極形成工程と、を有することを特徴とする薄膜トランジスタ基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】電界効果トランジスタであって、半導体基板10上に垂直に形成され、且つ第1の領域が第2の領域よりも高く形成された半導体フィン31と、第1の領域の両側面にゲート絶縁膜40を介して設けられたゲート電極50と、第2の領域に第1の領域の上端よりも低い位置まで設けられた、合金半導体からなるソース・ドレイン下地層63,73と、下地層63,73上に第1の領域の上部を挟むように設けられた、下地層63,73とは格子定数の異なるソース・ドレイン領域60,70とを備えている。チャネル領域には応力が付与され、下地層63,73は、空乏層が収まる厚さよりも厚く、熱平衡状態で結晶にミスフィット転位が導入される熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

コプレナ型の酸化物半導体素子とその製造方法

【課題】折り曲げ耐性が向上したコプレナ型の酸化物半導体を提供し、また、コンタクトホールを精巧に形成するコプレナ型の酸化物半導体の製造方法を提供する。

【解決手段】絶縁性を有する基板と、前記基板上に配置され、チャネル領域及び電極接続領域を有する酸化物半導体層と、前記酸化物半導体層上に配置され、コンタクトホールを有するゲート絶縁層と、前記ゲート絶縁層上に配置されたソース電極、ドレイン電極、及びゲート電極と、を有するコプレナ型の酸化物半導体素子であって、前記ゲート絶縁層は、架橋ポリマーで形成されていることを特徴とするコプレナ型の酸化物半導体素子とその製造方法。

(もっと読む)

グラフェン電子素子及び製造方法

【課題】グラフェン電子素子及び製造方法を提供する。

【解決手段】ゲート電極として作用する導電性基板と、基板上に配置されたゲートオキサイドと、ゲートオキサイド上で互いに離隔された一対の第1金属と、第1金属上で、第1金属の間に延びたグラフェンチャネル層と、グラフェンチャネル層の両端にそれぞれ配置されたソース電極及びドレイン電極と、を備えるグラフェン電子素子である。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】低温成膜可能な酸化物で半導体膜を形成した逆スタガ型薄膜トランジスタであって、半導体膜上に形成した保護膜の紫外線等に対する耐光性と耐環境安定性を向上させてなる薄膜トランジスタ及びその製造方法を提供する。

【解決手段】基板1上にパターン形成されたゲート電極2と、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上にパターン形成された酸化物半導体膜4と、酸化物半導体膜4上にパターン形成されたソース電極6S及びドレイン電極6Dと、ソース電極6S及びドレイン電極6D間に露出する酸化物半導体膜4を少なくとも覆う保護膜7とを有するボトムゲートトップコンタクト構造の薄膜トランジスタ10であって、保護膜7を、酸化物半導体材料で形成する。このとき、酸化物半導体膜4及び保護膜7が、InMZnO(MはGa,Al,Feのうち少なくとも1種)を含むアモルファス酸化物である酸化物半導体材料からなることが好ましい。

(もっと読む)

トランジスタ、その製造方法および表示装置

【課題】ソース電極およびドレイン電極からのオーミックコンタクト膜の延在部分の表面を介したリーク電流、およびオーミックコンタクト膜と半導体能動膜との接合側面部での欠陥を介したリーク電流を増大させないことが可能な薄膜トランジスタを提供することにある。

【解決手段】オーソミックコンタクト層8の一方は、電極9,10の一方に接触して覆われた接触部分81と、接触部分81よりも厚さ方向D2において薄く、厚さ方向D2から見て電極9,10の一方からはみ出して電極9,10の他方へと延在して半導体能動膜7の少なくとも一部71を避けて覆う延在部分82とを有する。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体記憶装置

【課題】SOI構造のDRAMの提供

【解決手段】

半導体基板1上に複数層の絶縁膜(2、3、4、5)が選択的に設けられ、絶縁膜5上より、絶縁膜5が設けられていない領域上に延在して選択的に半導体層(8、9、10)が設けられ、半導体層の一部9の全周囲にゲート絶縁膜16を介し、絶縁膜4上に包囲構造のゲート電極17が設けられ、ゲート電極に自己整合し、直下に空孔7を有する半導体層の一部10にドレイン領域(14、15)が、半導体層の一部8にソース領域(12、13)が設けられた構造のMIS電界効果トランジスタと、ソース領域12の側面に一部を接し、絶縁膜(3、5)中にトレンチが設けられ、トレンチの側面に電荷蓄積電極19が設けられ、電荷蓄積電極の側面及び上部にキャパシタ絶縁膜20を介してセルプレート電極21が設けられた構造のトレンチ型キャパシタと、により構成されたDRAM。

(もっと読む)

金属酸化物粒子分散組成物

【課題】成膜後の金属酸化物粒子の緻密性を改善することができ、所望の性能を有する金属酸化物半導体薄膜や透明導電膜を形成することが可能な金属酸化物粒子分散組成物を提供する。

【解決手段】金属酸化物粒子と、金属塩及び/又は有機金属化合物と、溶媒とを含有する透明導電膜形成用の金属酸化物粒子分散組成物であって、前記金属酸化物粒子は、Zn、Ga、In、Sn、Al、Sb、Cd及びFeからなる群より選択される少なくとも1種の金属の酸化物を含有し、かつ、前記金属塩及び/又は有機金属化合物は、Zn、Ga、In、Sn、Al、Sb、Cd及びFeからなる群より選択される少なくとも1種の金属の金属塩及び/又はZn、Ga、In、Sn、Al、Sb、Cd及びFeからなる群より選択される少なくとも1種の金属を含む有機金属化合物である金属酸化物粒子分散組成物。

(もっと読む)

電子デバイス及びその製造方法

【課題】転写プロセスを用いずに、所期のグラフェンを制御性良く容易且つ確実に安定形成し、信頼性の高い高性能の微細な電子デバイスを実現する。

【解決手段】基板1上に絶縁層2を形成し、絶縁層2に空隙2Aを形成し、空隙2Aに触媒材料4を充填し、絶縁層2における触媒材料4の露出面4aにグラフェン5を形成し、絶縁層2上でグラフェン5の両端部に接続するように一対の電極5,6を形成し、グラフェン5を一部除去してグラフェンリボン8を形成し、グラフェンリボン8の除去された部位である間隙2A1,2A2を通じて触媒材料4を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極及び空孔付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に選択的に一対の第1の半導体層6が設けられ、第1の半導体層6にそれぞれ1側面を接し、空孔5上に一対の第2の半導体層8が設けられ、第2の半導体層8間に2側面を接し、残りの周囲にゲート絶縁膜14を介してゲート電極15に包囲された、歪み構造の第3の半導体層7が設けられ、第1及び第2の半導体層(6、8)には概略ソースドレイン領域(10、11、12、13)が設けられ、第3の半導体層7には概略チャネル領域が設けられ、ソースドレイン領域(10、13)及び包囲型ゲート電極15には配線体(19、20、22、23)が接続されているMISFET。

(もっと読む)

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

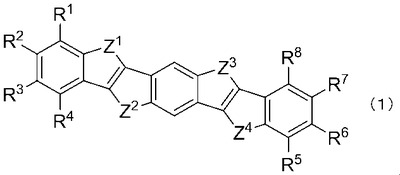

可溶性ヘテロアセン化合物及び該化合物を含有する薄膜および有機トランジスタ

【課題】有機半導体材料として好適な新規化合物の提供。

【解決手段】下記式(1)で示される化合物。

[式中、Z1〜Z4はそれぞれ独立に、硫黄原子又はセレン原子を表す。R1〜R8はそれぞれ独立に、水素原子、フッ素原子で置換されていてもよい炭素数1〜30のアルキル基、フッ素原子で置換されていてもよい炭素数1〜30のアルコキシ基、又は特定な置換シリル基を表す。]

(もっと読む)

141 - 160 / 1,993

[ Back to top ]