Fターム[5F110GG44]の内容

Fターム[5F110GG44]の下位に属するFターム

Fターム[5F110GG44]に分類される特許

201 - 220 / 1,993

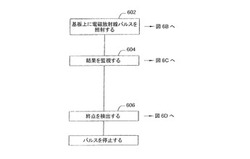

パルス列アニーリング方法および装置

【課題】基板の所望の領域上でアニーリングプロセスを実行するために使用される装置および方法を開示する。

【解決手段】1つの実施形態では、電磁エネルギのパルスはフラッシュランプまたはレーザ装置を使用して基板に送出される。パルスは約1nsecから約10msecの長さであってもよく、各パルスは基板材料を融解するのに必要なエネルギより少ないエネルギを有する。パルスの間隔は一般的に、各パルスにより与えられるエネルギを完全に放散させるのに十分な長である。このようにして、各パルスはマイクロアニーリング周期を終了する。パルスは1回で基板全体にまたは同時に基板の一部に送出されてもよい。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの活性層に好適に用いられる非晶質酸化物の製造方法を提供する。

【解決手段】基板1上に、非晶質酸化物層2を形成する前に、基板1表面にオゾン雰囲気中で紫外線を照射したり、基板1表面にプラズマを照射したり、あるいは基板1表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物層2を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板1上に、非晶質酸化物層2を形成する後に、非晶質酸化物層2の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの活性層に好適に用いられる非晶質酸化物の製造方法を提供する。

【解決手段】基板1上に、非晶質酸化物層2を形成する前に、基板1表面にオゾン雰囲気中で紫外線を照射したり、基板1表面にプラズマを照射したり、あるいは基板1表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物層2を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板1上に、非晶質酸化物層2を形成する後に、非晶質酸化物層2の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

有機EL表示装置用シリコン膜検査方法及び有機EL表示装置用シリコン膜検査装置

【課題】シリコン膜を精度良く検査するシリコン膜検査方法を提供することを目的とする。

【解決手段】本発明は、シリコン膜の形成された領域を第1膜厚の第1領域と前記第1膜厚と異なる第2膜厚の第2領域とに仮想的に分割する分割工程と、互いに異なる波長の第1波長と第2波長とを含む照射光を前記シリコン膜に照射する照射工程と、前記照射光が照射された前記第1領域からの前記第1波長の第1反射光を用いて第1反射率の測定を行う第1測定工程と、前記第1反射率から前記シリコン膜の第1結晶化率を導出する第1導出工程と、前記照射光が照射された前記第2領域からの前記第2波長の第2反射光を用いて第2反射率の測定を行う第2測定工程と、前記第2反射率から前記シリコン膜の第2結晶化率を導出する第2導出工程と、を含む有機EL表示装置用シリコン膜検査方法を提供する。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタに関する新規な製造方法を提供する。

【解決手段】基板上に、非晶質酸化物層を形成する前に、基板表面にオゾン雰囲気中で紫外線を照射したり、基板表面にプラズマを照射したり、あるいは基板表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物を含み構成される活性層を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板上に、非晶質酸化物層を形成する後に、非晶質酸化物層の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

薄膜トランジスタ用ゲート絶縁膜および該絶縁膜を備えた薄膜トランジスタ素子

【課題】低温条件下かつ溶液塗布プロセスにより形成可能であり、薄膜トランジスタにおける電気特性であるヒステリシス、On/Off比が良好な薄膜トランジスタ用ゲート絶縁膜及び該絶縁膜を備えた薄膜トランジスタを提供する。

【解決手段】必須成分として(A)アルケニル基を有する化合物、(B)SiH基を有する化合物、(C)ヒドロシリル化触媒を含有する硬化性組成物を低温条件下によるポストベイクしたゲート絶縁膜を用いることにより、良好なトランジスタ特性が発現する。

(もっと読む)

スパッタリングターゲット、半導体装置および半導体装置の製造方法

【課題】Cu配線層に含まれるCuの周囲への拡散を抑制すると共に密着性および動作特性に優れた半導体装置およびその製造方法、並びに、その半導体装置の製造に用いるスパッタリングターゲットを提供する。

【解決手段】実施の形態に係るスパッタリングターゲットは、1.5原子%以上5.0原子%以下のMnと、(Mgの原子%)/(Mnの原子%)で示される比率が0.3以上2.1以下となるMgと、10wtppm以下のCと、2wtppm以下のO2と、を含むCu合金を用いて形成される。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのスイッチング速度を高速化した半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、絶縁層の一部上に形成された半導体層10と、半導体層10の側面10aに形成され、第1のゲート絶縁膜21、第1のゲート電極22、並びにソース及びドレインとなる2つの第1の不純物層23,24を有する第1のトランジスタ20と、半導体層10の側面10bに形成され、第2のゲート絶縁膜31、第2のゲート電極32、並びにソース及びドレインとなる2つの第2の不純物層33,34を有する第2のトランジスタ30とを具備する。

(もっと読む)

電界効果型トランジスタ、表示素子、画像表示装置、及びシステム

【課題】新規なp型酸化物半導体を活性層に用いた電界効果型トランジスタなどの提供。

【解決手段】ゲート電圧を印加するためのゲート電極と、電流を取り出すためのソース電極及びドレイン電極と、前記ソース電極及び前記ドレイン電極との間に形成されたp型酸化物半導体からなる活性層と、前記ゲート電極と前記活性層との間に形成されたゲート絶縁層とを有し、前記p型酸化物半導体が、一般式ABO3(Aは、Sr及びBaの少なくともいずれかを含む。Bは少なくともBiを含む。)で表され、かつ擬ペロブスカイト構造である電界効果型トランジスタである。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタの電気特性は、基板内、基板間およびロット間において、ばらつきが大きく、熱、バイアスまたは光などの影響で変動が起こる場合がある。そこで、信頼性が高く、電気特性のばらつきの小さい酸化物半導体を用いた半導体装置を作製する。

【解決手段】酸化物半導体を用いたトランジスタにおいて、膜中および膜と膜との界面の水素を排除する。膜と膜との界面の水素を排除するためには、成膜と成膜との間で、基板を真空下で搬送する。また、大気暴露された表面を持つ基板は、熱処理またはプラズマ処理によって、表面の水素を除去する。

(もっと読む)

放射線撮像装置、放射線撮像表示システムおよびトランジスタ

【課題】被曝量による閾値電圧のシフトを抑制するが可能なトランジスタを提供する。

【解決手段】放射線撮像装置1は、フォトダイオードとトランジスタ111Bとを含む光電変換層を有する。トランジスタ111Bは、基板11上に、第1ゲート電極120A、第1ゲート絶縁膜129、半導体層126、第2ゲート絶縁膜130および第2ゲート電極120Bをこの順に有し、第1ゲート絶縁膜129および第2ゲート絶縁膜130におけるSiO2膜の総和が65nm以下となっている。トランジスタが被曝すると、ゲート絶縁膜におけるSiO2膜に正孔がチャージされ、閾値電圧がシフトし易くなるが、上記のようなSiO2膜厚の最適化により、閾値電圧シフトが効果的に抑制される。

(もっと読む)

チャネルエッチ型薄膜トランジスタとその製造方法

【課題】半導体層の膜厚均一性を向上させたチャネルエッチ型TFTとその製造方法を提供する。

【解決手段】酸化物半導体からなるチャネル層4を形成した後、該チャネル層4の上にIn、Zn、Gaを含む酸化物からなり、上記酸化物半導体よりもエッチングレートが速く、抵抗率が3.38×107Ωcm以下である犠牲層5を形成し、その上にソース電極6及びドレイン電極7を形成して、該ソース電極6とドレイン電極7の間に露出した犠牲層5をウェットエッチング除去することにより、半導体層膜厚の均一性を向上させ、TFT特性とその均一性と、をより向上させることができる。

(もっと読む)

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

スパッタリングターゲット、スパッタリングターゲットの作製方法および半導体装置の作製方法

【課題】酸窒化物膜を作製する成膜技術を提供する。また、その酸窒化物膜を用いて信頼性の高い半導体素子を作製する。

【解決手段】窒化インジウム、窒化ガリウム、窒化亜鉛の少なくとも1つを原料の一とし、これと、酸化インジウム、酸化ガリウム、酸化亜鉛の少なくとも1つと混合して窒素雰囲気中で焼結したインジウムとガリウムと亜鉛を有する酸窒化物よりなるスパッタリングターゲットを用いて酸窒化物膜を作製することにより、必要な濃度の窒素を含んだ酸窒化物膜が得られる。得られた酸窒化物膜はトランジスタのゲートやソース電極、ドレイン電極等に用いることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

201 - 220 / 1,993

[ Back to top ]