Fターム[5F110HJ16]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物の導入方法 (4,201) | 拡散 (325) | 固相拡散 (107)

Fターム[5F110HJ16]に分類される特許

61 - 80 / 107

半導体装置及びその製造方法

【課題】フォトマスクの枚数を低減しながらも、容易且つ高精度に半導体装置を製造する。

【解決手段】ゲート配線5と、ソース配線6と、ゲート配線5及びソース配線6に接続された薄膜トランジスタ12と、薄膜トランジスタ12に接続された絵素電極11とを備えた半導体装置1を製造する場合に、絵素電極11とソース配線6とを同時にパターン形成する。

(もっと読む)

印刷されたドーパント層

【課題】MOSトランジスタなどの電子デバイスを形成する方法であって、比較的安価で時間のかからない処理技術の提供。

【解決手段】基板10上に複数の半導体アイランド31,35を形成するステップと、半導体アイランドの第1のサブセット31上に或いはそれよりも上側に第1の誘電体層60を印刷するとともに、随意的に半導体アイランドの第2のサブセット35上に或いはそれよりも上側に第2の誘電体層65を印刷する。第1の誘電体層60は第1のドーパントを含み、(随意の)第2の誘電体層65は第1のドーパントとは異なる第2のドーパントを含む。誘電体層60,65、半導体アイランド31,35及び基板10は、第1のドーパントを半導体アイランドの第1のサブセット31中へ拡散させ、且つ存在する場合には第2のドーパントを半導体アイランドの第2のサブセット35中へ拡散させるように十分にアニールされる。

(もっと読む)

半導体装置の製造方法

【課題】オフリーク電流を押さえて高い電流駆動力を有し、オフセット電圧が極力低減された微細な半導体装置の製造方法を提供する。

【解決手段】半導体基板に、一対の素子分離絶縁膜を離間して形成し、素子領域を画定する工程と、半導体基板の素子領域におけるチャネル領域の上に、ゲート絶縁膜を介してゲート長30nm以下のゲート電極を形成する工程と、ゲート電極側面にオフセットスペーサーを形成する工程と、オフセットスペーサー及びゲート電極をマスクとしてゲート電極の直下を除く半導体基板に不純物を導入し、フラッシュランプアニールを用いて1000℃以上で100msec以下の極短時間加熱処理を施して不純物を活性化し、ゲート電極の端部から10nm以下の距離で離間した不純物拡散領域を形成する工程と、半導体基板の全面に層間絶縁膜を形成してコンタクトホールを開口し、導電材料で埋め込んで配線を形成する工程とを具備することを特徴とする。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】 LSIを構成する微細な縦型電界効果型トランジスタ、特に半導体層の両側にゲート電極を有するダブルゲート縦型電界効果型トランジスタの製造方法として最適な縦型電界効果型トランジスタの製造方法を提供する。

【解決手段】 矩形断面を持つ半導体領域を跨ぐように、ゲート絶縁膜を介してゲート電極5を設け、続いてゲート電極5のうち、少なくとも前記略矩形の断面を持つ半導体領域の上端よりも低い位置を絶縁膜で覆うとともに、前記略矩形の断面を持つ半導体の側面のうちゲート電極に覆われない領域の少なくとも一部を露出させ、前記露出した前記略矩形の断面を持つ半導体の側面に、半導体を選択的に成長させ、選択成長と同時または選択成長後に選択的に成長させた前記半導体に不純物を導入することにより、選択的に成長させた前記半導体をソース/ドレイン領域もしくはソース/ドレインエクステンション領域となす

(もっと読む)

薄膜半導体装置の製造方法および薄膜半導体装置

【課題】半導体薄膜の表面層に浅い接合の拡散層を形成することが可能で、これによりLDD領域を設けることなくドレイン端においての電界を緩和してリーク電流を均一に抑えることができる薄膜トランジスタの製造方法を提供する。

【解決手段】半導体薄膜5上にゲート絶縁膜7を介してゲート電極9をパターン形成する。半導体薄膜5の表面にp型またはn型の不純物aを含む溶液の液膜を形成して乾燥させた不純物膜Aを形成する。ゲート電極9をマスクとし、不純物膜Aを介して半導体薄膜5にエネルギービームh’をスポット照射する。これにより、不純物aを半導体薄膜5の表面層のみに拡散させた浅い拡散層からなるソース/ドレイン11を形成する。

(もっと読む)

プリント不揮発性メモリ

【課題】不揮発性メモリセル、並びに薄膜トランジスタ及びそれらを含む回路を様々な基板上に作成する方法を提供する。

【解決手段】この不揮発性メモリセルは、同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランドが制御ゲート2を構成し、第2の半導体アイランドがソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランドの少なくとも一部の上のゲート誘電体層と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体5層と、ゲート誘電体4層とトンネリング誘電体層の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

半導体装置の製造方法

【課題】薄膜のSOI層を持つSOI−MOSFETにおいて、基板浮遊効果を抑制するボディコンタクト構造の半導体装置の製造方法を提供する。

【解決手段】絶縁体上の半導体層上において、素子領域及びボディコンタクト領域を覆うCMPマスクを形成する工程と、全体を前記CMPマスクの材料とは異なる第2の絶縁体で覆い続いてCMPにより第2の絶縁体を平坦化する工程と、CMP工程後により露出した前記CMPマスク材料を除去し、露出した半導体層にはゲート絶縁膜、ゲート電極及び第1導電型のソース/ドレイン領域を持つ電界効果型トランジスタ、およびまたは第2導電型の不純物が高濃度に導入されたボディコンタクト領域を形成することを特徴とする。

(もっと読む)

シリコンナノワイヤに基づくトンネル効果トランジスタ

【課題】トンネル電界効果トランジスタ(TFET)は、金属酸化物半導体電界効果トランジスタ(MOSFET)の後継者と考えられるが、シリコンベースのTFETは一般に低いオン電流、トンネルバリアの大きな抵抗に関する欠点を有する。

【解決手段】より高いオン電流を達成するために、他のシリコン(Si)チャネル中にゲルマニウム(Ge)トンネルバリアを備えたナノワイヤベースのTFETが用いられる。ナノワイヤは、シリコンとゲルマニウムの間の格子不整合が、高い欠陥のある界面とならないように導入される。従来のMOSFET構造に比較して、静的電力の低減と共に動的電力の低減が得られる。これにより、多層ロジックは、ナノワイヤSi/GeTFETを用いることで、非常に高いオンチップトランジスタ密度となる。

(もっと読む)

半導体装置

【課題】 本発明は、同一基板上に同時に異なるLDD構造を有する生産性の高いTFTの作製方法およびその構造を提供することを目的としている。即ち、本発明はTFTの新規な構造と生産性の高い製造工程を提供するものである。

【解決手段】 耐熱性の高いTa膜またはTaを主成分とする膜を配線材料に用い、さらに保護層で覆うことで、高温(400〜700℃)での加熱処理を施すことが可能となり、且つ保護層をエッチングストッパーとして用いることで周辺駆動回路部においては、サイドウォール126を用いた自己整合プロセス(セルフアライン)によるLDD構造を備えたTFTを配置する一方、画素マトリクス部においては、絶縁物125を用いた非自己整合プロセス(ノンセルフアライン)によるLDD構造を備えたTFTを配置する

(もっと読む)

半導体装置及びその製造方法

【課題】半導体製造工程で加わる熱履歴の違いに因り、不純物の拡散具合が異なることから、薄膜トランジスタの閾値にばらつきを生じた。これを低減、防止する対策を施した薄膜トランジスタを有する半導体装置及びその製造方法を提供する。

【解決手段】薄膜トランジスタは、絶縁体層を介して半導体基板上に形成された、不純物を含むソース/ドレイン領域と、前記ソース/ドレイン領域間を充填する絶縁体と、前記ソース/ドレイン領域上に形成された不純物拡散制御膜層と、前記不純物拡散制御膜上に形成されたチャネル層と、前記チャネル層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記チャネル層、ゲート絶縁膜及びゲート電極を充填する層間膜とを具備する。前記不純物拡散制御膜は、熱の加わらない製造工程の段階になって、前記ソース/ドレイン領域とチャネル層との間に所定の電圧を印加することにより絶縁破壊される。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】液状シリコンを利用して薄膜トランジスタのポリシリコンチャネル層を形成することによって、製造工程を単純化した薄膜トランジスタ及びその製造方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたソース/ドレイン電極と、ソース/ドレイン電極上の全面に形成されたドーピング層と、ソース/ドレイン電極間にゲート絶縁膜とドーピング層上に形成されたポリシリコンチャネル層とを含み、ドーピング層は、チャネル層とオーバーラップする領域に形成された。

(もっと読む)

印刷式自己整合トップゲート型薄膜トランジスタ

【課題】高性能のトップゲート型TFTを印刷方式で製造することを可能にする薄膜トランジスタを提供する。

【解決手段】半導体薄膜層2を形成するステップと、その上に、TFTのチャネル領域を画成するギャップ5が形成されたドープトガラスパターン4を印刷するステップと、チャネル領域の上又は上方に、ゲート誘電体膜及びこの上のゲート伝導体3を有するゲート電極を形成するステップと、ドープトガラスパターンから半導体薄膜層にドーパントを拡散させるステップとを含む自己整合トップゲート型薄膜トランジスタ(TFT)及びそのような薄膜トランジスタの製造方法。

(もっと読む)

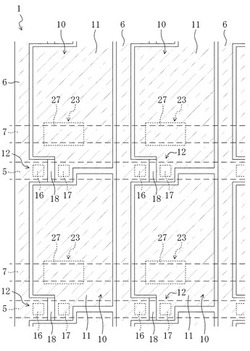

カラー液晶表示装置、カラー表示装置

【課題】フォトリソグラフィー工程数を低減することで製造コストの低減および歩留まりの向上を実現し得るカラー表示装置の製造方法を提供する。

【解決手段】透明基板710上にソース線705、ドレイン電極708となる線状遮光体701、701kを形成した後、開口部711に色素材702を定着させてカラーフィルターとする。次に、色素材を覆う透明保護膜723を成膜し、その上に多結晶シリコン薄膜717を形成する。そして、画素マトリックス外のソース線端子を覆うポリイミド膜を形成した後、ゲート絶縁膜719を成膜し、ポリイミド膜を除去する。次に、ゲート絶縁膜上にゲート線707を形成する。本方法におけるフォトリソグラフィー工程は、線状遮光体形成、多結晶シリコン薄膜形成、ゲート電極形成、の3工程のみとなる。

(もっと読む)

酸化物膜をチャネルに用いた電界効果型トランジスタ及びその製造方法

【課題】トランジスタの特性(Id−Vg特性)にばらつきが生じる場合があった。

【解決手段】酸化物膜を半導体層11として有する電界効果型トランジスタであって、酸化物膜の中に、水素又は重水素が添加されたソース部位及びドレイン部位を有している。または、酸化物膜の中に、チャンネル部位18とソース部位16とドレイン部位17とを有し、ソース部位とドレイン部位との水素又は重水素の濃度がチャンネル部位の水素又は重水素の濃度よりも大きい。ソース部位とドレイン部位が、ゲート絶縁層を介して配されるゲート電極と自己整合して配され、且つ、コプレーナ構造からなる構成をとることができる。

(もっと読む)

半導体装置の製造方法、電子光学装置の製造方法および電子機器の製造方法

【課題】不純物ドープ半導体膜を形成する際の熱負荷を低減する。また、熱負荷を低減することで、TFTの特性を向上させる。

【解決手段】半導体膜3および絶縁膜5を順次形成し、これらの膜よりなる積層膜した後、この積層膜を選択的に除去することにより、プール部7bおよびこのプール部7bに連結した一対の溝7aを形成し、プール部7bにドープ高次シラン組成物溶液9を充填し、この溶液9を溝7a内部に導入した後、熱処理によりドープシリコン膜9Aを形成する。次いで、溝7a間に位置する絶縁膜5上にゲート電極を形成することによりTFTを形成する。

(もっと読む)

CMOS回路の製造方法及びトランジスタ装置

【課題】少数の工程段階又はマスキング段階しか必要としないトランジスタの製造方法を提供する。

【解決手段】基板(1)上に第1の種類及び第2の種類のトランジスタ(20,21)を製造する方法において、

a)第1の種類のトランジスタ(20)の後になっての接触領域(3a,3b)に第1の 伝導型のドーピングされた半導体領域を形成し、

b)第1の真性半導体層(4)を全面に析出し、

c)真性半導体層(4)に第1の伝導型の接触領域(3a,3b)が生じるように、半導 体領域にあるドーパントを活性化し、

d)ゲート誘電体(6)を析出し、

e)第1の導電層(7)の析出及びこの導電層(7)の構造化によりゲート電極(7a,7b)を形成し、

f)第2の種類のトランジスタ(21)のため第2の伝導型の接触領域(8)を形成する ドーパントによりイオンドーピングし、

g)不活性化層(10)を析出し、

h)接触開口(K)をあけ、

i)第2の導電層(11)を析出しかつ構造化する。

(もっと読む)

トランジスタとそのトランジスタの製造方法及びこれを適用する有機発光ディスプレイ

【課題】トランジスタとそのトランジスタの製造方法及びこれを適用する有機発光ディスプレイを提供する。

【解決手段】相互に平行して配置され、チャンネル領域とチャンネル領域の両側にドーピングされた二つの高伝導領域とを有する二つの多結晶シリコン層10a、10bと、二つの多結晶シリコン層10a、10bのチャンネル領域に対応して配置され、二つの多結晶シリコン層10a、10bと交差するように形成されたゲート12と、ゲート12と多結晶シリコン層10a、10bとの間に介在されるゲート絶縁層と、を備え、ゲート12の一側端部に隣接して形成され、ニつの多結晶シリコン層10a、10bのチャンネル領域と一側の高伝導領域との間に低伝導領域が形成されている構造を有している。

(もっと読む)

プロセス変動に耐性を有するダイオード、同ダイオードを有するスタンダードセル、同ダイオードを含むタグ及びセンサ、並びに同ダイオードを製造する方法

【課題】プロセス変動に耐性を有するダイオード及びダイオード接続薄膜トランジスタ(TFT)を提供する。

【解決手段】ダイオード又はTFTを含む印刷又はパターニング構造(例えば、回路)、これらを製造する方法、並びに、これらの識別タグ及びセンサへの応用を開示する。相補型のダイオード対又はダイオード接続TFTを直列に含む印刷された構造は、印刷又はレーザ描画技術を用いて製造したダイオードの閾値電圧(Vt)を安定化することができる。NMOS TFTのVt(Vtn)とPMOS TFTのVt(Vtp)の間の分離を利用して、印刷又はレーザ描画のダイオードの順方向電圧降下の安定性を確立又は向上する。更なる応用は、参照電圧発生器、電圧クランプ回路、参照又は差動信号伝送ラインにおける電圧を制御する方法、並びにRFID及びEASタグ及びセンサに関する。

(もっと読む)

半導体装置

【課題】可及的に簡略な構成で、かつ高集積度、高性能の半導体装置を得ることを可能にする。

【解決手段】半導体基板1上に板状に設けられた第1導電型の第1半導体領域3と、第1半導体領域の第1側面に設けられた第1強誘電体絶縁膜4と、第1強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第1ゲート電極6と、第1半導体領域の第2側面に設けられた第2強誘電体絶縁膜5と、第2強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第2ゲート電極7と、第1及び第2ゲート電極に挟まれるように第1半導体領域に形成されるチャネル領域と、チャネル領域の両側の第1半導体領域に設けられた第2導電型の第1ソース・ドレイン領域8と、を備え、第1半導体領域の厚さが第1半導体領域の不純物濃度で決まる空乏層の最大厚さの二倍よりも薄い。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース、ドレインおよびチャネルが同導電型で構成されたトランジスタにおいて、ソース−ドレイン間の導通を良好に遮断する。

【解決手段】半導体装置100は、半導体基板102上にBOX層110およびSOI層106がこの順で形成されたSOI基板と、SOI層106に形成された第1導電型のドレイン領域106aおよび106bと、これらの間に設けられた第1導電型のチャネル領域106cと、チャネル領域106c上に形成されたゲート絶縁膜112およびその上に形成された第1のゲート電極114とを含む。チャネル領域106cの下方にドープトシリコンまたは金属からなる導電層108がSOI層106の膜厚よりも狭い間隔で設けられる。また、チャネル領域106cと導電層108との間にBOX層110が設けられる。

(もっと読む)

61 - 80 / 107

[ Back to top ]