Fターム[5F110HJ16]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物の導入方法 (4,201) | 拡散 (325) | 固相拡散 (107)

Fターム[5F110HJ16]に分類される特許

41 - 60 / 107

薄膜トランジスタ及びその製造方法

【課題】電気的ストレスによる閾値電圧変化の小さいコプラナー構造の薄膜トランジスタ及びその製造方法を提供する。

【解決手段】基板の上に、ゲート電極と、ゲート絶縁層と、ソース電極とドレイン電極とチャネル領域とからなる酸化物半導体層と、チャネル保護層と、層間絶縁層と、を少なくとも有する薄膜トランジスタであって、前記チャネル保護層は1層以上で形成され、そのうち前記酸化物半導体層と接する層は酸素を含む絶縁体からなり、該チャネル保護層の端部の膜厚が該チャネル保護層の中央部の膜厚と比べ薄く、かつ、前記層間絶縁層は水素を含有しており、該層間絶縁層と直接接している該酸化物半導体層の領域がソース及びドレイン電極をなしていることを特徴とする。

(もっと読む)

伸張可能及び折畳み可能な電子デバイス

本明細書においては、デバイスを作成するための、伸張可能、折畳み可能、及び任意にはプリント可能なプロセスと、伸張、圧縮、撓曲、又は他の態様で変形される場合に良好な性能を示すことが可能な、半導体、電子回路、及びそれらの構成要素などの、伸張可能、折畳み可能、及び任意にはプリント可能なデバイスとが、開示される。歪み隔離層は、機能デバイス層に対して良好な歪み隔離をもたらす。多重層デバイスは、歪み誘起破損を受けやすい材料を含む機能層に対してコインシデントである又は近位に位置するようにニュートラル機械表面を位置決めするように、構築される。ニュートラル機械表面は、多重層デバイスの層のいずれかをパターニングすることなどにより、空間的に不均一である特性を有する1つ又は複数の層によって位置決めされる。 (もっと読む)

表示装置およびその製造方法

【課題】 製造の工数を低減できる表示装置の提供。

【解決手段】 基板上にp型薄膜トランジスタを備える表示装置であって、

前記p型薄膜トランジスタは、

ゲート電極の上面に絶縁膜を介して半導体層が形成され、

前記半導体層の上面に離間部を有して互いに対向配置されるドレイン電極とソース電極とが形成され、

前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、p型不純物の拡散層が形成されて構成されている。

(もっと読む)

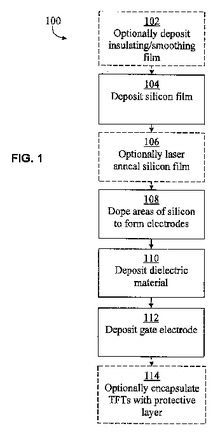

シリコン薄膜トランジスタ、並びにその製造システム及び方法

可撓性基板上に、自己整合シリコン薄膜トランジスタを製造するシステム及び方法。前記システム及び方法は、高いパフォーマンスのトランジスタを製造するために、精密さ、レゾリューション、レジストレーションが達成されるよう、レーザアニール、エッチング技術、レーザドーピングを全て低温度で行いつつ、化学気相堆積、プラズマエンハンスト気相堆積、プリント、コーティング、及び他の堆積処理といった堆積処理を組み込むとともに組み合わせている。そのようなTFTはディスプレイ、パッケージング、ラベリング等に使用できる。  (もっと読む)

(もっと読む)

薄膜トランジスタと、その製造方法と、薄膜トランジスタを用いた電子機器

【課題】本発明は薄膜トランジスタとその製造方法と、それを用いた電子機器に関するもので、薄膜トランジスタの生産性を向上することを目的とするものである。

【解決手段】そしてこの目的を達成するために本発明は、基板1と、この基板1上に所定間隔を置いて配置した複数のソース/ドレイン電極2と、これら複数のソース/ドレイン電極2を覆うごとく前記基板1上に設けた半導体層3と、この半導体層3を覆った絶縁層4と、この絶縁層4上で、前記半導体層3のチャネル領域対応部分に設けたゲート電極6とを備え、前記ソース/ドレイン電極2上面と、前記半導体層3のチャネル領域5両側のソース/ドレイン領域8との間には、結晶化誘導金属のシリサイド層9を介在させたものである。

(もっと読む)

半導体装置および半導体装置を製造する方法

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびそれを製造する方法を提供する。

【解決手段】本発明の半導体装置は、素子分離領域と活性領域を有する半導体装置であって、活性領域とゲート酸化膜が接する第1の面より上に、ソース領域およびドレイン領域の一部が存在し、該ソース領域および/または該ドレイン領域と、該ソース領域および/または該ドレイン領域に電気的に接続される電極とが接する第2の面が、該第1の面に対して傾いている。

(もっと読む)

半導体素子及びその製造方法並びに表示装置

【課題】駆動力向上、サブスレッショルド係数低減、オフ電流低減、駆動電圧の低減等トランジスタ特性の高性能化、低消費電力化を実現する半導体素子を提供する。

【解決手段】基板101上に設けられた導電性電極103と、導電性電極103上に設けられた絶縁膜104と、絶縁膜104を介して導電性電極103上部に設けられた半導体105と、半導体105の両側に、絶縁膜104に接して設けられた導電性領域109とを備える。

(もっと読む)

液晶表示装置及び電子機器

【課題】低比抵抗を有し、且つ上記ゲッタリング工程に十分耐えうる電極構造の必要に応じ、新規な電極構造を有する液晶表示装置を提供する。

【解決手段】絶縁表面を有する基板上に、多層構造を有するゲート電極と、前記基板、前記ゲート電極の上面および側面を覆う保護膜と、前記保護膜を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜上に接して、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域の間に形成されたチャネル形成領域と、を有する半導体素子からなる半導体回路を備える。保護膜は、高温処理を施した場合、基板からの不純物の拡散を抑えることができ、基板の不純物濃度に左右されることなく、良好なTFT特性を得ることができる。

(もっと読む)

半導体素子及びこの半導体素子を用いた装置

【課題】高速な書込み及び消去動作を比較的低電圧で行い、かつ書換え劣化を抑えることで、メモリウインドウが大きく信頼性の高いメモリ素子を、低コストで提供する。

【解決手段】メモリ素子は、絶縁基板上に設けられた半導体層と、P型の導電型を有する第1の拡散層領域及び第2の拡散層領域と、第1の拡散層領域と第2の拡散層領域との間のチャネル領域を覆い、チャネル領域より電荷を注入され得る電荷蓄積膜と、電荷蓄積膜をはさんでチャネル領域とは反対側に位置するゲート電極とを有する。

(もっと読む)

半導体装置

【課題】素子の耐圧を下げることなく、半導体層の層厚を小さくする。

【解決手段】BOX層4上に積層されたN−型のSOI層5に、環状のディープトレンチ6が形成されている。ディープトレンチ6は、SOI層5の表面からBOX層4に至る深さを有している。ディープトレンチ6に取り囲まれる素子形成領域9には、P型のボディ領域10と、このボディ領域10以外の残余の領域からなるN−型のドリフト領域11とが形成されている。ボディ領域10の表層部には、N+型のソース領域12が形成されている。ドリフト領域11の表層部には、N+型のドレイン領域14が形成されている。ドリフト領域11には、SOI層5のN型不純物濃度よりも高く、かつ、ドレイン領域のN型不純物濃度よりも低いN型不純物濃度を有するN型領域15が形成されている。N型領域15の最深部は、ドレイン領域14よりも深い位置に達している。

(もっと読む)

ナノ構造電界効果型センサならびに同センサを形成する方法および使用する方法

化学的および生物学的な化学種を検出し、かつ放射線の変化を検出するソリッドステート電界効果トランジスタセンサが開示される。デバイスは、多孔性または構造化されたチャネルの区画を含むことにより、デバイス感度を向上させる。感知された生物学的、化学的または放射線の変化がチャネルのコンダクタンスの指数関数的な変化を引き起こすように、デバイスはフルデプレート型モードにおいて動作する。一実施形態において、チャネルの上に重なる誘電体層と、該誘電体層の上に重なる材料の層とをさらに備え、該材料の層は、放射性、化学的および生物学的な化学種から成るグループから検出される標的化学種と相互作用し、該材料の層は、連続的な層または離散的なアイランドのいずれかである。  (もっと読む)

(もっと読む)

フィン型トランジスタおよびその形成方法

【課題】フィン型トランジスタにおいて、半導体フィンの側面に不純物濃度が一様な不純物拡散層を形成する。

【解決手段】フィン型トランジスタは、基板上に立設された半導体のフィン10と、当該フィン10の側面に形成されたソース/ドレイン・エクステンション領域12とを備える。ソース/ドレイン・エクステンション領域10を、通常のイオン注入ではなく、クラスタ注入によって形成する。

(もっと読む)

シード印刷及びめっきによるコンタクト金属及び相互接続金属の印刷

シリサイド形成金属を含むインクを用いて、コンタクト形成方法、そのコンタクト及び局所相互接続を含むダイオード及び/又はトランジスタ等の電気デバイスとその形成方法に関する。コンタクト形成方法は、露出したシリコン表面上にシリサイド形成金属インクを堆積させるステップと、インクを乾燥させ、シリサイド形成金属前駆体を形成するステップと、シリサイド形成金属前駆体及びシリコン表面を加熱して、金属スイサイドコンタクトを形成するステップとを含む。任意選択的に、露出したシリコン表面に隣接する誘電体層上に、金属前駆体インクを選択的に堆積させて、金属含有相互接続を形成できる。更に、1つ又は複数のバルク導電性金属を、残りの金属前駆体インク及び/又は誘電体層上に堆積させてもよい。かかる印刷したコンタクト及び/又は局所相互接続を用いて、ダイオード及びトランジスタ等を作製できる。 (もっと読む)

半導体装置の製造方法および半導体装置

【課題】CMIS構造の半導体装置において、n型およびp型MISEFETの界面抵抗を低減する半導体装置の製造方法および半導体装置を提供する。

【解決手段】第1の半導体領域上にn型MISFETのゲート絶縁膜およびゲート電極を形成し、第2の半導体領域上にp型MISFETのゲート絶縁膜およびゲート電極を形成し、第1の半導体領域にAsをイオン注入して、n型拡散層を形成し、第1の半導体領域上にNiを含む第1の金属を堆積した後、第1の熱処理によって第1のシリサイド層を形成し、第1のシリサイド層上および第2の半導体領域上に、Niを含む第2の金属を堆積した後、第2の熱処理によって、第1のシリサイド層を厚膜化するとともに、第2のシリサイド層を形成し、第2のシリサイド層にBまたはMgをイオン注入した後、第3の熱処理を加えることを特徴とする半導体装置の製造方法および半導体装置。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】真空プロセスの工程数を減らし、薄膜トランジスタの製造コストを低減させる。。

【解決手段】非晶質シリコン薄膜13の上に絶縁保護膜14を形成したのち、n型不純物を含む非結晶シリコン膜15を形成する。ウェットエッチングにより非結晶シリコン膜15の絶縁保護膜14上に開口15Cを形成し、非結晶シリコン膜15をソース領域15A側と、ドレイン領域15B側に分離する。続いて、シリコン(Si)を触媒とした無電解めっきプロセスにより、非結晶シリコン膜15上に金属層、例えばクロム(Cr)膜を形成する。真空プロセスを用いることなく、常圧でソース電極16,ドレイン電極17および配線を形成することができる。

(もっと読む)

アクティブマトリクス表示装置及びその製造方法

【課題】製造工程数を削減すると共に生産性を向上させる。

【解決手段】TFTアレイ基板11は、絶縁基板21を備えている。絶縁基板21上には、一部にポリシリコン層22が形成されている。このポリシリコン層22は、TFT素子14を構成する、チャネル領域22a、ソース領域22b及びドレイン領域22cを有している。ポリシリコン層22上には、ソース領域22b及びドレイン領域22cのそれぞれ一部を覆うように配線層23が形成されている。配線層23並びに配線層23が積層されていないポリシリコン層22には、両者の表面を覆うようにゲート絶縁膜24が形成されている。ゲート絶縁膜24上には、ゲート絶縁膜24を介してチャネル領域22aに対向する位置にゲート電極層25が形成されている。ゲート絶縁膜24表面の一部には、キャパシタ上部電極層26が形成されている。

(もっと読む)

絶縁膜の改質方法および半導体装置の製造方法

【課題】大掛かりな装置を必要とすることなく、低温プロセスで絶縁膜の結晶欠陥を低減可能な半導体装置の製造方法を提供する。

【解決手段】基板11上に半導体層13、ゲート絶縁膜14およびゲート電極15をこの順に積層してトップゲート型の薄膜トランジスタを製造する。この際、塗布法により、ゲート絶縁膜14を形成したのち、エネルギービームEを照射する。これにより、半導体層13がエネルギービームEを吸収し、ゲート絶縁膜14が加熱される。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁性構造物の下部でイオンの衝突によって発生する電子とホールの量を減少させて半導体装置の破壊電圧を増加させることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、第1不純物濃度を有する第1水平部及び第1不純物濃度より大きい第2不純物濃度を有する第2水平部を具備するドリフト領域、ドリフト領域上及び第1及び第2水平部間の境界上部に形成された絶縁性構造物、第1水平部の露出した部分上に形成されたゲート絶縁膜パターン、ゲート絶縁膜パターン及び絶縁性構造物の一部上に形成されたゲート電極、ドリフト領域の第1水平部に向かうように配置されるソース、ドリフト領域の第2水平部に向かうように配置されるドレイン、及びドレインに向かう第2水平部に形成されドリフト領域の一部で形成される追加N型ドリフト部を有する。

(もっと読む)

高耐圧半導体装置

【課題】オフ動作時における耐圧を低下させることなくオン動作時における素子抵抗を低減する。

【解決手段】p型半導体基板1の主表面上にはn-層2が形成される。このn-層2の表面にはp-拡散領域5が形成される。このp-拡散領域5の一方の端部に連なるようにp拡散領域6が形成される。p-拡散領域5内には、このp-拡散領域5よりも高濃度のp型の不純物を含むp拡散領域20が複数個形成される。p-拡散領域5と間隔をあけてp拡散領域3が形成される。このp拡散領域3とp-拡散領域5の間に位置するn-層2の表面上に酸化膜10を介在してゲート電極9が形成される。p拡散領域6の表面と接触してドレイン電極12が形成される。また、p拡散領域3と隣接してn拡散領域4が形成され、このn拡散領域4とp拡散領域3との双方の表面に接触してソース電極11が形成される。

(もっと読む)

高耐圧半導体装置

【課題】オフ動作時における耐圧を低下させることなくオン動作時における素子抵抗を低減する。

【解決手段】p型半導体基板1の主表面上にはn-層2が形成される。このn-層2の表面にはp-拡散領域5が形成される。このp-拡散領域5の一方の端部に連なるようにp拡散領域6が形成される。p-拡散領域5内には、このp-拡散領域5よりも高濃度のp型の不純物を含むp拡散領域20が複数個形成される。p-拡散領域5と間隔をあけてp拡散領域3が形成される。このp拡散領域3とp-拡散領域5の間に位置するn-層2の表面上に酸化膜10を介在してゲート電極9が形成される。p拡散領域6の表面と接触してドレイン電極12が形成される。また、p拡散領域3と隣接してn拡散領域4が形成され、このn拡散領域4とp拡散領域3との双方の表面に接触してソース電極11が形成される。

(もっと読む)

41 - 60 / 107

[ Back to top ]