Fターム[5F110HK05]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 金属 (18,241) | シリサイド (1,278)

Fターム[5F110HK05]に分類される特許

161 - 180 / 1,278

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

半導体素子

【課題】垂直に形成されたナノワイヤを構成要素として備える半導体素子の寄生容量増加を抑制し、動作速度時定数が改善される半導体素子を提供する。

【解決手段】導電性基板101の主平面と電極109間の層間絶縁膜を膜厚調整層102と保護絶縁層103の2層化することにより、膜密着性の乏しい低誘電率膜102と電極109を保護絶縁層103で隔てることによってはがれを抑制しながら、主平面101と電極109間を電気的に接続するナノワイヤ107と、導電性基板101と電極109の間の寄生容量を低減する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

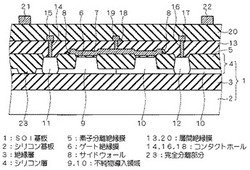

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体基板に付着する異物の影響を低減し、歩留まりよく半導体基板を作製することを目的の一とする。安定な特性を有する半導体装置を歩留まりよく作製することを目的の一とする。

【解決手段】半導体基板の作製工程において、単結晶半導体基板に脆化領域を形成する際、単結晶半導体基板表面に対して複数の(少なくとも二つ以上の)異なる角度で斜め方向から水素イオンを照射することによって、単結晶半導体基板に付着する異物の影響を低減し、均一な単結晶半導体層を有する半導体基板を歩留まりよく作製することができる。

(もっと読む)

SOI基板の作製方法

【課題】半導体層が効率良く平坦化されたSOI基板を提供することを課題の一とする。また、当該SOI基板を用いた半導体装置を提供することを課題の一とする。

【解決手段】ボンド基板に加速されたイオンを照射して該ボンド基板に脆化領域を形成し、ボンド基板またはベース基板の表面に絶縁層を形成し、絶縁層を介してボンド基板とベース基板を貼り合わせ、熱処理により、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成し、半導体層の表面と、該半導体層と同じ半導体材料でなる半導体ターゲットとが対向するように配置し、半導体層の表面と半導体ターゲットとに、交互に希ガスイオンを照射することで、半導体層の表面の平坦化を図るSOI基板の作製方法である。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極(またはドレイン電極)と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタとして、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミスを防ぐことが可能である。

(もっと読む)

半導体装置の作製方法

【課題】動作性能および信頼性の高い半導体装置の提供を課題とする。

【解決手段】シリコン基板上に設けられた酸化シリコン膜と、単結晶シリコン基板の一部

よりなりTFTの活性層となる単結晶の島状シリコン層となる前の単結晶シリコン基板を

熱酸化して得られ、酸化シリコン膜に貼り合わせ界面にて貼り合わせて設けられた膜厚が

0.05μm〜0.5μmの酸化シリコン膜と、活性層を熱酸化して設けられた他の面の

酸化シリコン膜と、により取り囲まれた活性層と、活性層上に設けられたゲート電極と、

を有し、単結晶の島状シリコン層は、膜厚が0.05μm〜0.5μmの酸化シリコン膜

を介して水素が導入された単結晶シリコン基板を水素が導入された部分で分断して得られ

たものである半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、半導体装置の各メモリセルを構成する、酸化物半導体を用いたトランジスタを直列に接続することにより、隣り合うメモリセルにおいて、酸化物半導体を用いたトランジスタのソース電極またはドレイン電極をお互いに接続させることができ、メモリセルの占有面積を低減することができる。

(もっと読む)

半導体装置

【課題】高集積なCMOS型SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体137と第1の第2導電型半導体104との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、第1の第1導電型半導体137の上下に配置された第1の第2導電型高濃度半導体182と、第2の第2導電型高濃度半導体141と、第1の第2導電型半導体104の上下に配置された第1の第1導電型高濃度半導体186と、第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート導電体167と、を有するインバータを用いてSRAMを構成する。

(もっと読む)

半導体装置の作製方法及び電気光学装置

【課題】TFTに適したSOI基板およびその作製方法を提供する。またSOI基板を用

いて信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】SIMOX、ELTRAN、Smart−Cutに代表される技術を用いて

SOI基板を作製するにあたって、主表面(結晶面)が{110}面である単結晶半導体

基板を用いる。その様なSOI基板は下地となる埋め込み絶縁層と単結晶シリコン層との

密着性が高く、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

ナノワイヤトランジスタ及びその製造方法

【課題】過度な酸化により生じるナノワイヤの断線を防止できるナノワイヤトランジスタ及びその製造方法を提案する。

【解決手段】配線形成シリコン層4を酸化させて極めて細いナノワイヤ11を形成する際、シリコン窒化膜20を配線形成シリコン層4の上部となるシリコン酸化薄膜23に予め形成しておき、シリコン窒化膜20によって配線形成シリコン層4の酸化を抑制させつつ、ソース電極形成部12とドレイン電極形成部13とナノワイヤ11とを配線形成シリコン層4に形成するようにした。このように、配線形成シリコン層4が過度に酸化されることをシリコン窒化膜20により抑制させることで、所望の領域のみ酸化させることができ、かくして、過度に酸化されることにより生じるナノワイヤ11の断線を防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】TFT回路を備える半導体装置において、歩留まりの低下を抑制可能な半導体装置及び半導体装置の製造方法を提供することを目的とする。

【解決手段】ロジック回路10上に形成された層間絶縁膜22と、層間絶縁膜22上に形成され、上部から所定の高さまでシリサイド化されたシリサイド層30を含むアモルファスシリコン層23と、アモルファスシリコン層23上に形成されたTFTと、層間絶縁膜22を貫通する貫通孔24を埋め込むように形成され、ロジック回路10に電気的に接続すると共に、上部がシリサイド層30に接続するコンタクトプラグ25とを備える。

(もっと読む)

半導体装置およびそれを用いた半導体集積回路

【課題】バックゲートを有するMOSを、回路の動作特性に応じて使い分け、幅広い温度範囲にて高速かつ低電力なLSIを実現する。

【解決手段】薄膜埋め込み酸化膜層を持つFD−SOIを使用し、薄膜埋め込み酸化膜層の下層半導体領域をバックゲートとし、論理回路ブロックにおいてブロック中の負荷の軽い論理回路にはバックゲートの電圧をブロック活性化に合わせてブロック外から制御する。このバックゲート駆動信号を発生する回路、及び回路ブロック出力部など負荷の重い論理回路には、ゲートとバックゲートとを接続したトランジスタを用い、そのゲート入力信号でバックゲートを直接制御する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さ(RMS)が1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、または絶縁層表面の一部とドレイン電極表面との高低差は、5nm未満の半導体装置である。

(もっと読む)

ナノワイヤトランジスタ及びその製造方法

【課題】動作不良や動作速度の低下の発生を従来よりも抑制できるナノワイヤトランジスタ及びその製造方法を提案する。

【解決手段】窒素が導入されたニッケルからなるニッケル層28をナノワイヤ5の周辺に形成して熱処理することにより、ナノワイヤ5に形成されたソース15及びドレイン16をシリサイド化させつつ、窒素によりゲート電極被覆領域ER1までシリサイド化されることを抑制できることから、従来よりもゲート電極被覆領域ER1にチャネル17を確保でき、かくして動作不良や動作速度の低下の発生を従来よりも抑制できる。

(もっと読む)

161 - 180 / 1,278

[ Back to top ]