Fターム[5F110HK05]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 金属 (18,241) | シリサイド (1,278)

Fターム[5F110HK05]に分類される特許

1,261 - 1,278 / 1,278

二重ゲートトランジスタ半導体製造プロセス用の限定スペーサ

半導体製造プロセスは、基板上にシリコンフィンを形成することを含む。フィンの主面上にはゲート誘電体が形成される。フィンの少なくとも2つの面の上にゲート電極が形成される。次いで、ゲート電極の側壁に近接して誘電体スペーサが選択的に形成されて、誘電体スペーサが該側壁に限定されることによって、主フィン面の大部分が露出したままとされる。その後、主フィン面上にシリサイドが形成される。一実施形態では、ゲート電極の形成は、フィンおよび基板の上にポリシリコンを堆積し、ポリシリコンの上にキャッピング層を堆積し、キャッピング層の上にフォトレジストをパターニングし、パターニングしたフォトレジストが適所に配された状態でキャッピング層およびポリシリコンをエッチングすることを含む。エッチングによりポリシリコンの幅はキャッピング層の幅よりも小さくなり、ポリシリコンの側壁に隣接するキャッピング層の下に空隙ができ、ここに限定スペーサを形成することができる。  (もっと読む)

(もっと読む)

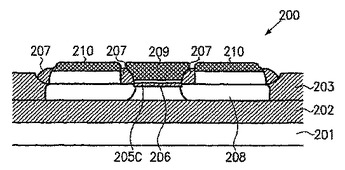

高さが異なる隆起したドレインおよびソース領域を有するトランジスタを形成するための先進技術

極めて小型の半導体デバイスにおけるエピタキシャル成長させた半導体領域の高さは、2つ以上のエピタキシャル成長を実行しうる異なるデバイス領域に対して、個別に調節することができる。エピタキシャル成長マスクは、特定のデバイス領域における半導体領域の形成を選択的に抑制する。他の実施形態において、2つ以上の異なるデバイス領域に対して、一般的なエピタキシャル成長プロセスを用いてもよく、選択されたエリアにあるすでにエピタキシャル成長させた半導体領域の高さを正確に低減するように、引き続き、選択されたデバイス領域に選択的酸化プロセスを実行することができる。  (もっと読む)

(もっと読む)

高性能の歪みCMOSデバイス

【課題】 デバイス内の酸化に起因する圧縮応力を防止するために界面に覆い被さる浅いトレンチ分離領域(STI)を有する相補型金属酸化物半導体(CMOS)デバイスを提供すること。

【解決手段】 この半導体デバイス及び製造方法は、電流の流れの方向に平行な方向及び電流の流れに対し横方向に、Si−SiO2界面に覆い被さる張出し部を備えた浅いトレンチ分離領域を有するn型チャネル電界効果トランジスタ(n型FET)を提供する。また、このデバイス及び方法は、電流の流れに対し横方向に、Si−SiO2界面に覆い被さる張出し部を備えた浅いトレンチ分離領域を有するp型チャネル電界効果トランジスタ(p型FET)を提供する。しかしながら、p型FETの浅いトレンチ分離領域は、電流の流れの方向に平行な方向には張出し部を備えない。

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

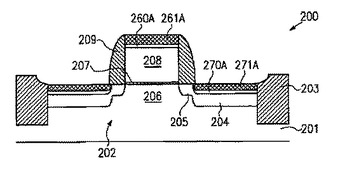

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

格子不整合エピタキシャル拡張領域ならびにソースおよびドレイン領域を有するひずみチャネルCMOSトランジスタ構造体およびその製造方法

【課題】n型電界効果トランジスタ(NFET)およびp型電界効果トランジスタ(PFET)がそれぞれ、第1の半導体の単結晶層内に配置されたチャネル領域を有し、PFETのチャネル領域には第1の大きさの応力が加えられているが、NFETのチャネル領域にはその大きさの応力が加えられていない構造体およびその製造方法を提供すること。

【解決手段】この応力は、第1の半導体とは格子不整合の第2の半導体の層によって加えられる。この第2の半導体の層は、PFETのソースおよびドレイン領域ならびに拡張領域の上の、PFETのチャネル領域から第1の距離のところに形成されており、この第2の半導体の層は、NFETのソースおよびドレイン領域の上の、NFETのチャネル領域からより大きな第2の距離のところにも形成されており、またはNFETには全く形成されていない。

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

減少されたゲート高さを有するトランジスタを製造する方法

【課題】減少されたゲート高さを有する集積回路トランジスタを形成する方法およびシステムを開示すること。

【解決手段】本方法は、基板、基板の上のゲート導体(13)、およびゲート導体(13)の上の少なくとも1つの犠牲層(14〜16)を有する積層構造を形成する。このプロセスは、積層構造を基板から延びる少なくとも1つのゲート・スタックにパターン形成し、ゲート・スタックに隣接してスペーサ(60)を形成し、ゲート・スタックに隣接してソースおよびドレイン領域(71)を形成するようにスペーサで保護されていない基板の領域にドーピングし、そして、スペーサ(60)および犠牲層(14〜16)を除去する。

(もっと読む)

ゲートの枯渇を低減した注入ゲート電極を有する電界効果型トランジスタ、及び、このトランジスタを製造する方法

ドレイン領域及びソース領域(208)を規定する前に、注入マスク(220)を形成することにより、ゲートドーパント密度をドレインドーパント密度及びゲートドーパント密度から効果的に分離する。さらに、注入マスク(220)を除去した後に、ゲート電極(205)の横方向寸法は、十分に確立された側壁スペーサ(207)技術によって規定される。その結果、フォトリソグラフィ及び異方性エッチングに基づく従来の方法に対してデバイスの縮小に関する優位性を提供する。  (もっと読む)

(もっと読む)

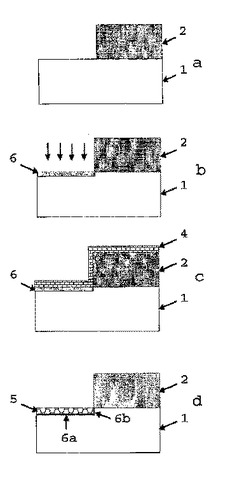

接点の製作方法とその接点を持つ電子部品

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

半導体基板におけるドーパントの拡散を低速化する方法およびこれにより製造されたデバイス

【課題】 ひずみSi/Si1-XGeXデバイス基板において、極めて浅い接合を形成する方法およびそれによって得られる半導体構造を提供する。

【解決手段】 半導体デバイスを形成する方法(およびその結果として得られる構造)は、基板上に、ドーパントおよび少なくとも1つの種を注入するステップと、基板をアニールするステップであって、少なくとも1つの種が、基板のアニールの間のトーパントの拡散を遅らせるステップと、を含む。

(もっと読む)

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

1,261 - 1,278 / 1,278

[ Back to top ]