Fターム[5F110HK08]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961)

Fターム[5F110HK08]の下位に属するFターム

Fターム[5F110HK08]に分類される特許

201 - 220 / 618

半導体装置、この半導体装置の製造方法、前記半導体装置を備えた画素アレイ基板、前記半導体装置を備えたセンシング素子アレイ基板、表示パネル、インプットパネル、表示装置、携帯機器、X線検査装置、及びレントゲン装置

【課題】曲げストレスによるオン特性の劣化を抑制できる半導体装置、この半導体装置の製造方法、前記半導体装置を備えた画素アレイ基板、前記半導体装置を備えたセンシング素子アレイ基板、表示パネル、インプットパネル、表示装置、携帯機器、X線検査装置、及びレントゲン装置を提供する。

【解決手段】単結晶膜または多結晶膜からなる結晶化領域であるチャネル領域14と、アモルファス膜からなるアモルファス領域であるソース領域24及びドレイン領域34とからなる半導体層4を備えており、チャネル領域14は、半導体層4となるアモルファス膜を形成し、アモルファス膜に電流を流して一部分を結晶化することにより形成されてなる。

(もっと読む)

酸化物薄膜トランジスタ及びその製造方法

【課題】素子の劣化及び均一度の低下を防止する酸化物薄膜トランジスタ及びその製造方法を提供する。

【解決手段】酸化物薄膜トランジスタの製造方法は、基板110上にゲート電極121を形成する段階と、基板110上にゲート絶縁膜115を形成する段階と、ゲート絶縁膜115上にチャネル領域の側面にテーパを有する1次アクティブ層124aを形成し、1次アクティブ層124a上にソース/ドレイン電極を形成する段階と、ソース/ドレイン電極122、123の上部に、非晶質酸化亜鉛系半導体からなる2次アクティブ層124bを、1次アクティブ層124aのテーパと接触するように形成する段階とを含み、1次アクティブ層124aは、ソース/ドレイン電極122、123のウェットエッチング中に低い選択比でエッチングされることにより、側面にテーパが形成される。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層にダメージを与えず、また、オフ電流の小さい薄膜トランジスタを提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の手前側にソース電極又はドレイン電極が形成されてなるボトムゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、裏面照射によって紫外線の照射された半導体層部分を高導電率化するものであるため、半導体層へのダメージが生じないため信頼性が向上する。また、ソース電極又はドレイン電極によって紫外線が遮光された半導体層の領域は照射前の導電率と同じとなるため、オフ電流の値を小さくすることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】In、Gaなどのレアメタルを含まず、Znを含む酸化物層を用いたトランジスタを提供し、Znを含む酸化物層を用いたトランジスタにおいて、オフ電流を低減し、電気特性を安定させることを課題の一とする。

【解決手段】Znを含む酸化物層を用いたトランジスタにおいて、酸化物層の上に絶縁性酸化物を含む酸化物半導体層を積層し、酸化物層とソース電極層又はドレイン電極層とが絶縁性酸化物を含む酸化物半導体層を介して接触するようにトランジスタを形成することによって、トランジスタのしきい値電圧のばらつきを低減し、電気特性を安定させることができる。

(もっと読む)

複数の閾値電圧を有するナノワイヤ・メッシュFET及びその製造方法

【課題】 調整可能な複数の閾値電圧(Vt)を有する、ナノワイヤ・ベースのFET、及びこれを製造する方法を提供する。

【解決手段】 ナノワイヤ・ベースの電界効果トランジスタ(FET)及びその製造のための技術が提供される。一態様において、各々がソース領域、ドレイン領域、及びソース領域とドレイン領域を接続する複数のナノワイヤ・チャネルを有する、スタック状に垂直方向に配向された複数のデバイス層であって、デバイス層の1つ又は複数は、デバイス層の他の1つ又は複数とは異なる閾値電圧を有するように構成される、複数のデバイス層と、ナノワイヤ・チャネルを取り囲むデバイス層の各々に共通のゲートとを有するFETが提供される。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供する。

【解決手段】基板301上にゲート電極303を形成し、ゲート電極303を覆ってゲート絶縁膜304を形成し、ゲート絶縁膜304上に酸化物半導体膜305を形成し、酸化物半導体膜305上に第1の導電膜306及び第2の導電膜307を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも加熱処理LRTAにより結晶化した領域308を有する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いた好適な構造のnチャネル型トランジスタおよびpチャネル型トランジスタを提供することを目的の一とする。

【解決手段】第1の酸化物半導体層と電気的に接続し、第1の材料を含む第1の導電層と第2の材料を含む第2の導電層の積層構造でなる第1のソース電極またはドレイン電極と、第2の酸化物半導体層と電気的に接続し、第1の材料を含む第3の導電層と第2の材料を含む第4の導電層の積層構造でなる第2のソース電極またはドレイン電極と、を有し、第1の酸化物半導体層には、第1のソース電極またはドレイン電極の第1の導電層が接触し、第2の酸化物半導体層には、第2のソース電極またはドレイン電極の第3の導電層および第4の導電層が接触する。

(もっと読む)

半導体装置の作製方法

【課題】 レジスト材料の利用効率を向上させて、作製コストの削減を目的としたレジス

トパターンの作製方法、レジストパターンの除去方法、半導体装置の作製方法を提供する

ことを課題とする。

【解決手段】 本発明は、減圧下で、被加工物上に、感光剤を含む組成物を吐出してレジ

ストパターンを形成するステップを有することを特徴とする。また、前記レジストパター

ンをマスクとして前記被加工物をエッチングするステップ、若しくは、前記レジストパタ

ーンに、フォトマスクを介して前記感光剤の感光波長域の光を照射するステップ、前記レ

ジストパターンをマスクとして前記被加工物をエッチングするステップ、前記被加工物上

の前記レジストパターンを除去するステップを有することを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板と、前記基板上に形成されたバッファ層と、前記バッファ層上に形成された高抵抗層又は下地層と、前記高抵抗層又は下地層上に形成された、炭素を含有するキャリア濃度制御層と、前記キャリア濃度制御層上に形成されたキャリア走行層と、前記キャリア走行層上に形成された、前記キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層と、前記キャリア供給層から所定の深さに到るまで形成されたリセス部と、前記キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記キャリア供給層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備える。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

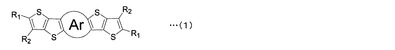

ジチエノナフトジチオフェン誘導体とこれを用いた有機電子デバイス、有機薄膜トランジスタ及びディスプレイ装置

【課題】熱安定性、電荷移動性、電流On/Off比の良好な縮合多環材料と、これを用いた有機電子デバイス、有機薄膜トランジスタ及びディスプレイ装置を提供する。

【解決手段】下記一般式(1)[式(1)中、R1及びR2は水素原子、ハロゲン原子、置換若しくは無置換のアルキル基又はアルコシキ基若しくはチオアルコキシ基から選択される基を示す。Arはナフタレン環を示す。]で表される新規なジチエノナフトジチオフェン誘導体を用いて、有機電子デバイス(例えば、前記誘導体を主成分とする有機半導体層(1)を備えた有機薄膜トランジスタ)を構成する。 (もっと読む)

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

半導体装置およびその作製方法

【課題】薄膜トランジスタの製造工程における不特定な要因によって、しきい値電圧がマイナス側、或いはプラス側にシフトすることがある。0Vからシフトする値が大きい場合には、駆動電圧の増大を招き、結果として半導体装置の消費電力を増加させてしまう。

【解決手段】酸化物半導体層を覆う第1の保護絶縁膜として平坦性のよい樹脂層を形成した後、樹脂層上に第2の保護絶縁膜としてスパッタ法またはプラズマCVD法を用いて低パワー条件で成膜される第2の保護絶縁膜を形成する。さらに、しきい値電圧を所望の値に制御するため、酸化物半導体層の上下にゲート電極を設ける。

(もっと読む)

半導体装置、表示装置、及び電子機器

【課題】実動作の阻害を低減し、ノイズによる影響を低減する。

【解決手段】電極と、電極に電気的に接続された配線と、平面視において前記電極と重なる酸化物半導体層と、断面視において前記電極と前記酸化物半導体層の間に設けられた絶縁層と、前記配線を介して前記電極から信号が入力され、入力された前記信号に応じて動作が制御される機能回路と、を有する構造であり、酸化物半導体層及び絶縁層と、配線又は電極と、を用いて容量素子を構成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】絶縁表面上にゲート電極と、酸化シリコンを含む酸化物半導体層と、ゲート電極と酸化物半導体層の間に絶縁層と、酸化シリコンを含む酸化物半導体層とソース電極層またはドレイン電極層との間にソース領域またはドレイン領域とを有し、ソース領域またはドレイン領域は、縮退した酸化物半導体材料または酸窒化物材料を用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜BOX−SOI基板に形成される電界効果型トランジスタの信頼性および動作特性の劣化を防ぐことのできる技術を提供する。

【解決手段】薄膜BOX−SOI基板の主面上に所定の間隔で配置されたnウェルnwおよびpウェルpwが形成されており、pウェルpwに形成されたnMIS1nは、SOI層1iの主面上に所定の距離を隔てて積み上げられた半導体層に形成された一対のn型ソース・ドレイン領域2nと、一対のn型ソース・ドレイン領域2nに挟まれたゲート絶縁膜3、ゲート電極4、およびサイドウォール5とを有しており、nウェルnwとpウェルpwとの間に素子分離10を形成し、素子分離10の側端部が、n型ソース・ドレイン領域2nの側端部(BOX層1bの側壁部)よりもゲート電極4側に広がっている。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を無機絶縁膜で覆うことなく加熱処理を行って酸化物半導体層が結晶化されると、結晶化による表面凹凸などが形成され、電気特性のバラツキが発生する恐れがある。

【解決手段】酸化物半導体層成膜直後から酸化物半導体層上に接して酸化シリコンを含む無機絶縁膜を形成する直前までの間に1回も加熱処理を行わず、基板上の酸化物半導体層上に接して第2の絶縁膜を形成した後に加熱処理を行うプロセス順序とする。また、酸化シリコンを含む無機絶縁膜において、膜中に含まれる水素密度は、5×1020/cm3以上、または窒素密度は、1×1019/cm3以上とする。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

201 - 220 / 618

[ Back to top ]