Fターム[5F110HK08]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961)

Fターム[5F110HK08]の下位に属するFターム

Fターム[5F110HK08]に分類される特許

601 - 618 / 618

プレーナ型ダブルゲートトランジスタおよびその製造方法

【課題】プレーナ型自己整合ダブルゲートトランジスタを既知の簡単かつコスト効率のよい製造方法で提供する。

【解決手段】SOI基板上に活性領域を規定する工程と、上記SOI基板上に第1ゲート領域206を形成する工程と、上記活性領域の中にシリコンゲルマニウムからなるソース/ドレイン領域を形成する工程と、上記SOI基板のケイ素層からチャネル領域203を形成する工程と、上記SOI基板と、ソース/ドレイン領域と、第1ゲート領域206との上に、平面を有する層311を形成する工程と、上記の平面に酸化ケイ素413が形成されたウェハーを結合する工程と、第1ゲート領域206と向かい合う第2ゲート領域517を形成する工程とを有する。

(もっと読む)

勾配付き組み込みシリコン−ゲルマニウムのソース−ドレイン及び/又は延長部をもつ、歪みP型MOSFETの構造及びこれを製造する方法

【課題】歪みシリコンをもつP型MOSFETの構造及びこれを製造する方法を提供する。

【解決手段】P型MOSFETは、ゲート110を絶縁体で封止し、ゲルマニウム含有層を側壁105の外側に成層させ、次いで、アニーリング又は酸化により、ゲルマニウムを絶縁体上シリコン層又はバルクシリコンの中に拡散させて、勾配付き組み込みシリコン−ゲルマニウムのソース−ドレイン40及び/又は延長部(geSiGe−SDE)を形成する。SOIデバイスにおいては、geSiGe−SDEは、水平方向の(ゲート誘電面に対して平行な)圧縮応力と、垂直方向の(該ゲート誘電面に対して直角の)引張り応力とをPMOSFETのチャネルに生成し、これによって、PMOSFET性能を向上させる構造を形成する。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】 チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置とその製造方法を提供すること、及び、MOSトランジスタのチャネルにおけるキャリア分布を直接測定することができる半導体装置の評価方法を提供すること。

【解決手段】 シリコン(半導体)基板10と、シリコン基板10の上に順に形成されたゲート絶縁膜13及びゲート電極14cと、ゲート電極14cの横のシリコン基板10のリセス(穴)10a、10bに形成されたソース/ドレイン材料層18a、18bと、を有し、リセス10a、10bのゲート電極14c寄りの側面10c、10dが、シリコン基板10の少なくとも一つの結晶面で構成されることを特徴とする半導体装置による。

(もっと読む)

半導体装置の製造方法

【課題】p型トランジスタの動作速度を高め、n型トランジスタとの動作速度の均衡がとれた半導体装置の製造方法を提供する。

【解決手段】p−MOS領域30aのソース/ドレイン領域にSiGe膜からなる圧縮応力印加部20を形成し、その後にp−MOS領域30aおよびn−MOS領域30bに不純物注入を行い、浅い接合領域22a、22bおよび深い接合領域23a、23bを形成する。SiGe膜を形成する際の加熱により浅い接合領域22a、22bの不純物がゲート絶縁膜15の直下に拡散することを防止し、短チャネル効果を防止すると共に、p−MOSトランジスタ13aのチャネル領域の正孔移動度を高め、n−MOSトランジスタ13bの動作速度との均衡により、相補型の半導体装置10の総合的な動作速度を高める。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】 より高精細なパターンの形成が可能な、液滴吐出法を用いた半導体装置の作製方法の提供を課題とする。

【解決手段】 パターンが形成されたモールドを絶縁膜に押し付けた状態で絶縁膜の硬化を行なった後、モールドを取り外すことで、絶縁膜に凹部を形成し、導電材料を有する液滴を吐出することにより、凹部に導電膜を形成し、導電膜を覆うようにゲート絶縁膜を形成し、ゲート絶縁膜上に島状の半導体膜を形成することを特徴とする半導体装置の作製方法。

(もっと読む)

膜形成方法、半導体膜、及び積層絶縁膜

【課題】 基板にダメージを与えることなく酸化亜鉛等の膜を形成することができる膜形成方法等を提供する。

【解決手段】 成膜室124内で、対向して配置され、少なくともその一方が高純度の亜鉛からなる一組のターゲットA,Bに、DC電圧を印加し、両ターゲットA,B間に発生させたプラズマによりスパッタリングする。スパッタリングされたターゲットA,BのZn粒子を、酸素ガスと反応させつつ、対向するターゲットの軸方向からずらされて配置された基板上に堆積し、該基板表面にZnO膜を形成する。

(もっと読む)

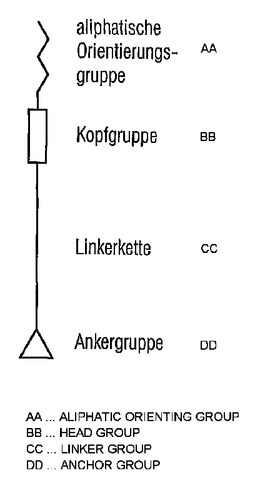

超薄膜誘電体、および、有機電界効果トランジスタでの超薄膜誘電体の使用

本発明は、基板、ソース電極、ドレイン電極、ゲート電極、および有機半導体材料を含む有機電界効果トランジスタに関するものである。このとき、誘電体層(ゲート誘電体)が、ゲート電極と半導体材料との間に配置されている。上記誘電体層は、アンカー基、リンカー基、頭部基、および脂肪族基を含んだ有機化合物の自己組織化単分子層からなる。アンカー基、リンカー基、頭部基、および脂肪族基は、この順にて互いに結合されている。  (もっと読む)

(もっと読む)

マルチゲート構造の半導体素子及びその製造方法

本発明は、複数のスラブを含むメサ型活性領域を有する半導体素子及びその製造方法を提供する。相互連結されている第1活性領域及び第2活性領域を備え、第1活性領域は基板上にライン・アンド・スペースパターン状に形成され、相互逆方向である第1側面、第2側面及び上面をそれぞれ有する複数のスラブから構成され、第2活性領域は第1活性領域とは同じであるか、または異なる物質からなり、複数のスラブを相互連結させるように、基板上でスラブの少なくとも一端部に接して延びている半導体素子である。該半導体素子を製造するために、まず、ライン・アンド・スペースパターン状の第1活性領域を基板上に形成した後、第2活性領域を形成する。  (もっと読む)

(もっと読む)

歪みFINFETチャネルの製造方法

例示的実施形態はFinFETチャネル構造の形成法に関する。当該方法において、絶縁層(130)上に化合物半導体層(140)を提供し、化合物半導体層(140)上にトレンチ(142)を提供し、かつ、化合物半導体層(140)上およびトレンチ(142)内に歪み半導体層(144)を提供する。該方法において、さらに、化合物半導体層(140)上から歪み半導体層(144)を除去し、その結果、トレンチ(142)内に歪み半導体層(144)を残し、化合物半導体層(140)を除去して、歪み半導体層(144)を残し、かつ、フィン形のチャネル領域(152)を形成する。  (もっと読む)

(もっと読む)

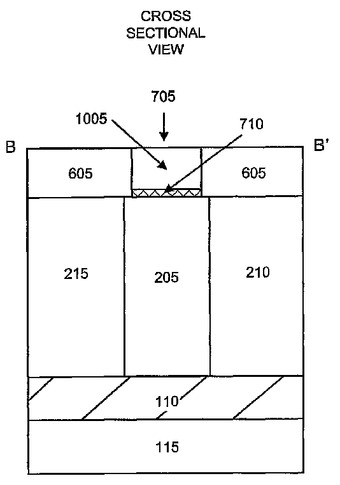

ダマシンプロセスにより形成されるトライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の第1端部に隣接するソース領域(210)、フィン(205)の第2端部に隣接するドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上にダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、絶縁層(605)中にトレンチ(705)を形成するように、ダミーゲート(505)を除去するステップと、トレンチ(705)中に金属ゲート(905)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

細型化されたボディを有する、狭いボディのダマシン・トライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の一端上にソース領域(210)、このフィン(205)の他端上にドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上に、第1パターンで、第1半導体材料のダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、第1パターンに対応する絶縁層(605)中にトレンチ(705)を残すように、第1半導体材料を除去するステップと、トレンチ(705)内に露出したフィン(205)の部分を細型化するするステップと、トレンチ(705)内に金属ゲート(1005)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

ヘテロ接合を備える半導体デバイス

ヘテロ接合を有する半導体デバイス。このデバイスは、基板と少なくとも1つのナノ構造とを備える。この基板とナノ構造とは、異なる材料から成る。この基板は、例えばIV族半導体材料から成ることがあるのに対して、このナノ構造は、III−V族半導体材料から成ることもある。このナノ構造は、この基板によって支持され、この基板とエピタキシャルな関係にある。ナノ構造は、ゲートアラウンドトランジスタデバイスなどの電子デバイスの機能コンポーネントになる可能性がある。ゲートアラウンドトランジスタの一実施形態においては、ナノワイヤ(51)が、基板(50)によって支持され、この基板はドレインであり、このナノワイヤは電流チャネルであり、上部金属コンタクト(59)はソースである。薄いゲート絶縁膜(54)が、このナノワイヤとこのゲート電極(55A、55B)とを絶縁している。  (もっと読む)

(もっと読む)

Si:CおよびSiGeエピタキシャル成長ソース/ドレインを用いた高性能で応力が向上されたMOSFETおよび製造方法

【課題】 半導体デバイスおよび半導体デバイスの製造方法を提供する。

【解決手段】 半導体デバイスはpFETおよびnFETのためのチャネルを含む。SiGe層はpFETチャネルのソースおよびドレイン領域に選択的に成長され、Si:C層はnFETチャネルのソースおよびドレイン領域に選択的に成長される。SiGe層およびSi:C層は、下に位置するSi層の格子ネットワークに一致して応力成分を生成する。1つの実施形態では、これによって、pFETチャネルでは圧縮成分が引き起こされ、nFETでは引張成分が引き起こされる。

(もっと読む)

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

分離領域を有する半導体デバイスを形成するための方法

分離構造を有する半導体デバイス(10)を形成するための方法が漏れ電流を低減する。チャネル分離構造(32、30、34)がチャネル構造の中の漏れ電流を低減する。さらに、電流電極領域の下に電流電極誘電体分離構造(36)が形成され、電流電極(40)間の漏れを防ぐ。  (もっと読む)

(もっと読む)

弱く結合した層からなる無機半導体を用いた電界効果トランジスタ

電界効果トランジスタは、ソース電極と、ドレイン電極と、ゲート電極と、無機半導体の結晶または多結晶の層と、誘電体層とを含む。無機半導体の層は、物理的にソース電極からドレイン電極まで延びる活性チャネル部分を有する。無機半導体は、層内の結合力が共有結合および/またはイオン結合である2次元の層の積み重ねを有する。互いに隣接する層のそれぞれが、共有結合およびイオン結合の力よりかなり弱い力によって互いに結合される。誘電体層は、ゲート電極と無機半導体材料の層の間に介在する。ゲート電極は、無機半導体の層の活性チャネル部分の導電率を制御するように構成される。

(もっと読む)

(もっと読む)

減少されたゲート高さを有するトランジスタを製造する方法

【課題】減少されたゲート高さを有する集積回路トランジスタを形成する方法およびシステムを開示すること。

【解決手段】本方法は、基板、基板の上のゲート導体(13)、およびゲート導体(13)の上の少なくとも1つの犠牲層(14〜16)を有する積層構造を形成する。このプロセスは、積層構造を基板から延びる少なくとも1つのゲート・スタックにパターン形成し、ゲート・スタックに隣接してスペーサ(60)を形成し、ゲート・スタックに隣接してソースおよびドレイン領域(71)を形成するようにスペーサで保護されていない基板の領域にドーピングし、そして、スペーサ(60)および犠牲層(14〜16)を除去する。

(もっと読む)

601 - 618 / 618

[ Back to top ]