Fターム[5F110HK08]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961)

Fターム[5F110HK08]の下位に属するFターム

Fターム[5F110HK08]に分類される特許

141 - 160 / 618

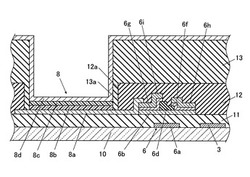

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるソース電極6i(5i)と不純物半導体膜6g(5g)の積層体の一部が、チャネル保護膜6d(5d)における膜厚の厚い一端側に重なる構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制することができ、チャネルの乱れを抑えることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

正孔注入輸送層を有するデバイス、及びその製造方法、並びに正孔注入輸送層形成用インク

【課題】製造プロセスが容易でありながら、長寿命を達成可能なデバイスを提供する。

【解決手段】基板上に対向する2つ以上の電極と、そのうちの2つの電極間に配置された正孔注入輸送層を有するデバイスであって、前記正孔注入輸送層が、遷移金属錯体の反応生成物を含有し、該遷移金属錯体の中心金属が、少なくともバナジウム、レニウム及び白金よりなる群から選択される1種以上の遷移金属を含むか、或いはバナジウム、レニウム及び白金よりなる群から選択される1種以上の遷移金属とモリブデンとの混合物であることを特徴とする、デバイスである。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるソース電極6i(5i)と不純物半導体膜6g(5g)の積層体と、ドレイン電極6h(5h)と不純物半導体膜6f(5f)の積層体が、チャネル保護膜6d(5d)に重ならない構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制するとともに、薄膜トランジスタ6(5)のチャネル長を短くすることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

電圧調整回路

【課題】トランジスタにおけるオフ電流を低減し、電圧調整回路における出力電圧の変換効率を向上させる。

【解決手段】ゲート、ソース、及びドレインを有し、ゲートがソース又はドレインに電気的に接続され、ソース及びドレインの一方に第1の信号が入力され、チャネル形成層としてキャリア濃度が5×1014/cm3以下である酸化物半導体層を有するトランジスタと、第1の電極及び第2の電極を有し、第1の電極がトランジスタのソース及びドレインの他方に電気的に接続され、第2の電極にクロック信号である第2の信号が入力される容量素子と、を有し、第1の信号の電圧を昇圧又は降圧し、昇圧又は降圧した電圧である第3の信号を出力信号としてトランジスタのソース及びドレインの他方を介して出力する構成である。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】 置換ゲート工程で発生する不良を防止できる半導体装置の製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体基板上にゲート絶縁膜および犠牲ゲート電極を含むゲートパターンを形成する段階、前記半導体基板および前記ゲートパターン上にエッチング停止層および絶縁層を形成する段階、前記エッチング停止層が露出するまで前記絶縁層を除去する段階、前記犠牲ゲート電極が露出するまで前記エッチング停止層をエッチバックする段階、前記犠牲ゲート電極を除去し、結果物の全体構造の上面に金属層を形成する段階、前記絶縁層が露出するまで前記金属層を除去する段階、および前記金属層を所定の深さでエッチバックする段階を含む。

(もっと読む)

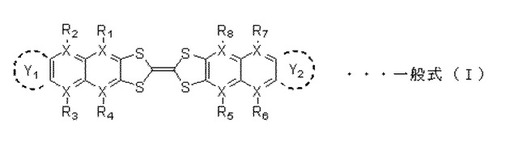

テトラチアフルバレン誘導体を用いた有機トランジスタ及びその製造方法

【課題】種々の溶媒に対して溶解性が優れ、インクジェット等の印刷法により製膜可能なTTF誘導体を用いたインクおよびそれを用いた製造方法、用途を提供する。

【解決手段】一般式(I)で表わされるテトラチアフルバレン誘導体を含む電子デバイス用インク。

(式中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり、同一でも異なっていてもよい。Xに炭素原子及び窒素原子が選択される場合において、R1〜R8は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり、同一でも異なっていてもよい。)

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能向上を図ることが可能な薄膜トランジスタを提供する。

【解決手段】ソース電極4およびドレイン電極5は、互いに離間されていると共にそれぞれ有機半導体層3の上に重なっている。有機半導体層3は、下部有機半導体層3Aの上に上部有機半導体層3Bが形成された積層構造を有している。下部有機半導体層3Aは、ソース電極4と重なる領域R1からドレイン電極5と重なる領域R2まで延在している。上部有機半導体層3Bは、領域R1,R2に互いに離間されるように配置されており、下部有機半導体層3Aよりも高い溶解性および導電性を有している。

(もっと読む)

薄膜トランジスタとその作製方法

【課題】薄膜トランジスタのオン電流を大きくする。

【解決手段】薄膜トランジスタのバックチャネル部に凸部を設ける。該凸部は、ソースまたはドレインからチャネル形成領域まで引いたバックチャネル部の接線を避けて設けられる。該凸部により電荷のトラップ箇所とオン電流の経路を遠ざけることができ、オン電流を大きくすることができる。バックチャネル部の側面の形状は曲面であってもよいし、断面において直線で表される形状であってもよい。更には、一括してエッチングを行うことでこのような形状を形成する方法を提供する。

(もっと読む)

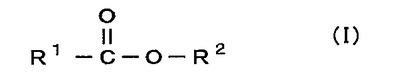

有機半導体用混合物、並びに、有機電子デバイスの作製方法及び有機電子デバイス

【課題】有機半導体として実用上十分に高移動度で、且つ安定した半導体特性を発現することができる有機半導体用混合物、並びに、有機電子デバイスの作製方法及び有機電子デバイスを提供する。

【解決手段】有機半導体材料と下記一般式(I)で表されるカルボン酸又はそのエステルを含む有機半導体用混合物、並びに、基板上に有機半導体用塗布液を塗布し乾燥させて有機半導体層を形成する有機電子デバイスの作製方法において、有機半導体用塗布液が、有機半導体材料と前記カルボン酸又はそのエステルと溶媒とを含む有機半導体用混合物である有機電子デバイスの作製方法、及び、基板上に有機半導体と前記カルボン酸又はそのエステルを含有する有機半導体層を有する有機電子デバイス。

〔式(I)中、R1及びR2はそれぞれ独立して、水素原子又は置換基を有していてもよい炭素数1〜50の脂肪族炭化水素基を示す。但し、R1とR2の各炭素数の和は5以上である。〕

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好で生産性の高い薄膜トランジスタを提供する。

【解決手段】ゲート電極を覆うゲート絶縁層と、ゲート絶縁層に接する半導体層と、半導体層の一部に接し、ソース領域及びドレイン領域を形成する不純物半導体層と、不純物半導体層に接する配線とを有し、半導体層において、ゲート絶縁層側に形成される凹凸状の微結晶半導体領域と、当該微結晶半導体領域に接する非晶質半導体領域とを有し、半導体層及び配線の間に障壁領域を有する薄膜トランジスタである。

(もっと読む)

不揮発性のラッチ回路及び論理回路及びそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】シリコン半導体の物性は解明されていることが多いが、酸化物半導体の物性は不明な点が多い。特に、不純物が酸化物半導体に及ぼす影響について未だ明らかにされていない。以上に鑑み、酸化物半導体層を用いた半導体装置の電気特性に影響を与える不純物を防止又は排除した構成を以下に開示する。

【解決手段】ゲート電極と、チャネル形成領域を有する酸化物半導体層と、前記ゲート電極と前記酸化物半導体層との間に挟まれたゲート絶縁層と、を有し、前記チャネル形成領域に含まれる窒素濃度は、1×1020atoms/cm3以下である半導体装置である。

(もっと読む)

液晶表示装置、及び当該液晶表示装置を具備する電子機器

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】酸化物半導体層に対して、窒素、または希ガス(アルゴン、ヘリウムなど)の不活性気体雰囲気下、或いは減圧下で脱水化、又は脱水素化処理のための加熱処理を行い、酸素、酸素及び窒素、又は大気(好ましくは露点−40℃以下、より好ましくは−50℃以下)雰囲気下で加酸化処理のための冷却工程を行うことで高純度化及びI型化した酸化物半導体層を形成する。該酸化物半導体層を含む薄膜トランジスタを有する半導体装置を作製する。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好な、酸化物半導体を用いた薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート電極およびゲート絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられた金属酸化物膜と、金属酸化物膜上に設けられた金属膜と、を有し、酸化物半導体膜は、金属酸化物膜と接し、且つ、酸化物半導体膜の他の領域よりも金属濃度が高い領域(金属高濃度領域)を有する。金属高濃度領域には、酸化物半導体膜に含まれる金属が、結晶粒または微結晶として存在していてもよい。

(もっと読む)

141 - 160 / 618

[ Back to top ]